# Formation of coupled triple silicon quantum dot with a compact device structure

Takafumi Uchida<sup>1</sup>, Atsushi Tsurumaki-Fukuchi<sup>1</sup>, Masashi Arita<sup>1</sup>, Akira Fujiwara<sup>2</sup>, and Yasuo Takahashi<sup>1</sup>

<sup>1</sup> Graduate School of Information Science and Technology, Hokkaido University, Sapporo, 060-0814, Japan

Phone: +81-11-706-6457 E-mail: takafumi-uchida@frontier.hokudai.ac.jp

<sup>2</sup> NTT Basic Research Laboratories, NTT Corporation, 3-1 Morinosato Wakamiya, Atsugi, 243-0198, Japan

#### Abstract

We succeeded in fabricating the compact and coupled triple quantum dots (TQDs) in Si-nanowire by splitting a single Si-nanodot into three QDs by the use of oxidization through the narrow gaps of the three fine gate electrodes attached on the nanowire. The formation of coupled TQDs was confirmed by the analysis of the change in conductive spots appeared in stability diagrams. Gate capacitances of each QD were evaluated.

## 1. Introduction

Capacitively coupled QDs systems are extensively studied for a quantum computation and a single-electron transport. Although many coupled QDs are fabricated by controlling the tunnel barriers with the many gates attached to the QDs, it is important to form compact coupled QDs for the practical application by decreasing the number of gates. We succeeded to fabricate multiple QDs by applying the pattern-dependent oxidation (PADOX) [1] of Si-nanowire and the additional oxidation through the gaps between fine gate electrodes attached on the nanowire, and observed the each QD was formed under the each gate electrode [2]. In order to increase the inter-dot capacitive coupling, the gap size between the gates should be reduced. However, this makes it difficult to confirm the formation of multiple QDs due to the complicated coupled characteristics. Here, we fabricated a compact TQDs device that has three fine gates by reducing the gap size between the gates. The formation of series TQDs was confirmed from the measured characteristics, and gate capacitances between gates and QDs were evaluated.

## 2. Experiment

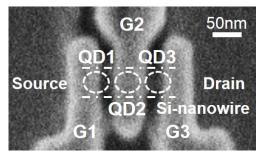

The scanning electron microscope image of three fine gate electrodes (G1, G2, and G3) on Si-nanowire is shown in Fig. 1. The 40-nm-wide and 160-nm-long Si-nanowire was formed on a SOI wafer. A single QD was first fabricated by using PADOX of the nanowire at 1000°C in dry  $O_2$ . Three 40-nm-wide fine gate electrodes made of  $n^+$  poly-silicon were attached on the nanowire with an inter-electrode gap of 40 nm. The tunnel barriers between the TQDs were formed by oxidation through the gaps between the gates at 700°C and 1000°C. The series-TQDs (QD1, QD2, and QD3) were fabricated in the nanowire just under the gate electrodes. After depositing 50-nm-thick SiO<sub>2</sub> inter-gate insulator, a top gate electrode was attached.

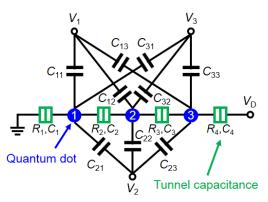

Electrical characteristics of the TQDs were investigated by applying gate voltages  $(V_1, V_2, \text{ and } V_3)$  to the three gates of G1, G2, and G3. The equivalent circuit of TQDs with three gates is shown in Fig. 2. In this experiments, all gate capacitances were evaluated from stability diagrams in which drain current peaks were shown as a function of gate voltages. Although the electron tunneling current through the TQDs was identified only when all the three QDs are resonant, the diffusion of current peaks was seen in the part of stability diagram due to the thermal energy and the strength of capacitive coupling between QDs. In order to observe the current peaks of each QD, the current peaks were diffused at the measurement temperature of about 8 K and the drain voltage of 5 mV. In addition, the splitting of current peaks due to the inter-dot capacitive coupling was excluded by the diffusion of the current peaks.

## 3. Result and Discussion

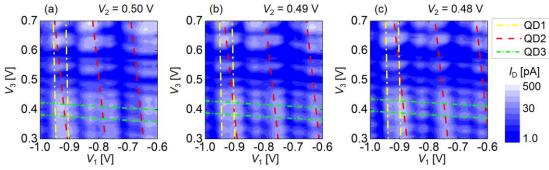

Figs. 3(a)-(c) shows contour plots of the drain current  $(I_D)$  as a function of  $V_1$  and  $V_3$  measured at constant  $V_2$  of (a) 0.50 V, (b) 0.49 V, and (a) 0.48 V, respectively. Three kinds of lines connecting the current peaks represent the boundaries of charge transition in each QD. From these results, it was observed that the charge transition lines were shifted by decreasing  $V_2$  from 0.50 V to 0.48 V. All the gate capacitances calculated from the shifts, gaps and slopes of these lines are shown in Table I. The result that  $C_{ii}$  (i=1-3) was the largest in the  $C_{ij}$  (j=1-3) indicates that the QDs were formed just under the gate.

Table I. Capacitances between each gate and QD.

|     | G1 [aF]                       | G2 [aF]                      | G3 [aF]                       |

|-----|-------------------------------|------------------------------|-------------------------------|

| QD1 | <i>C</i> <sub>11</sub> : 3.7  | <i>C</i> <sub>21</sub> : 1.4 | <i>C</i> <sub>31</sub> : 0.08 |

| QD2 | $C_{12}$ : 1.2                | C <sub>22</sub> : 1.9        | C <sub>32</sub> : 0.13        |

| QD3 | <i>C</i> <sub>13</sub> : 0.24 | $C_{23}$ : 2.5               | <i>C</i> <sub>33</sub> : 3.9  |

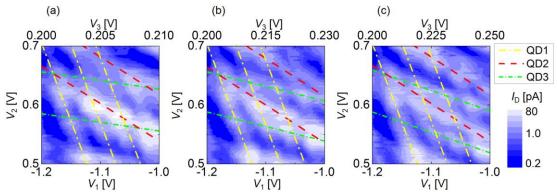

To confirm the result shown in Table I, another series of electrical measurements were performed. Figs. 4(a)-(c) show the stability diagrams as a function of  $V_1$ ,  $V_2$ , and  $V_3$ with a different range of  $V_3$ . The charge transition lines can be drawn from the conductive spots appeared within the thermal fluctuation of the current peaks. It was observed that the slopes of the charge lines ( $dV_1/dV_2$ ) were changed by the variation of  $V_3$ . When the change of the slope was large, the capacitive coupling between G3 and QD3 was strong, which means that the green lines represents the charge transition in QD3 just under G3. On the other hand, the other lines are not much changed because the gate capacitances of  $C_{31}$  and  $C_{32}$  were very small. We calculated the gate capacitances from the changes in the slopes, and consistent values of  $C_{ij}$  were obtained with the result in Table I. This result also confirmed the formation of coupled TQDs fabricated with a very compact device structure by the two measurement methods.

#### 3. Conclusion

We successfully fabricated coupled series-TQDs by the oxidation of Si-nanowire attached three fine gate electrodes. Because of the compact device size, we can achieve the inter-dot couplings between QDs, which makes the electrical characteristic of TQDs complicated. Then, we evaluated all the gate capacitances of TQDs by two measurement methods in which three gate voltages ( $V_1$ ,  $V_2$ , and  $V_3$ ), were varied independently. These measurement methods will be applicable to estimate the formation of coupled TQDs when the device size is further reduced.

#### Acknowledgements

This work was supported by KAKENGHI by MEXT and JSPS (Nos. 25420279, 26630141) and the Mitsubishi Foundation.

#### References

[1] Y. Takahashi et al., Electron. Lett., 31, (1995) 136.

[2] T. Uchida et al., J. Appl. Phys., 117, (2015) 084316.

Fig. 1. Scanning electron microscope image of fine gate electrodes on Si-nanowire. White dashed circles show TQDs configurations.

Fig. 2. Equivalent circuit of triple quantum dot with three gate electrodes.

Fig. 3. Measured stability diagrams of coupled TQDs as a function of  $V_1$  and  $V_3$  at constant  $V_2$  of (a) 0.50 V, (b) 0.49 V, and (c) 0.48 V. The broken lines represent the charge transition in each QD. The  $V_1$  coordinates of the charge transition lines are shifted along the right by decreasing. The amount of the shift for  $V_2$  change of 10 mV are  $V_1$  of 3.8 mV for QD1, 16 mV for QD2, and 100 mV for QD3, respectively.

Fig. 4. TQDs stability diagrams as a function of  $V_1$ ,  $V_2$ , and  $V_3$ .  $V_3$  is changed along with  $V_1$  in a range of (a) 0.20-0.21 V, (b) 0.20-0.23 V, and (c) 0.20-0.25 V, respectively.