# Evaluation of InAs HEMT with Non-alloyed Ohmic contacts & Mesa Sidewall Etch for RF and Low-power Logic Applications

Kai-Chun Yang<sup>1</sup>, Jing-Neng Yao<sup>2</sup>, Hisang-Hua Hsu<sup>3</sup>, Yueh-Chin Lin<sup>4</sup>, Heng-Tung Hsu<sup>5</sup>, Jer Shen Maa<sup>1</sup>, Edward Yi Chang<sup>2,4,6</sup>, H. Iwai<sup>6,7</sup>

<sup>1</sup>Institute of Photonic System, National Chiao-Tung University (NCTU).

1001 Ta Hsueh Road, Hsinchu 30010, Taiwan, R.O.C.

Phone: +886-9-2979-9186 E-mail: lbj win@hotmail.com

<sup>2</sup> Department of Electronics Engineering, National Chiao-Tung University (NCTU).

<sup>3</sup>Institute of Imaging and Biomedical Photonics, National Chiao-Tung University (NCTU).

<sup>4</sup>Department of Materials Science and Engineering, National Chiao-Tung University (NCTU).

<sup>5</sup> Department of Communications Engineering, Yuan Ze University, Chungli 320, Taiwan, R.O.C.

<sup>6</sup>International college of Semiconductor Technology, National Chiao-Tung University (NCTU).

<sup>7</sup>Interdisciplinary Graduate School of Science and Engineering, Tokyo Institute of Technology.

J2-68, 4259 Nagatsuta, Midori-ku, Yokohama 226-8502, Japan

## Abstract

An InAs HEMTs with Ti/Pt/Au non-alloyed ohmic contacts and mesa sidewall etch is successfully fabricated and evaluated for RF and low-power logic applications. The device exhibits a SS of 65.5 mV/decade with low DIBL of 22.2 mV/V and  $I_{ON}/I_{OFF}$  of 1.52  $\times$  10<sup>4</sup> at  $V_{DS} = 0.5$  V, and the off-state breakdown voltage was 6.6 V. For RF applications, the device shows a high  $f_T$  of 537 GHz and fmax of 486 GHz. These results demonstrate that mesa sidewall etch and non-an- nealed ohmic contacts can be applied to the fabrication of InAs HEMTs with excellent electrical characteristics.

## 1. Introduction

InP-based High electron mobility transistors (HEMTs) technologies are capable of providing high frequency application. However, conventional mesa isolation process causes sidewall leakage and results in increased gate leakage currents, subthreshold currents and lower breakdown voltage [1]. And using Au/Ge/Ni/Au ohmic metals could easily diffuse into adjacent semiconductor layers during annealing, which results in poor edge definition inadequate thermal stability [2]. In the previous study, researchers have acknowledged that sidewall leakage causes excessive gate leakage current, degraded breakdown voltage and non-alloyed ohmic contacts can provide good edge definition, smooth surface morphology.

In this study, a simple technique of sidewall etch and Ti/Pt/Au non-alloyed ohmic contacts was developed for RF and high speed application.

# 2. Device fabrication

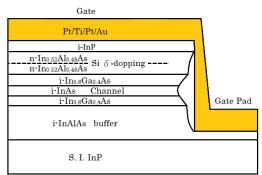

layer structure includes highly The Si-doped. In<sub>1-x</sub>Ga<sub>x</sub>As cap layers, an InP etch stop layer, In<sub>0.52</sub>Al<sub>0.48</sub>As barrier layer, a Si planar doping layer, a thin In<sub>0.52</sub>Al<sub>0.48</sub>As spacer layer, and the In<sub>0.65</sub>Ga<sub>0.35</sub>As/InAs/In<sub>0.65</sub>Ga<sub>0.35</sub>As layers to improve the electron transport properties [3][4]. The device fabrication process includes mesa isolation, ohmic metal deposition, silicon nitride passivation, gate recess, gate formation and Pt sinking process. The active area of the device was defined by wet etch using a H<sub>3</sub>PO<sub>4</sub> base solution. After mesa definition, SA base solution was used for sidewall etch as shown in Fig. 1. Then, the non-annealing ohmic metal (Ti/Pt/Au) was deposited and the source, drain spacing was 3µm. The T-shaped gate was achieved using E-beam lithography. Finally, Schottky gate metal (Pt/Ti/Pt/Au) was deposited, the device was alloyed at 90°C for Pt gate sinking. The low annealing temperature was used to avoid Pt diffusion into the channel layer owing to the thin barrier layer for the device.

Fig. 1 The cross section of mesa sidewall etch.

### 3. Results and discussions

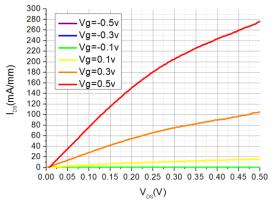

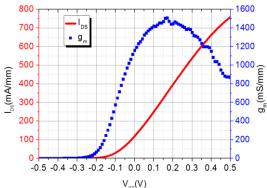

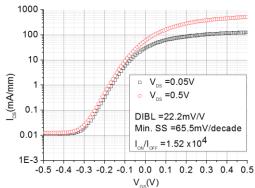

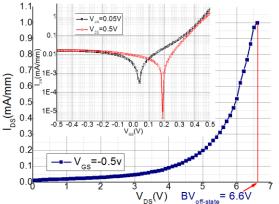

The InAs HEMTs with non-alloyed ohmic contacts and mesa sidewall etch obtains a high I<sub>ON</sub>/I<sub>OFF</sub> ratio, off-state breakdown voltage and low sub-threshold swing (SS) and drain induced barrier lowering (DIBL). Fig. 2 shows the DC characteristics of the device. It exhibits a maximum transconductance of 1508 mS/mm and the IDS of 759 mA/mm were achieved at V<sub>DS</sub>=1.0V and V<sub>GS</sub>=0.5V as shown in Fig. 3. The InAs HEMTs was evaluated for high speed logic applications. Fig. 4 shows the sub-threshold characteristics of the device [5]. In a classic planar field-effect transistor with a long channel, the threshold voltage is independent of drain voltage bias. However, DIBL is a short-channel effect in devices, which is caused by gate shrinking and referring to the reduction of threshold voltage of the transistor at higher drain voltages. Because of using the non-alloyed ohmic contacts, lower DIBL value of 22.2mV/V was achieved. Also, excellent minimum SS of 65.5 mV/decade was obtained at  $V_{DS} = 0.5 \text{ V}$ , which

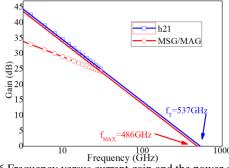

represents a fast switch transition. Besides, an  $I_{ON}/I_{OFF}$  of 1.52 x 10<sup>4</sup> was achieved. Fig. 5 shows the off-state breakdown voltage. Higher breakdown voltage of 6.6V was achieved by using sidewall etch as comparison with conventional mesa isolation [6]. Fig. 6 shows the frequency dependence of the current gain (H<sub>21</sub>) and the power gain (MAG/MSG) for the device measured at  $V_{DS} = 1.2V$ . The values of intrinsic cut-off frequency and maximum oscillation frequency were extracted by extrapolating current gain and the power gain with a -20 dB/decade slope. A high intrinsic f<sub>T</sub> of 537GHz and f<sub>max</sub> of 486GHz were obtained for the device when device was biased at  $V_{DS} = 1.0V$  and  $V_{GS} = 0.16V$ . Excellent DC and RF characteristics of the device were achieved at low applied voltage of 1.2V.

Fig. 2 DC characteristics for the InAs HEMTs with mesa sidewall etch and non-alloyed ohmic contacts. ( $I_{DS}$  versus  $V_{DS}$  curves)

Fig. 3  $I_{DS}$  and  $G_m$  versus  $V_{GS}^{(V)}$  curves at  $V_{DS} = 1V$ .

Fig. 4 Electrical characteristics (DIBL, SS, I<sub>ON</sub>/I<sub>OFF</sub> ratio)

### 4. Conclusions

In this study, InAs HEMTs Using mesa sidewall etch and non-alloyed ohmic contacts with a thin barrier layer design for logic and RF performance is demonstrated. Besides, with the Pt gate sinking process, the gate electrode becomes much closer to the channel layer, thus avoid short channel effect. The devices exhibit improved behaviors at low V<sub>DS</sub> such as better current saturation (759 mA/mm), higher maximum transconductance ( $g_{m,max}$ =1508 mS/mm). For logic applications, the device exhibited the DIBL of 22.2 mV/V, SS of 65.5 mV/decade,  $I_{ON}/I_{OFF}$  ratio > 10<sup>4</sup> and BV<sub>off-state</sub> of 6.6V. The device also shows RF performance with higher  $f_T$  (537GHz) and higher  $f_{max}$  (486GHz).

Overall, these experimental results demonstrate that InAs HEMTs with non-alloyed ohmic contacts and mesa sidewall etch has great potential for the next generation device for high-speed and low-voltage logic applications.

$v_{DS}(v) = Bv_{off-state} = 6.6V$ Fig. 5 Gate leakage and  $BV_{off-state}$  was defined at  $I_{DS}=1$ mA/mm.

Fig. 6 Frequency versus current gain and the power gain .

#### Acknowledgements

This work was sponsored by NCTU-UCB I-RiCE program, Ministry of Science and Technology, Taiwan, under Grant No. MOST104-2911-I-009-301. This work is particularly supported by "Aiming for the Top University Program" of the National Chiao Tung University and Ministry of Education, Taiwan, R.O.C

#### References

- [1] Sandeep R. Bahl, et al., IEEE TED 39, 9 (1992)

- [2] A. G. Baca, et al., Thin Solid Films 308-309, 599 (1997)

- [3] T. Enoki, K. Arai, et al., Jpn. J. Appl. Phys. 37(1998)

- [4] E. Y. Chang, et al., Jpn. J. Appl. Phys. 43, 871 (2004).

- [5] R. Chau, S. Datta et al., Proc. IEEE CSIC Dig., 17 (2005)

- [6] Chien-I Kuo, et al., IEEE IPRM, 128 (2009)