# Investigation of Conventional Bipolar Logic Technologies in 4H-SiC for Harsh Environment Applications

Hazem Elgabra<sup>1</sup>, Amna Siddiqui<sup>2</sup> and Shakti Singh<sup>3</sup>

Khalifa University of Science, Technology & Research P.O Box: 127788, Abu Dhabi, United Arab Emirates. <sup>1</sup>E-mail: <u>hazem.elgabra@kustar.ac.ae</u> <sup>2</sup>E-mail: <u>100037104@kustar.ac.ae</u> <sup>3</sup>Phone: +971-2-501-8517 E-mail: <u>shakti.singh@kustar.ac.ae</u>

# Abstract

Silicon Carbide (SiC) is a wide bandgap semiconductor capable of robust operation in extreme environments. Thus far, SiC research has been geared primarily towards developing discreet devices. These devices are controlled by silicon-based circuitry, limiting the overall efficiency of the system in such environments. For this purpose, 4H-SiC integrated circuits (ICs), based on different conventional logic technologies, have been investigated using different device structures by various research groups. This paper presents, for the first time, a thorough investigation of conventional bipolar logic technologies in 4H-SiC across a wide range of temperatures (27 °C - 500 °C) and power supply voltages (7 V -17 V). Unlike previous studies, this paper evaluates different technologies using the same device structure to highlight the true merits of each logic technology.

## 1. Introduction

Energy efficiency, high speed, small size, and low power are desired features for integrated circuits (ICs). Silicon (Si) based electronics are able to fulfill these requirements primarily at low temperatures (< 250 °C). Silicon carbide (SiC), on the other hand, can inherently handle high temperatures (~600 °C) and high radiation due to its wide bandgap, low intrinsic carrier concentration, and high thermal conductivity. All these features, in addition to its high saturation velocity, high breakdown field, and mature substrate technology makes it a suitable candidate for harsh environment applications in fields such as automotive, aerospace, nuclear, defense, etc. SiC bipolar junction transistors (BJTs) are essential for such applications as unlike metal oxide semiconductor devices, they do not have a critical oxide layer under high electric field, and hence are not prone to reliability issues at high temperatures.

Conventional bipolar logic technologies using 4H-SiC BJTs have been separately studied by different research groups (Transistor-Transistor Logic (TTL) [1], and Emitter-Coupled Logic (ECL) [2]-[3]). ECL is traditionally known to be the fastest Si bipolar technology, however, experiments have shown gate delays of ~9.8 ns and ~105 ns at room temperature for 4H-SiC based TTL and ECL technologies, respectively [1]-[2]. These anomalous results can be attributed to the different transistor designs used in each study, which calls for a thorough investigation that highlights the differences in each logic technology using the same 4H-SiC transistor design.

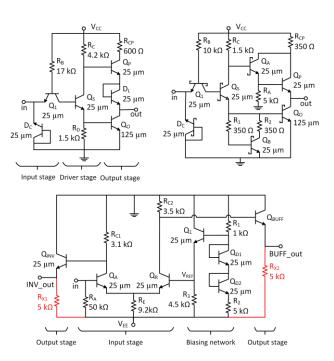

FIG. 1 Optimized circuit diagrams for TTL (top left) and STTL (top right) inverters, and ECL BUFF/INV circuit (bottom).

This paper provides a comparative study of the three most popular bipolar technologies (TTL, Schottky TTL (STTL), and ECL) with varying temperatures and power supply voltages, using the 4H-SiC BJT described in [3].

### 1. Digital Logic Technology Evaluation

The criteria used to evaluate the performance of each technology are the low and high noise margins ( $NM_L$  and  $NM_H$ ) of a fan-out of 10 inverter (FO-10), and the gate delay ( $t_g$ ) of an 11-stage ring oscillator (11-RO). An inverter based on each technology is designed and optimized for best noise margins and gate delays and is operated at varying temperatures (27 °C, 250 °C, and 500 °C) and power supply voltages (7 V-17 V). A different model set is designed for the transistor at each temperature. The change in resistivity at elevated temperatures is also taken into account for all the resistors in the circuits. Fig. 1 shows the circuit configuration for the optimized inverters in the three technologies.

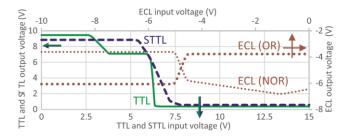

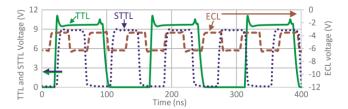

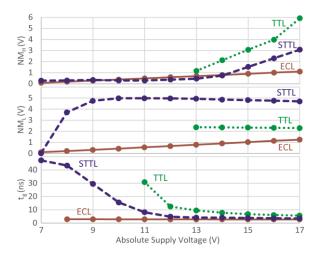

Figs. 2 and 3 display the FO-10 inverter voltage transfer characteristics and the 11-RO waveforms for each technology, respectively. Fig. 4 shows the effect of chang-

FIG. 2 Voltage transfer characteristics of optimized FO-10 inverters for TTL (solid), STTL (dashed) and ECL (dotted), where T = 27 °C and power supply voltage = |15| V.

FIG. 3 Waveforms of 11-stage ring oscillator for optimized ECL (dashed), TTL (solid), and STTL (dotted) circuits, where T = 27 °C and power supply voltage = |15| V.

FIG. 4  $NM_H$  (top),  $NM_L$  (middle) values for optimized FO-10 inverters, and  $t_g$  (bottom) values for 11-stage ring oscillator for optimized ECL (solid), TTL (dotted) and STTL (dashed) circuits, at different supply voltages, where T = 27 °C.

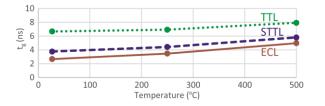

FIG. 5 11-stage ring oscillator gate delays for optimized ECL (solid), TTL (dotted) and STTL (dashed) at different temperatures, where supply voltage = |15| V.

ing power supply voltages on the noise margins and gate delays for the technologies under investigation. Out of all technologies, ECL shows the most stable operation under these conditions. The STTL circuit shows significant perfo-

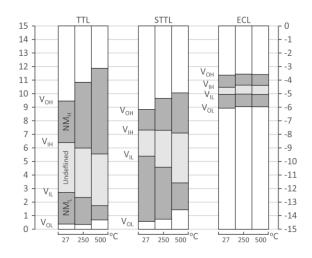

FIG. 6 FO-10 inverter logic level diagram for optimized ECL, TTL and STTL circuits at different temperatures, where supply voltage = |15| V.

rmance degradation where its  $NM_L/NM_H$  decreases from 4.8 V/1.5 V at  $V_{CC} = 15$  V to 0.1 V/0.3 V at  $V_{CC} = 7$  V and its gate delay increases significantly for  $V_{CC}$  less than 11 V. For the TTL circuit, the FO-10 inverter and 11-RO circuits cease to operate when supplied with less than 13 V and 11 V, respectively. As shown in Fig. 5, all circuits exhibit longer  $t_g$  as the temperature increases, primarily due to the expected decrease in current gain. The effect of temperature on the DC characteristics for all circuits is shown in Fig. 6. The operating temperature has a notable effect on the noise margins of the TTL and STTL circuits, as the  $NM_H$  increases and  $NM_L$  decreases with increasing temperature. The ECL circuit is least affected by temperature where its noise margins degrade by ~0.1 V and  $t_g$  increases by ~2.3 ns, when the temperature is increased from 27 °C to 500 °C.

#### 3. Conclusions

A thorough comparison of different bipolar technologies in 4H-SiC is presented. All discussed bipolar technologies show stable performance across wide range of temperatures, exceeding the limits of Si-based circuits. The ECL and STTL technologies also show excellent stability across power supply voltages. The obtained results demonstrate the potential of robust bipolar ICs in 4H-SiC for small-scale logic applications.

#### Acknowledgements

This work is supported by Mubadala and the Semiconductor Research Corporation (SRC) contract number 2011-HJ-2187.

## References

- S. Singh and J. A. Cooper, IEEE Trans. Electron Devices, vol. 58, 1084 (2011).

- [2] L. Lanni, B. G. Malm, M. Östling, and C.-M. Zetterling, IEEE Electron Device Lett., vol. 34, 1091 (2013).

- [3] S. Singh, N. El Sayed, H. Elgabra, T. ElBoshra, M. Wahbah, M. Al Zaabi, in *Materials Science Forum 2014, Proceedings* of the 15<sup>th</sup> Int. Conf. Silicon Carbide Relat. Mater, Miyazaki, Japan, 29 September-4 October 4 2013, pp. 1009–1012.