# Investigation of trap properties in High-k/Metal Gate pMOSFETs of Higher Al Energy and Concentration Ion Implantation on Random Telegraph Noise

Tsung-Hsien Kao<sup>1\*</sup>, Shoou-Jinn Chang<sup>1</sup>, Yean-Kuen Fang<sup>1</sup>, Po-Chin Huang<sup>1</sup>, Yan-Kuin Su<sup>1</sup>, Ying-Jun Shen<sup>1</sup>, Chung-Yi Wu<sup>2</sup> and San-Lein Wu<sup>2</sup>

<sup>1</sup> Institute of Microelectronics and Department of Electrical Engineering, Advanced Optoelectronic Technology Center, Center for Micro/Nano Science and Technology, National Cheng Kung University, Tainan 701, Taiwan <sup>2</sup> Departments of Electronic Engineering, Cheng Shiu University, Kaohsiung 833, Taiwan Phone: +886-6-2757575 ext.62391 Fax: +886-6-2671854 \*e-mail: market200000@gmail.com

#### Abstract

In this study, the impact of aluminum ion implantation (Al I/I) with different energy and doses on random telegraph noise (RTN) in high-k/metal gate (HK/MG) p-type metal–oxide–semiconductor field-effect transistors (pMOSFETs) was investigated. The Al I/I can reduce oxide trap densities, because the Al filled the defects and formed a thin Al<sub>2</sub>O<sub>3</sub> layer. However, when energy and doses increased, higher Al concentration will cause gate tunneling current density (J<sub>G</sub>). In addition, in the RTN, we were also observed that the trap position (X<sub>T</sub>) in the control device was lower, maybe due to Al not diffusion too deeply near SiO<sub>2</sub>/Si interface.

# 1. Introduction

Random telegraph noise (RTN) is a special kind of g-r noise occurred at the range of low frequency. RTN originates from the trapping/detrapping behaviors of a single trap, resulting in the phenomena of two discrete current levels in the time domains and is believed as a good approach to study the individual defect properties in small-area MOSFETs (1  $\mu$ m<sup>2</sup> <). It is known that RTN can be used to monitor distributions and characteristics of oxide traps. Thus, RTN should be an effective tool for studying individual defect behavior via carrier capture and emission, which in turn, should be beneficial for the development of new process flows. As the continued shrinking of conventional CMOS devices, the suppression of higher gate leakage current owning to decreasing gate oxide thickness has emerged as a key technology for improving device performance [1]. For the sub-28-nm era, issues such as direct gate tunneling, poly-gate depletion, gate sheet resistance, boron penetration, and Fermi level pinning [2] all become severe obstacles to the improvement of device performance. To overcome these obstacles, HK materials and MG electrodes have been used to replace conventional SiO<sub>2</sub> gate oxide and poly-gate electrodes, respectively. Hafnium (Hf) based high-k stacks have an attraction for replacing SiO2 as the insulator of metal-oxide-semiconductor field-effect transistors (MOSFETs) due to the high permittivity, appropriate band gap (E<sub>G</sub>), and good thermal stability with Si. However, fabricating MG pMOSFETs with a low threshold voltage (V<sub>T</sub>) and with a small equivalent oxide thickness (EOT) in particular is still a crucial challenge in gate-first integration owing to the presence of numerous oxygen vacancies and defect sites in the HK gate dielectric [3]. It has been reported that one can employ an Al2O3 capping layer to modulate the effective work function (EWF) near the Si valence band edge to meet the V<sub>T</sub> requirement of pMOSFETs. However, the use of an Al<sub>2</sub>O<sub>3</sub> capping layer often results in increased EOT. Alternatively, to obtain a large V<sub>FB</sub> shift with a minimal EOT penalty in HK/MG pMOSFETs, aluminum ion implantation (Al I/I) technology was implemented and identified as an effective approach for EWF modulation without increasing the EOT or involving a complex process. In this paper, the use of RTN to evaluate HK/MG pMOSFETs with different energy and doses of Al I/I was investigated. The effects of employing Al I/I on trap properties, such as activation energy, capture and emission kinetics, and spatial depth

from the channel of HK/MG pMOSFETs, were investigated by temperature-dependent RTN.

#### 2. Device Structure and Experiment

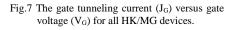

The Al I/I pMOSFETs used in this study were all fabricated using 28-nm gate-first HK/MG technology CMOS process are illustrated in Fig. 1. The gate dielectrics consisted of a ~1-nm-thick thermally grown SiO<sub>2</sub> interfacial layer (IL) and a ~2.5-nm-thick HfO<sub>2</sub> film prepared by atomic layer deposition. A 10-nm-thick TiN layer prepared by radio-frequency physical vapor deposition was then deposited on top of the gate dielectrics. The Al I/I was subsequently performed through TiN following gate metal deposition with implantation energy of 1.2 keV and dose of  $5 \times 10^{15}$  cm<sup>-2</sup> is control device, at 1.5 keV with a dose of  $5 \times 10^{15}$  cm<sup>-2</sup> and  $1 \times 10^{16}$  cm<sup>-2</sup> for devices A and B, respectively. To avoid singularity effects and demonstrate the reproducibility of the oxide trap characteristics, three devices were measured to determine the device-to-device variation and ensure that the results are reproducible [4].

#### 3. Results and Discussion

To understand the effects of Al I/I on the trap parameters within HK dielectrics, we measured the RTN characteristics of the all fabricated devices. In the RTN measurement, a distinct difference in I<sub>D</sub> between two states under different V<sub>G</sub> is observed as shown in Fig. 2 for the control device, devices A, B, respectively, which is responsible for carrier trapping and detrapping at a single trap site and confirms the existence of RTN in all devices. The extracted mean capture time ( $\tau_c$ ) and mean emission time constant  $(\tau_e)$  as functions of the gate overdrive  $(V_G - V_T)$  plot is shown in Fig. 3. It should be noted that small values of  $\tau_c$  and  $\tau_e$  indicate that capture and emission events occur very frequently and that a given device has a small trap depth (X<sub>T</sub>). The Fig. 3 also shows that  $\tau_c$  decreases and  $\tau_e$  increases with the increase in V<sub>G</sub> - V<sub>T</sub> for all devices. Figure 4 shows the dependence of  $ln(\tau_c / \tau_e)$  on  $V_G$  -  $V_T$ for the fabricated devices. The X<sub>T</sub> from the insulator/semiconductor interface can be extracted using the following formulas [5]:

$$\begin{split} X_{T1} = & \left( T_{oxt} + \frac{\varepsilon_{oxt}}{\varepsilon_{ox2}} T_{ox2} \right) \left( \frac{k_B T}{q} \frac{\partial \ln(\tau_c/\tau_e)}{\partial V_G} + \frac{\partial \varphi_s}{\partial V_G} \right) \left( \frac{\partial \varphi_s}{\partial V_G} - 1 \right) \dots (1) \\ X_{T2} = & \left( T_{ox2} + \frac{\varepsilon_{ox2}}{\varepsilon_{oxt}} T_{oxt} \right) \left( \frac{k_B T}{q} \frac{\partial \ln(\tau_c/\tau_e)}{\partial V_G} + \frac{\partial \varphi_s}{\partial V_G} \right) \left( \frac{\partial \varphi_s}{\partial V_G} - 1 \right) + \left( 1 - \frac{\varepsilon_{ox2}}{\varepsilon_{oxt}} \right) T_{oxt} \dots (2) \end{split}$$

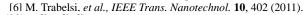

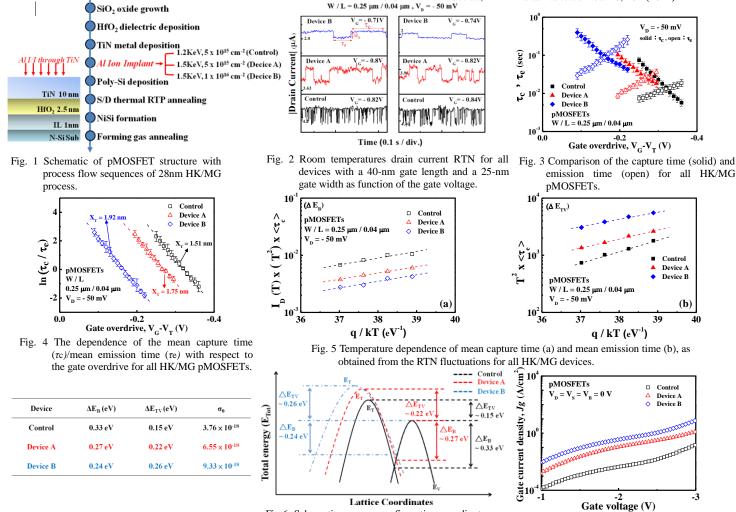

where  $X_{T1}$  and  $X_{T2}$  are the trap depths for the active traps located within the IL of SiO<sub>2</sub> and within the HK layer, respectively.  $T_{ox1}$ and  $T_{ox2}$  are the physical thicknesses of the IL and HK layers, respectively.  $\varepsilon_{ox1}$  and  $\varepsilon_{ox2}$  are the dielectric constants of SiO<sub>2</sub> and the HK film, respectively. As shown in Fig. 4, the dashed lines represent the linear fitted curves that are used to obtain the  $X_T$ values of all devices. The obtained values of  $X_T$  are 1.92, 1.75, and 1.51 nm for device B, device A, and the control device, respectively. In other words, the trap in the HK layer was located closer to the IL/Si interface for the control device, than it was for the other both devices. This observation should be attributed to the fact that the implanted Al could react with oxygen vacancies at the bottom of the HfO2 layer to form Al-Si-O bonds and thus induce dipoles at the HfO<sub>2</sub>/SiO<sub>2</sub> interface. But, when energy and doses increased, higher Al concentration diffusion too deeply near SiO<sub>2</sub>/Si interface will accompanied with EOT increasing and cause gate tunneling current density (J<sub>G</sub>) performance degradation due to non-optimized implant condition. In addition, Fig. 5 (a) and (b) shows temperature-dependent RTN fluctuations measured for these three devices.  $\tau_c$  and  $\tau_e$  decrease as temperature increases. Based on the temperature-dependent RTN results, from Table I we should be able to extract the barrier energy ( $\Delta E_B$ ) for carrier capture, the activation energy ( $\Delta E_{TV} = E_T - E_V$ ) for carrier emission, and the effective capture cross-section ( $\sigma_0$ ) of the defect [6]. Here,  $\Delta E_{TV}$  is defined as the energy difference between the trap level  $(E_T)$  in the gate dielectric and the valence band maximum  $(E_V)$  in silicon. In other words,  $\Delta E_B$  decreased by 0.09 eV, whereas  $\Delta E_{TV}$ increased by 0.11 eV for device B relative to the control device. Based on these values, we can plot a schematic energy configuration-coordinate diagram of the all fabricated devices. As shown in Fig. 6, it was observed that the trap in the control device had a lower energy level  $(E_T)$  and was located closer to the IL/Si interface than that in the other both devices. It should be noted that the higher  $E_T$  is, the smaller the energy difference  $(E_T - E_F)$  becomes (i.e., the trap energy level  $E_T$  can cross the Fermi level,  $E_F$ , easily). Thus, the lower  $E_T$  observed for the control device suggests the intersection of the emission and capture times should occur at a large negative gate overdrive, which agrees well with the results shown the Fig. 3. This discrepancy should be attributed to the fact that the implanted Al could fill defects and form a thin Al<sub>2</sub>O<sub>3</sub> layer, but excess Al ions accumulated to the SiO2/Si interface maybe cause J<sub>G</sub>, V<sub>FB</sub> and reliability degradation.

On the other hand, the tunneling barrier height  $\varphi_B$  for holes became smaller, and the tunneling attenuation length for carriers penetrating into the dielectric,  $\lambda$ , became longer. The reduced  $\lambda$ implies a smaller tunneling probability and lower JG for the control device. The J<sub>G</sub> of  $1.22 \times 10^{-4}$ ,  $1.66 \times 10^{-3}$  and  $8.57 \times 10^{-3}$ A/cm<sup>2</sup> were obtained for control device, devices A and B, respectively, under bias condition of  $V_G = -1$  V and  $V_D = V_S = V_B = 0$  V shown in the Fig. 7. Smaller J<sub>G</sub> of the control device verifies clearly the device has a higher  $\phi_B$  than that in the other both devices.

# 4. Conclusions

We investigated the behavior of traps in HK/MG pMOSFETs with Al I/I and different energy and doses using RTN. Although the Al I/I can improve the quality of gate stacks by passivating defects in insulator, higher Al concentration would cause the degradation in  $J_G$  owing to the lower  $\phi_B$  and longer  $\lambda$  for hole, which can be attribution to the accumulation of excess Al at SiO2/Si interface. More studies must be carried out to optimize the Al profile to minimize the induced worsening of gate leakage by the diffusion of Al too deep into the Si substrate will not lead to deterioration of the reliability and performance.

## Acknowledgements

This work was supported by the National Science Council (NSC) of Taiwan under contract No. MOST 103-2221-E-006 -128 -MY3.

## References

- [1] R. M. Wallace et al., Crit. Rev. Solid State, 28, 231 (2003).

- [2] H. Y. Lin et al., Appl. Phys. Lett, 98, 123509 (2011).

- [3] Y. W. Chen et al., IEEE Electron Device Lett. 31, 1290 (2010).

- [4] C. Leyris, et al., Microelectron. Reliab, 47, 41 (2007).

- [5] S. Lee, et al., IEEE IEDM Tech. Dig, 763 (2009).

Table I. Extracted barrier energy ( $\Delta E_B$ ), trap activation energy (  $\Delta E_{TV} = E_T - E_V$  ), and effective capture cross-section ( $\sigma_0$ ) of all devices.

Fig.6 Schematic energy configuration-coordinate diagram showing the changes in total energy of the system as a hole is transferred from the inversion layer into an interfacial defect.