# High-Yield Fabrication of n-Type Carbon Nanotube Thin-Film Transistors on Plastic Substrate

Fu-Wen Tan<sup>1</sup>, Jun Hirotani<sup>1</sup>, Tomohiro Yasunishi<sup>1</sup>, Shigeru Kishimoto<sup>1</sup>, and Yutaka Ohno<sup>1,2</sup>

<sup>1</sup>Graduate School of Engineering, Nagoya University, Furo-cho, Chikusa-ku, Nagoya 464-8603, Japan

<sup>2</sup>Institute of Material and Systems for Sustainability, Nagoya University, Furo-cho, Chikusa-ku, Nagoya 464-8603, Japan Phone: +81-52-789-5387, E-mail: yohno@nagoya-u.jp

#### Abstract

Carbon nanotube thin-film transistors (CNT TFTs) are promising active device for various flexible/stretchable devices because CNTs exhibit excellent mechanical and electrical properties. As-fabricated CNT TFTs normally show p-type characteristics, thus n-type TFTs are necessary to construct complementary metal-oxide-semiconductor-based devices. We have fabricated more than 800 air-stable, n-type CNT TFTs on a flexible plastic substrate with high yield by chemical doping technique. We confirmed 99.5 % of devices changed from p- to n-type characteristics with small hysteresis.

## 1. Introduction

Single-walled carbon nanotubes (CNTs) are suitable materials for high-performance future electronic devices due to its highly desirable electrical and mechanical properties. In particular, a thin film of randomly arranged CNTs can be used as the conductive channel for thin-film transistors (TFTs) on flexible substrates, [1,2] which meets the demands of wearable healthcare/medical electronic devices.

As-fabricated CNT TFT devices are normally p-type, due to the adsorption of oxygen molecules in the ambient air [3]. However, devices with n-type characteristics are required to realize complementary metal-oxide-semiconductor (CMOS)based circuits because of its good noise margin and low power consumption [4,5].

There are several methods to fabricate n-type CNT TFTs, in particular, solution based chemical doping with poly(ethylene) imine (PEI) [6] combined with surface passivation offers stability of dopant in air and ease of controlling the doping level [7]. However, the yield of n-type devices is still one of the unresolved issues.

In this work, we have fabricated more than 800 n-type CNT TFTs on a flexible substrate with high yield on the basis of PEI doping combined with surface passivation.

# 2. Experimental

Semiconducting CNTs extracted by gel chromatography [8] were used as channel material. The mean diameter and length of individual CNTs were estimated to be 1.3 nm and 0.52  $\mu$ m respectively by absorption spectroscopy and atomic force microscopy.

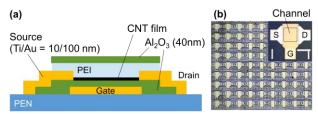

We have adopted poly(ethylene naphthalate) (PEN) as a flexible and transparent substrate. The schematic device structure of a bottom gate TFT is shown in Figure 1(a). Channel length and width are 100  $\mu$ m. The Ti/Au (10/100 nm) electrodes were formed by conventional photolithography, electron-beam evaporation, and lift-off process. A 40-nm-

Fig.1 (a) Schematic structure of a typical n-type device. (b) Optical micrograph of CNT TFT device with channel length and width of 100  $\mu$ m. (scale bar: 100  $\mu$ m) (inset) and an array of CNT TFTs.

thick  $Al_2O_3$  gate oxide layer was deposited by atomic layer deposition (ALD) process. A CNT film was formed on the  $Al_2O_3$  layer by transfer process and patterned by oxygen plasma [9]. Before chemical doping with PEI, electrical characteristics of the CNT TFTs were measured. Concentrationoptimized PEI (Sigma Aldrich, MW = 800) dissolved in methanol was spin-coated onto the substrate for n-type doping. Subsequently, an  $Al_2O_3$  passivation layer was formed by ALD and patterned by photolithography and reactive ion etching. The fabricated array of CNT TFTs with bottom-gate structure is shown in Fig. 1(b). More than 800 devices were fabricated on a PEN film.

Their characterization was performed in ambient air. Transfer characteristics were measured by sweeping gate voltage ( $V_{GS}$ ) from 2 V to -2 V. On-current was evaluated at the saturation region ( $V_{DS} = 4$  V) of  $I_D$ - $V_{DS}$  characteristics.

## 3. Results and Discussion

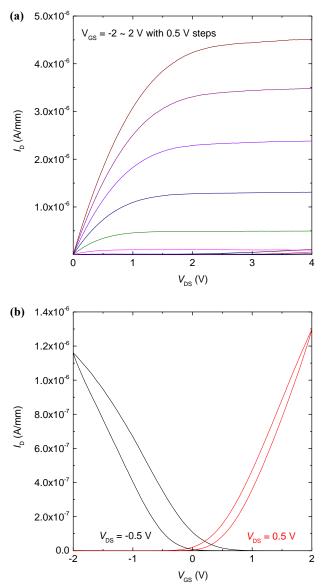

In the first phase of the fabrication process, the 831 devices showed p-type behavior with good on/off ratio of  $10^4$  and relatively uniform characteristics. The second phase involved n-type doping and Al<sub>2</sub>O<sub>3</sub> passivation onto the p-type devices. The output and transfer characteristics of a device before and after doping are shown in Fig. 2. The device characteristics changed from p- to n-type without significant degradation of on-current and mobility. Hysteresis was reduced as a result of Al<sub>2</sub>O<sub>3</sub> passivation.

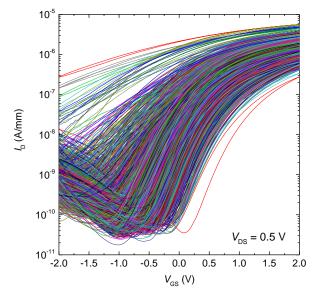

Figure 3 shows the transfer characteristics of 827 operational devices after PEI doping. 99.5 % of 831 devices were converted to n-type behavior by our n-type doping method. Four devices did not work after doping due to gate leakage current or damage during measurement. A majority of the TFTs maintain a good on/off ratio of  $10^4$ , with an average hysteresis width of 0.25 V. However, low on/off ratio and threshold voltage shift toward the normally-on condition are

Fig. 2 (a) Typical  $I_{\rm D}$ - $V_{\rm DS}$  curves of an n-type device. (b) Typical  $I_{\rm D}$ - $V_{\rm GS}$  curves of a TFT before and after doping. After PEI doping and Al<sub>2</sub>O<sub>3</sub> passivation, the device shows a small hysteresis.

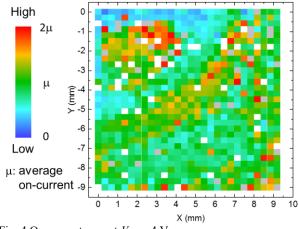

exhibited by a few percentages of devices. This is probably due to non-uniformity of doping levels caused by spin coating method, which is in agreement with the on-current map in Fig. 4. Improvement in doping process should be able to yield better overall homogeneity in the n-type characteristics.

#### 4. Conclusions

We have fabricated n-type CNT TFTs on a flexible plastic substrate with high yield. The n-type doping was performed by PEI coating with Al<sub>2</sub>O<sub>3</sub> passivation. Although threshold voltage of some devices shifted to normally-on side due to non-uniformity of doping levels, majority of the devices kept a good on/off ratio of 10<sup>4</sup>. A 99.5% highly efficient n-type conversion and reduction of hysteresis were achieved.

Fig. 3  $I_{\rm D}$ - $V_{\rm GS}$  curves at  $V_{\rm DS} = 0.5$  V of 827 n-type devices.

Fig. 4 On-current map at  $V_{\rm DS} = 4$  V.

#### Acknowledgements

The semiconducting CNTs were provided by TASC. This work was partially supported by Grant-in-Aid by MEXT, NEDO, and JST/SICORP.

#### References

- [1] Q. Cao et al., Nature 454, 495 (2008).

- [2] D.-M. Sun et al., Nat. Nanotechnol. 6, 156 (2011).

- [3] E. S. Snow et al., Appl. Phys. Lett., 82, 2145 (2003).

- [4] M. L. Geier et al., Nat. Nanoechnol. 10, 944 (2015).

- [5] Y. Zhao et al., ACS Nano 10, 2193 (2016).

- [6] M. Shim et al., J. Am. Chem. Soc., 123, 11512 (2001).

- [7] T. Yasunishi et al., Jpn. J. Appl. Pys. 53, 05FD01 (2014).

- [8] T. Tanaka et al., Appl. Phys. Express, 1, 114001 (2008).

- [9] J. Hirotani et al., Extended Abstracts of the 2015 International Conference on Solid State Devices and Materials (2015) 722.