# Electrostatic perturbations from TSV processing during 3D integration of advanced CMOS Technologies

C. Kothandaraman, K. Sakuma and S.A.Cohen IBM T.J. Watson Research Center Yorktown Heights, NY10598, USA Phone : +001 234 456 9809 E-mail: raman1@us.ibm.com.

### Abstract

Due to complex processing TSV integration can perturb the functionality of the underlying CMOS technology. In this paper we summarize the results on the electrostatic perturbations caused by TSV on devices in proximity and describe characterization techniques to detect them. Potential issues in packaging and wafer to wafer bonding are identified and potential solutions are demonstrated.

## 1. Introduction

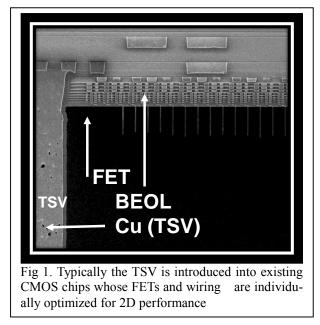

Through Silicon Via (TSV) are the basic elements for achieving 3D integration, essential for improved system performance in the era of saturating transistor performance. They provide the pathway to providing power as well as signal communication among the various layers in a 3D chip. Often, these TSVs are introduced into advanced CMOS technology layers that are optimized for yield and performance as stand-

alone 2D chips (Fig1). However, the high aspect ratios involved in the TSV along with challenges introduced due to process can perturb the functionality of the CMOS layer. In this paper, we discuss such a perturbation, one that is related to electrostatic charges resulting from TSV process.

## 2. TSV interaction to Devices

Initial attempts at making copper filled TSV were thwarted by the severe thermal expansion mis-match between

copper and silicon resulting in extrusions. Such structural issues were addressed with improved adhesion to the liners and 'bottoms-up' plating of Cu. Although the extrusions were prevented the stress resulted in the change in device characteristics in proximity to TSV. Such perturbations are typically addressed via suitable choice of 'keep-out-zone', where devices are forbidden [1].

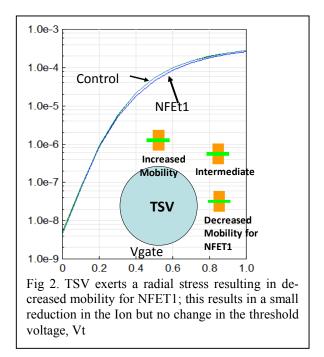

Such stresses typically affect the channel mobility resulting in changes to the device currents (saturation current, Ion or the linear current, Idlin). For e.g., the radially tensile stress from the TSV exerts a tangential compressive stress resulting

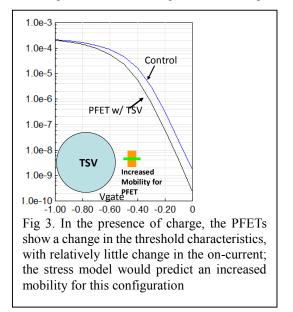

in the reduction of the ion of NFET1 (Fig 2) while no change is observed in the threshold voltage (Vt). However, if there are positive charges present in proximity, either through mobile ion contamination [2] or copper extrusions [3], the threshold voltage is changed (Fig 3).

While changes in mobility are problematic for accurate device models essential for circuit design, mobile ion contamination causes a more fundamental issue for proper functioning of the chip as the ions are mobile at chip operating temperature resulting in unpredictable circuit function in the field.

#### 3. Characterisation and Mitigation

While the presence of ions such as Cu, Na, K are easily detected by analytical techniques such as SIMS, it is much

more suitable to detect them via electrical characterization techniques that have the added advantage of being non-destructive. Id-Vg curves such as in Fig 3 can show the presence

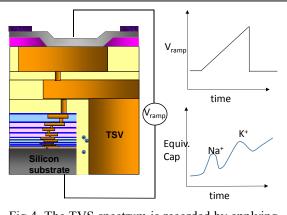

of charge, it cannot identify the species or give an idea about their concentration. C-V techniques, while sensitive to the presence of charge, again, do not have any specificity to the type of mobile ions or their concentrations. We have adapted the technique of triangular voltage sweeps (TVS) to address this issue Fig 4.

Fig 4. The TVS spectrum is recorded by applying a ramp voltage and recording the current, typically expressed as an equivalent capacitance; lighter ions such as  $Na^+$  typically show up earlier and have sharper peaks than heavier ions such as  $K^+$  or  $Cu^{++}$

This technique was demonstrated to show specificity to both mobile ions such as Na and K coming from CMP chemistries as well as Cu extrusions from TSV[3]. When unable to change CMP buffering agents, the primary source of mobile ions, cleaning with chelating agents were used to remove the impact of mobile ions. Cu migrations were stemmed by improved integration of the liner materials for the TSV.

# 4.0 Impact from thinning and packaging

Besides the potential for the migration of ions from BEOL 3D integration has another significant challenge posed by the

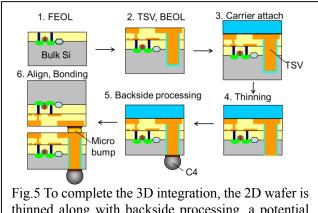

thinned along with backside processing, a potential source for the introduction of ions. This can pose additional sources of perturbation to devices.

thinning and the subsequent assembly process (Fig 5). This involves back-side thinning and subsequent backside processing, during which the device side has a direct pathway for mobile ion migration, via the TSV dielectric. Wherever possible the buffering agents for CMP must have low ionics to prevent such perturbations as ions can easily migrate along the TSV dielectric from back-side to the device side. Alternatively, gettering implants can be used that can bind the mobile ions and prevent their migration to sensitive device areas.

# 3. Conclusions

Electrostatic perturbations arising from TSV processing has been described. Electrical characterization techniques for identifying the issue along with its quantification has been proposed. Potential sources of such effects in thinning and packaging are identified and mitigation strategies were discussed.

#### Acknowledgements

The authors would like to thank all members of the 3D integration team and 300 mm advanced fabrication facility in East Fishkill, NY for the samples and SIMS analysis.

#### References

- 1. [1] W. Guo et al., in 'Cu TSV induced Keep Out Zone', Proc. of the Electron Devices Meeting (IEDM), (2013).

- 2. [2] C. Kothandaraman et al. in "Through silicon via (TSV) effects on devices in close proximity the role of mobile ion penetration characterization and mitigation", **Proc. of the Electron Devices Meeting (IEDM), (2014).**

- 3. [3] C. Kothandaraman et al. in "Triangular voltage sweep characterization for TSV reliability" **Proc. of International Reliability Physics Symposium** (IRPS), (2016).