# Impact of Rapid Cooling Process in Ultra-high-temperature Oxidation of 4H-SiC(0001)

Mitsuru Sometani<sup>1,2</sup>, Daisuke Nagai<sup>1</sup>, Takuji Hosoi<sup>1</sup>, Takayoshi Shimura<sup>1</sup>, Yoshiyuki Yonezawa<sup>2</sup>,

Manabu Takei<sup>3</sup>, and Heiji Watanabe<sup>1</sup>

<sup>1</sup> Graduate School of Engineering, Osaka University,

2-1 Yamadaoka, Suita, Osaka 565-0871, Japan

Phone: +81-29-861-8742 E-mail: m.sometani@aist.go.jp

<sup>2</sup> National Institute of Advanced Industrial Science and Technology,

Tsukuba West, 16-1 Onogawa, Tsukuba, Ibaraki 305-8569, Japan

<sup>3</sup> Fuji Electric Co., Ltd.,

1 Fujimachi, Hino, Tokyo 191-8502, Japan

## Abstract

A systematic evaluation of ultra-high-temperature oxidation, focusing on the cooling process, was performed. Sufficient Ar displacement to suppress oxide growth during the cooling process revealed the superiority of an ultra-high-temperature oxidation process in obtaining an improved metal-oxide-semiconductor (MOS) interface. In addition, a rapid water-cooling process was investigated, aimed at minimizing degradation of the MOS interface due to SiO<sub>2</sub> decomposition at ultra-high temperature in non-oxidizing ambient. The rapid water-cooling process after ultra-high-temperature oxidation achieved the lowest interface state density compared with other cooling processes.

## 1. Introduction

For reduction in the ON-resistance of SiC metal-oxidesemiconductor (MOS) devices, a gate oxide process which can reduce the interface state density  $(D_{it})$  is necessary. In general, nitridation is performed after gate oxide formation, to reduce the  $D_{it}$ . However, it has been reported that the nitridation process causes flatband voltage ( $V_{\rm FB}$ ) shift due to hole trapping under negative gate bias stress [1]. Thus, a gate oxide process without nitridation is required, to achieve both low  $D_{\rm it}$  and suppressed  $V_{\rm FB}$  shift. A number of studies have reported that an ultra-high-temperature oxidation process might be a candidate to improve interface characteristics [2.3]. However, we believe that systematic results have not yet been obtained, because there is a lack of adequate discussion regarding the cooling process after ultra-high-temperature oxidation. Thus, in this study, we systematically evaluated the ultra-high-temperature oxidation process, focusing on the cooling process.

### 2. Experiments

4H-SiC(0001) substrates with an n-type epilayer were used in the study. 40-nm-thick SiO<sub>2</sub> films were formed by thermal oxidation at temperatures ranging from 1150°C to 1600°C, in dry O<sub>2</sub>, in an ultra-high-temperature rapid annealing furnace [4]. After oxidation, a variety of different cooling processes from oxidation temperature were attempted. Then, Al gate electrodes were deposited to form MOS capacitors, by vacuum evaporation through a shadow mask. The  $D_{\rm it}$  for each sample was evaluated using the high-low method.

#### 3. Results and Discussion

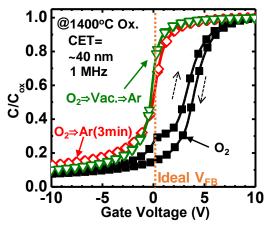

Figure 1 shows a comparison of the high-frequency *C-V* curves measured for SiC MOS capacitors with varying cooling ambient, after oxidation at 1400°C. The *C-V* curve of the MOS capacitor cooled in  $O_2$  ambient exhibited hysteresis and positive  $V_{\rm FB}$  shift. On the other hand, the *C-V* curves of the MOS capacitors using Ar ambient or Ar gas displacement after vacuum pumping exhibited no hysteresis and ideal  $V_{\rm FB}$ , suggesting that oxide growth during the cooling process may be suppressed to improve the electrical properties of the SiO<sub>2</sub>/SiC interface.

Fig. 1. Comparison of high-frequency C-V curves measured for SiC MOS capacitors with various cooling ambient after oxidation at 1400°C.

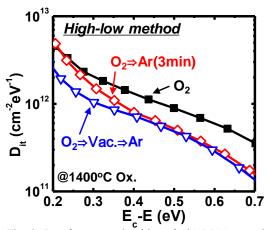

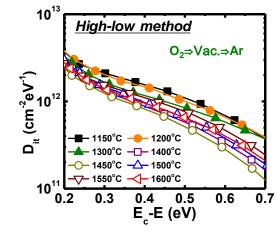

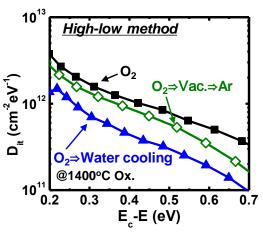

Figure 2 shows the interface state densities of SiC MOS capacitors with varying cooling ambient. The  $D_{it}$  located in the energy region of  $E_c$ -E = 0.3-0.7 eV was reduced by the cooling process using Ar ambient. In addition, the  $D_{it}$  located in the energy region of  $E_c$ -E < 0.4 eV was reduced by Ar gas displacement after vacuum pumping, indicating that Ar displacement sufficient to suppress oxide growth during the cooling process is required, to reduce the  $D_{it}$  located in the shallow energy region. Figure 3 shows the energy distribution of  $D_{it}$  with varying oxidation temperature, using the cooling

Fig. 2. Interface state densities of SiC MOS capacitors with various cooling ambient after oxidation at 1400°C.

Fig. 3. Interface state densities of SiC MOS capacitors with various oxidation temperatures using cooling process of Ar gas displacement after vacuum pumping.

process involving Ar gas displacement after vacuum pumping. It was found that the  $D_{it}$  value clearly depended on the oxidation temperature, and oxidation at 1450°C resulted in the lowest  $D_{it}$ .

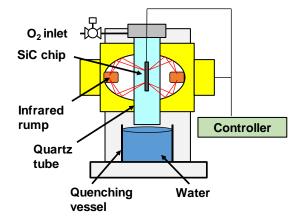

Next, we investigated the degradation of the MOS interface at ultra-high temperature in non-oxidizing ambient, and employed a rapid cooling process in order to validate our concept. Figure 4 shows a schematic illustration of ultra-hightemperature oxidation with a rapid water-cooling setup, in which the SiC chip is dropped into water immediately after thermal oxidation, to maximize the cooling rate. Using this setup, additional oxidation during the cooling process is completely suppressed, without vacuum pumping and Ar gas displacement. Figure 5 shows the D<sub>it</sub> of MOS capacitors fabricated with and without the water-cooling process. It was found that the water-cooling process effectively reduced the  $D_{\rm it}$  values in all energy regions, compared with the other processes, probably due to preservation of the high-quality SiO<sub>2</sub>/SiC interface formed by ultra-high-temperature oxidation.

Fig. 4. Schematic illustration of ultra-high-temperature oxidation with rapid water cooling setup.

Fig 5. Effect of water-cooling process on interface state densities of SiC MOS capacitors.

#### 4. Conclusions

The cooling process after ultra-high-temperature oxidation was systematically investigated. It was found that ideal  $V_{\rm FB}$  and low  $D_{\rm it}$  can be obtained in ultra-high-temperature oxidation by Ar displacement sufficient to suppress oxide growth during the cooling process. Additionally, to minimize degradation of the MOS interface during the ultra-high-temperature process in non-oxidizing ambient, we designed a rapid water-cooling setup, and found that the  $D_{\rm it}$  values of MOS capacitors fashioned using the proposed rapid watercooling process achieved the lowest  $D_{\rm it}$  values compared with other cooling processes.

## Acknowledgements

This work was supported by Council for Science, Technology and Innovation (CSTI), Cross-ministerial Strategic Innovation Promotion Program (SIP), "Next-generation power electronics" (funding agency: NEDO).

#### References

- [1] Y. Katsu et al., Mater. Sci. Forum 858 (2016) 599.

- [2] S. M. Thomas et al., IEEE J. Electron. Dev. Soc. 2 (2014) 114.

- [3] H. Naik, T. P. Chow, Mater. Sci. Forum 778-780 (2014) 607.

- [4] T. Hosoi et al., to be presented in ECSCRM2016.