# Enhanced Electrical and Reliability Characteristics in Ge p-MOSFETs by In-situ Plasma Treatments and Capping Hf/Zr on Interfacial Layers

Tse-Jung Huang, Chia-We Hsu, Kuei-Shu Chang-Liao\*, Yi-Wen Hsu, Chin-Hsiu Huang, and Yan-Lin Li

Department of Engineering and System Science, National Tsing Hua University, No. 101, Section 2, Kuang-Fu Road, Hsinchu, Taiwan 30013, R.O.C . \*Phone: +886-3-5742674, Email: lkschang@ess.nthu.edu.tw

## Abstract

A Ge p-MOSFET with an ultralow equivalent oxide thickness (EOT) of ~0.47 nm and a high hole mobility of ~401 cm<sup>2</sup>/V-s is demonstrated in this work. The excellent electrical characteristics are obtained by in-situ H<sub>2</sub> and NH<sub>3</sub> plasma treatments on the Ge/high-k interface. The enhanced drive current can be attributed to the lower EOT or higher mobility. Device with a Hf cap layer demonstrates the lowest interface trap density and stress-induced leakage current. Moreover, device with Zr cap layer has the lowest hysteresis effects and stress-induced voltage shifts.

### 1. Introduction

Germanium has been widely studied as the most promising candidate of channel material because both electron and hole mobility are about two and four times higher than those of silicon. However, the most critical thing is the formation of excellent interfacial layer (IL) between the high-k dielectric and Ge substrate. Many papers about the treatments for ILs have been reported, such as  $O_2$  plasma [1], H<sub>2</sub>O plasma [2], and desorption [3] processes. Although the equivalent oxide thickness (EOT) can be scaled down, the interface properties need improvement. It is reported that hydrogen incorporation is effective to reduce interface traps of Ge MOS devices due to the H<sup>+</sup> passivation at GeO<sub>2</sub>/Ge interface [4], and electrical characteristics are improved by ZrO<sub>2</sub>/HfO<sub>2</sub> stack gate dielectric [5]. Therefore, in-situ H<sub>2</sub> and NH<sub>3</sub> plasma treatments and Hf/Zr capping layers on ILs are investigated in this work.

#### 2. Experimental

After dilute HF clean (HF:H<sub>2</sub>O=1:100) for 10 mins to remove the native oxide, a remote H<sub>2</sub>O plasma is in-situ applied to form GeO<sub>2</sub> IL in an atomic layer deposition (ALD) chamber at 250 °C and a power of 300 W. Then, plasma treatments with H<sub>2</sub>, NH<sub>3</sub> and NH<sub>3</sub>+H<sub>2</sub> are performed, respectively. Afterwards, Hf or Zr-rich cap is in-situ deposited in ALD at 250°C on some samples. Then, a 3-nm thick HfO<sub>2</sub> or ZrO<sub>2</sub> is in-situ deposited as gate dielectrics. Next, a 100-nm thick TiN film is deposited by sputtering as metal gate, and a post metal annealing is performed at 550 °C for 30 s. A BF<sup>2+</sup> ion implantation with an energy of 25 keV and a dose of  $5 \times 10^{15}$  cm<sup>-2</sup> is performed. A 300-nm thick Al film is deposited as contact electrodes of source and drain. Lastly, a forming gas annealing is carried out at 400°C for 10 mins.

#### 3. Results AND Discussion

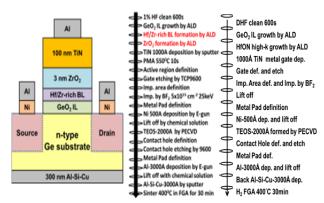

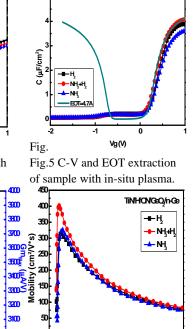

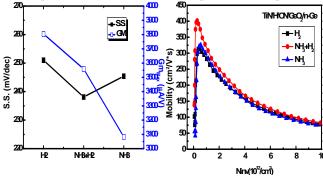

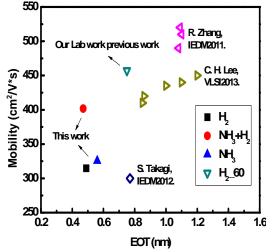

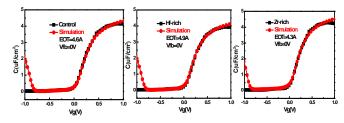

Fig.1 illustrates device structure and process flows. Fig. 2 shows  $I_D$ - $V_G$  for Ge MOSFETs with  $H_2$ ,  $NH_3$  and  $NH_3+H_2$  plasma treatments on ILs. The  $I_{OFF}$  can be lower for sample with  $NH_3$  plasma treatment. Fig. 3 shows  $I_D$ - $V_D$  for all samples. The  $I_{ON}$  of sample with  $H_2$  plasma treatment is the highest. Fig. 4 shows that  $I_g$  versus  $V_g$  curves for all samples are similar. Fig. 5 shows C-V characteristics for all samples, indicating an EOT value of ~0.47 nm. Fig. 6 shows (a) S.S. and transconductance, and (b) mobility of all samples. Sample with  $H_2$ + $NH_3$  plasma treatment has the lowest S.S. values and highest mobility. Fig. 7 shows peak hole mobility versus EOT of samples in this wrok with some published data in literatures. Sample with  $NH_3+H_2$  plasma treatment can obtain a lower EOT and a high mobility.

Fig. 1 Devices structure and process flows of Ge MOSFETs.

Fig. 2  $I_D$ - $V_G$  of samples with in-situ plasma.

Fig. 3  $I_D$ - $V_D$  of samples with in-situ plasma.

Fig. 4  $I_G$ - $V_G$  of samples with in-situ plasma.

Fig. 6 (a) S.S &  $G_m$  and (b) hole mobility of samples with in-situ plasma.

Fig. 7 Peak hole mobility versus EOT of all samples with some benchmarks.

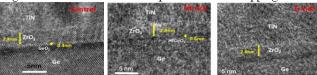

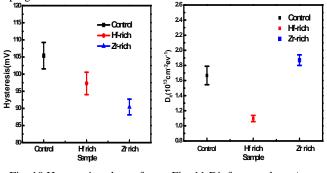

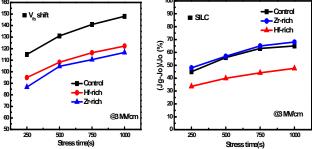

Fig. 8 shows that C-V curves and EOT values are slightly changed by capping Hf/Zr on IL. Fig. 9 shows cross-sectional TEM pictures of samples w/o or with Hf/Zr capping. Fig. 10 shows hysteresis values for samples w/o or with Hf/Zr capping, suggesting hysteresis effects can be reduced by capping a Hf or Zr on ILs. Fig. 11 shows interface trap density ( $D_{it}$ ) of all samples. Sample with Hf capping demonstrates the lowest  $D_{it}$  value because more GeO<sub>x</sub> with oxidation state of +4 can be obtained in HfGeO<sub>x</sub>. Fig. 12 shows stress-induced (a) flat-band voltage shift and (b) leakage current (SILC). Sample with Zr capping has the lowest flat-band voltage shift, and sample with Hf capping demonstrates the lowest SILC value.

Fig. 8 C-V data and EOT of samples w/o or with capping

Fig. 9 Cross-sectional TEM of (a) w/o, (b) Hf, and (c)Zr capping on IL.

Fig. 10 Hysteresis values of samples w/o or with capping.

Fig. 12 Stress-induced (a) flat-band voltage shifts, and (b) leakage current of samples w/o or with capping.

#### 4. Conclusions

shift(mV)

An EOT of ~0.47 nm and a peak hole mobility of ~401  $\text{cm}^2/\text{V-s}$  in Ge p-MOSFETs are obtained by a  $\text{NH}_3$ +H<sub>2</sub> plasma treatment. The interface traps can be minimized by a Hf cap layer, and the oxide traps can be reduced by a Zr cap layer. Therefore, electrical and reliability characteristics in Ge MOS devices can be improved by in-situ plasma treatments and Hf or Zr capping on ILs..

#### References

- [1] R. Zhang et al., 2014 IEEE Trans. ED, (2014) 61, 3668.

- [2] C.H. Fu et al., 2014 IEEE Trans. ED, (2014) 61, 2662.

- [3] C. C. Li et al., 2015 IEEE Electron Device Lett. (2015) 35, 509.

- [4] H. Matsubara et al., 2008 Appl. Phys. Lett. (2008) 93, 032104.

- [5] C. C. Li, et al., 2016 IEEE Electron Device Lett. (2016) 37, 12