# Transport property of NbSe<sub>2</sub>/WSe<sub>2</sub> van der Waals Junction

Yohta Sata<sup>1</sup>, Rai Moriya<sup>1</sup>, Yusuke Hoshi<sup>1</sup>, Satoru Masubuchi<sup>1</sup>, Kenji Watanabe<sup>2</sup> Takashi Taniguchi<sup>2</sup>, Keiji Ueno<sup>3</sup>, and Tomoki Machida<sup>1,4</sup>

> <sup>1</sup> Institute of Industrial Science, University of Tokyo 4-6-1 Komaba, Meguro-ku, Tokyo 153-8505, Japan

Phone: +81-3-5452-6158 E-mail: vsata@iis.u-tokvo.ac.jp

<sup>2</sup> National Institute for Materials Science

1-1 Namiki, Tsukuba, Ibaraki 305-0044, Japan

<sup>3</sup> Department of Chemistry, Graduate School of Science and Engineering, Saitama University

Saitama 338-8570, Japan

<sup>4</sup> Institute for Nano Quantum Information Electronics, University of Tokyo

4-6-1 Komaba, Meguro-ku, Tokyo 153-8505, Japan

#### Abstract

A transition metal dichalcogenide (TMD) NbSe<sub>2</sub> has recently received considerable attention due to its excellent metallic behavior even down to monolayer and significantly larger work function (~6 eV) among other TMDs. Therefore this material can be an efficient hole injecting electrode. Here, we show transport properties of NbSe<sub>2</sub>/WSe<sub>2</sub> van der Waals (vdW) heterojunction fabricated by mechanical exfoliation and dry transfer. Two NbSe<sub>2</sub> flakes are transferred on WSe<sub>2</sub> flake to realize van der Waals contacts and the device is encapsulated by h-BN. The current transport measured between two NbSe<sub>2</sub> contacts through the WSe<sub>2</sub> channel exhibited p-type field effect transistor characteristics having small Schottky barrier height (~50 meV) at the vdW interface. The results suggest the vdW NbSe<sub>2</sub> contact is the excellent material to make p-type contact for TMDs. Adopting NbSe<sub>2</sub> as a contact material will give us the opportunity to explore a lot of unique characteristics specific to valence band transport such as valleytronics or vertical field effect transistors [1,2].

## 1. Introduction

Semiconducting TMDs such as MoS<sub>2</sub> and WSe<sub>2</sub> revealed unique layered crystal structure connected together by vdW inter-layer interaction. These crystals can be exfoliated down to monolayers and different layered crystals can be stacked together to build vdW heterostructures. The TMD-based vdW heterostructures have been drawn considerable attention owing to their potentially high performance for electronics and optoelectronics devices. Yet, the performances of these devices are occasionally limited by the large contact resistance between metal electrode and TMD. The preparation of highly transparent electrical contact to TMD has been extensively studied in last half decade. Most of previous studies used evaporation of metals on TMD to prepare the contacts, yet surface pinning or interface reaction at the metal/TMD interface are still serious issues. More recently, instead of the evaporated metal/TMD contact, the vdW contact between metallic layered material/TMD junctions are proposed to overcome the issues mentioned above [3]. Therefore, the detailed study on the transport property in such vdW junctions is highly demanded. NbSe<sub>2</sub> is known to be a metallic TMD and becomes superconducting at low temperature. Its work function of 6.0 eV is considerably higher than the valence band energy of semiconducting TMDs such as  $MoS_2$  (5.6 eV) and  $WSe_2$  (5.2 eV) [4]; therefore it is a great candidate to build a vdW contact for the purpose of hole injection. Here we fabricated NbSe<sub>2</sub>/WSe<sub>2</sub> vdW junction and studied its transport properties.

#### 2. Device fabrication procedure

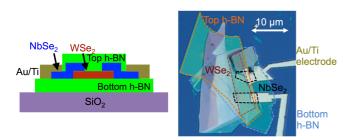

Figure 1 shows the photograph and the schematic illustration of the fabricated device. By using mechanical exfoliation and PDMS-based transfer technique [5], stack of the layered materials are fabricated on the 300 nm SiO<sub>2</sub>/Si substrate. Highly doped Si substrate works as a back gate electrode. First, hexagonal boron nitride (h-BN) with the thickness of ~30 nm is deposited on the substrate, followed by the transfer of few monolayer thick of WSe2. Next, two NbSe<sub>2</sub> flakes are individually transferred to make contacts with WSe<sub>2</sub>, and subsequently WSe<sub>2</sub> channel is capped by top h-BN flake with the thickness of ~30 nm. The width and length of the WSe<sub>2</sub> channel is 3.5 and 4  $\mu$ m, respectively. Finally, electrical contacts to NbSe<sub>2</sub> are made with 40 nm Au/40 nm Ti fabricated by electron beam (EB) lithography and EB evaporation. All device fabrications are conducted at room temperature without introducing any heat treatment [6]. The device was loaded into the variable temperature cryostat, where the device was annealed at ~140 °C in He atmosphere for 6 hours prior to the electrical characterization.

## 3. Results

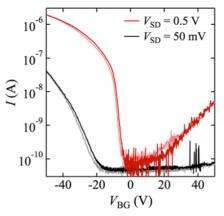

The back gate voltage  $V_{BG}$  dependence of the current *I* flow between the NbSe<sub>2</sub> contacts at different source-drain voltage  $V_{SD}$  at room temperature is presented in Fig. 2. This figure shows clear p-type field effect transistor characteristics. The current value in negative  $V_{BG}$  side (hole doped) is significantly larger than that of positive  $V_{BG}$  side (electron doped), suggesting that the NbSe<sub>2</sub> has much smaller potential barrier for hole injection than electron injection. We

obtained current on-off ratio of  $10^4$  with on current value order of micro ampere at  $V_{SD} = 0.5$  V. These properties are superior to that of NbSe<sub>2</sub>/W<sub>x</sub>Nb<sub>1-x</sub>Se<sub>2</sub>/WSe<sub>2</sub> vdW contacts fabricated by CVD method [7]. We demonstrated high quality NbSe<sub>2</sub>/WSe<sub>2</sub> vdW contact using exfoliation method.

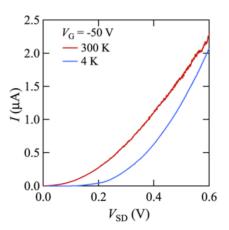

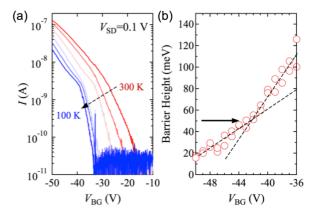

The *I*- $V_{SD}$  curves at  $V_{BG} = -50$  V at room temperature (300 K) and 4 K are presented in Fig. 3 showing non-linear behavior. This suggests Schottky barrier formation at NbSe<sub>2</sub>/WSe<sub>2</sub> interface. Fig. 4(a) presents temperature dependence of the drain current *I* at  $V_{SD} = 0.1$  V. Arrhenius plot has been created from these curves, followed by the fitting according to the thermionic emission theory. The value of the barrier height was determined when the gate voltage dependence of the barrier height deviated from linear tendency as shown in Fig. 4(b). We obtained the Schottky barrier height at NbSe<sub>2</sub>/WSe<sub>2</sub> interface of about 50 meV. The small Schottky barrier height suggests NbSe<sub>2</sub> works as a good hole injector to WSe<sub>2</sub>.

## 4. Conclusion

In summary, we made  $WSe_2/NbSe_2$  heterostructures encapsulated by h-BN by using mechanical exfoliation and PDMS dry transfer technique. The device showed the characteristics of a p-type field effect transistor, and the small barrier height was obtained by Arrhenius plot, inferring that vdW NbSe<sub>2</sub> contact could be a good p-type contact to  $WSe_2$ and other TMDs.

#### Acknowledgements

This work was partly supported by a Grant-in-Aid for Scien tific Research on Innovative Areas "Science of Atomic Layers" and "Nano Spin Conversion Science" from the Ministry of Education, Culture, Sports, Science and Technology (MEXT) and the Project for Developing Innovation Systems of MEXT and Grants-in-Aid for Scientific Research from the Japan Society for the Promotion of Science (JSPS) and CREST, Japan Science and Technology Agency (JST).

#### References

- [1] R. Moriya et al., Appl. Phys. Lett. 105 (2014) 083119.

- [2] Y. Sata et al., Jpn. J. Appl. Phys. 54 (2015) 04DJ04.

- [3] Y. Liu et al., Science Advances 2 (2016).

- [4] S. McDonnell et al., ACS Nano 8 (2014) 6265.

- [5] A. Castellanos-Gomez et al., 2D Materials 1 (2014) 011002.

- [6] N. Yabuki et al., Nature Commun. 7 (2016).

- [7] A. R. Kim *et al.*, *Nano Lett.* **16** (2016) 1890.

Fig. 1 (a) The device structure of  $WSe_2/NbSe_2$  heterostructure encapsulated with h-BN. (b) Photograph of the device.

Fig. 2  $V_{BG}$  dependence of the drain current *I* at different  $V_{SD}$  at room temperature.

Fig. 3 *I-V* characteristics of the device measured at 300 K and 4 K at  $V_{BG}$  = -50 V.

Fig. 4 (a) Temperature dependence of  $I-V_{\rm G}$  characteristics of the device measured at  $V_{\rm SD} = 0.1$  V. (b) Gate voltage dependence of barrier height obtained from the fitting of Arrhenius plot.