# Improved Performance and Sufficient Reliability In<sub>0.53</sub>Ga<sub>0.47</sub>As FinFET Using NH<sub>3</sub> Plasma Treatment

Kun Sheng Yang<sup>1</sup>, Quang-Ho Luc<sup>2</sup>, Chia Chi Chang<sup>3</sup>, Jia Wei Lin<sup>4</sup>, Chien-Chou Fan Chiang<sup>1</sup>, Huy Binh Do<sup>2</sup>, Minh Thien Huu Ha<sup>2</sup>, Sa Hoang Huynh<sup>2</sup>, Yu Da Jin<sup>3</sup>, Tuan Anh Nguyen<sup>2</sup>, Yueh-Chin Lin<sup>2</sup>, Edward Yi Chang<sup>2,4,5\*</sup>

<sup>1</sup> Institute of Photonic System

<sup>2</sup> Department of Materials Science and Engineering

<sup>3</sup> Institute of Lighting and Energy Photonics

<sup>4</sup> Department of Electronics Engineering

<sup>5</sup> International College of Semiconductor Technology National Chiao Tung Univ.

1001 University Road, Hsinchu 300, Taiwan

Phone: +886-3-5131502 E-mail: edc@mail.nctu.edu.tw

# Abstract

We present the In<sub>0.53</sub>Ga<sub>0.47</sub>As FinFET utilizing NH<sub>3</sub> passivation effects in a post remote plasma (PRP) process. A good immunity to the short channel effects is achieved and the performance is greatly improved with the high fin aspect ratio (H<sub>FIN</sub>/W<sub>FIN</sub>). Device with L<sub>CH</sub> = 50 nm, W<sub>FIN</sub> = 20 nm, and H<sub>FIN</sub> = 50 nm exhibits I<sub>on</sub>/I<sub>off</sub> ~ 10<sup>5</sup>, I<sub>DS</sub> = 1600  $\mu$ A/ $\mu$ m (V<sub>GS</sub> - V<sub>TH</sub> = 1 V), and G<sub>m,max</sub> = 2282  $\mu$ S/ $\mu$ m (V<sub>DS</sub> = 0.5 V). Besides, the positive bias temperature instability (PBTI) measurements indicate that the plasma-treated InGaAs FinFETs are quite reliable with a small threshold voltage shift and a long-term operation.

# 1. Introduction

Recently, high aspect ratio (AR) 3D III-V MOSFETs such as FinFET or nanowire/GAA FET have been considered as the promising structures to drive the CMOS technologies into sub-nanometer region [1], [2]. However, the etching-process-induced damage at the sidewall/surface of nano-patterned III-V structures needs to be addressed as one of the sources of performance degradation. In addition, the inherently poor quality of high-k/III-V interface has not been satisfied, contributing to the deterioration of III-V device characteristics. In this work, we propose NH<sub>3</sub> interfacial treatment in a post remote plasma (PRP) process to demonstrate the improved electrical performances InGaAs FinFET follow the fin ARs. From the PBTI reliability studies, the InGaAs FinFET treated by PRP treatment, being beneficial for passivating or recovering the sidewall of high-k/III-V FinFET, provides stable material properties for long-term operation.

# 2. Experimental Procedure

The epitaxial structure used in this study consisted of 50 nm p- $In_{0.53}Ga_{0.47}As$  (5 x 10<sup>16</sup> Be doped) channel layer and 100 nm p<sup>+</sup>-InP buffer layer on the p<sup>++</sup>-InP substrate grown by solid source molecular beam method as the starting material. After surface degrease, 10 nm Al<sub>2</sub>O<sub>3</sub> was grown by atomic layer deposition (ALD) as a dummy layer. Source/drain Si implantation was then performed and the dopant activation

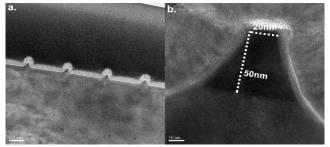

was carried out by rapid thermal annealing (RTA) in a nitrogen ambient. Then, the fin was defined via electronbeam lithography. The fin profile was done by inductively coupled plasma (ICP) dry etching and citric acid as a wet etching process. Next, the gate oxide was deposited after chemical pre-treatment with HCl (1:10) and (NH<sub>4</sub>)<sub>2</sub>S. In ALD chamber, 5 nm Al<sub>2</sub>O<sub>3</sub> was applied as gate oxide followed by in situ PRP treatment using NH<sub>3</sub>/N<sub>2</sub> gases with a plasma power of 150 W for 2 minutes. Some FinFET devices were fabricated without any in situ PRP treatment as the control samples. Finally, TiN gate metal, Au/Ge/Ni/Au S/D ohmic, and AuBe backside contact were formed and finished by post metallization annealing at 300°C in N<sub>2</sub> for 30 seconds. Fig. 1 shows the TEM images of a completed device featuring the fin profile with 20 nm fin width and 50 nm fin height.

Fig. 1 TEM of completed device (a) fins across the gate pattern and (b) the fin dimension with 20 nm fin width and 50 nm fin height.

## 3. Results and Discussion

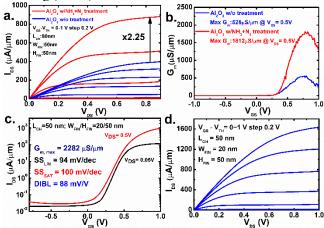

Fig. 2(a) and (b) show the output characteristics and transconductance ( $G_{m,max}$ ) of fabricated InGaAs FinFETs with channel length ( $L_{CH}$ ) of 80 nm, fin width ( $W_{FIN}$ ) of 50 nm, and fin height of ( $H_{FIN}$ ) of 50 nm for samples with and without PRP treatment. As compared to the control sample, the I<sub>DS</sub> and  $G_{m,max}$  increased 2.25 times and 3 times, respectively, for PRP treated sample. Significant improvements were clearly observed which can be attributed to the nitrogen-passivation effects obtained by the plasma process. Fig. 2(c) and (d) show the transfer and output characteristics of an L<sub>CH</sub> = 50 nm,  $W_{FIN} = 20$  nm, and  $H_{FIN} = 50$  nm FinFET treated by PRP. This device shows normalized I<sub>DS</sub> of 1600  $\mu$ A/ $\mu$ m at V<sub>GS</sub> – V<sub>TH</sub> = 1 V and V<sub>DS</sub> = 1 V, G<sub>m,max</sub> of 2282  $\mu$ S/ $\mu$ m, subthreshold swing (SS) of 100 mV/dec at V<sub>DS</sub> = 0.5 V, drain induced barrier lowering (DIBL) of 80 mV/V.

Fig 2. (a) Output and (b) transfer characteristics for InGaAs FinFETs with and without PRP treatment. (c) and (d) The electrical properties of an InGaAs FinFET with  $L_{CH}$ =50nm,  $W_{FIN}$ =20nm,  $H_{FIN}$ =50nm.

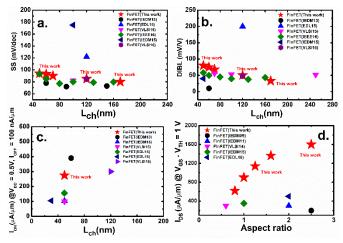

Fig 3. The devices benchmarked against the state-of-the-art InGaAs FinFETs. (a) SS, (b) DIBL, and (c) I<sub>on</sub> at  $V_{DD}=0.5V\&I_{off}=100nA/\mu m$  versus L<sub>CH</sub>; (d) I<sub>DS</sub> at V<sub>GS</sub>-V<sub>TH</sub>=1V versus aspect ratio.

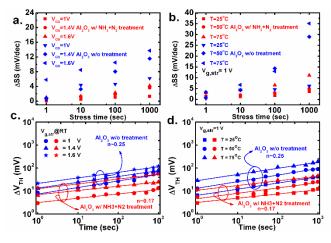

Fig 4. Time evolution of (a), (b) subthreshold swing degradation ( $\Delta$ SS) and (c), (d) threshold voltage shift ( $\Delta$ V<sub>TH</sub>) under PBTI stress for InGaAs FinFETs with and without PRP treatment.

Fig. 3 benchmarks the electrical characteristics of InGaAs FinFET presented here against those published to date [3-13]. Our results show excellent gate control ability which related to the improved performance of the scaled devices with high fin AR. This also proves that passivation the interface states at the sidewall of the high AR FinFETs play an important role in providing better electrostatic control.

Fig. 4 plots the time evolutions of the subthreshold swing degradation,  $\Delta$ SS, (Fig. 4(a) and (b)) and the threshold voltage shift,  $\Delta$ V<sub>TH</sub>, (Fig. 4(c) and (d)) under PBTI stress for different stress voltages, V<sub>g,str</sub>, and temperatures, T, for the In-GaAs FinFETs with and without PRP treatment, respectively. For the PRP treated samples, both  $\Delta$ SS and  $\Delta$ V<sub>TH</sub> against stress time follow the power law relation. A lower time exponent (*n*) value observed here indicates lower trap generation and electron trapping rates under different stress conditions, associated with a better PBTI reliability lifetime.

#### 3. Conclusions

In this work, we illustrated the improved performance and reliability on the In<sub>0.53</sub>Ga<sub>0.47</sub>As FinFETs using post remote plasma treatment. The device shows I<sub>on</sub>/I<sub>off</sub> ~ 10<sup>5</sup>, I<sub>DS</sub> = 1600  $\mu$ A/ $\mu$ m (V<sub>GS</sub> - V<sub>TH</sub> = 1 V), SS = 100 mV/dec and G<sub>m,max</sub> = 2282  $\mu$ S/ $\mu$ m (V<sub>DS</sub> = 0.5 V). In addition, from the PBTI reliability studies, the FinFETs treated by PRP treatment were observed to exhibit stable material properties after long-term operation.

#### Acknowledgements

This work was supported in part by the TSMC, NCTU-UCB I-RiCE Program, in part by the Ministry of Science and Technology, Taiwan, under Grant MOST 106-2911-I-009-301, and in part by National Chung-Shan Institute of Science and Technology, Taiwan, under Grant NCSIST-102-V211 (106).

## References

- [1] H. Wong et al., Microelectron. Eng., 138, p.57 (2015)

- [2] J. A. del Alamo, Nature, 479, p.317 (2011)

- [3] T.-W. Kim et al., IEDM Tech. Dig., p. 25(2013)

- [4] Arun V. Thathachary et al., EDL Vol.36 No.2., p.117 (2015)

- [5] IBM et al., VLSI Tech. Dig., p.176 (2015)

- [6] Vladimir Djara et al., EDL VOL.37 No.2 p.169 (2016)

- [7] J. Zhang et al., IEDM Tech. Dig., p.385 (2015)

- [8] M. L. Huang et al., VLSI Tech. Dig. (2016)

- [9] Y. Q. Wu et al., IEDM Tech. Dig. P.331 (2009)

- [10] N. Waldron et al., VLSI Tech. Dig. (2014)

- [11] M. Radosavljevic et al., IEDM Tech. Dig. P.765 (2011)

- [12] J. Franco et al., IEEE p. 6A.2.1 (2014)

- [13] Nidhi Agrawal et al., EDL Vol.36 No.2 p.120 (2015)