# Ge p-channel Tunneling FETs with steep phosphorus profile source junctions

Ryotaro Takaguchi, Ryo Matsumura, Takumi Katoh, Mitsuru Takenaka and Shinichi Takagi

The University of Tokyo

7-3-1 Hongo, Bunkyo-ku, Engineering Building #10, Tokyo 113-8656, Japan Phone: +81-3-5841-6733 E-mail: takaguchi@mosfet.t.u-tokyo.ac.jp

## Abstract

We have clarified that phosphorus can realize the highest impurity concentration ( $\sim 7 \times 10^{19}$  cm<sup>-3</sup>) and the steepest impurity profile ( $\sim 10$  nm/dec.) in Ge among solid-phase diffusion of the three n-type dopants, P, As and Sb from spin-on glass (SOG). We have demonstrated the operation of Ge p-channel TFETs with steep phosphorus profile source junctions formed by this method. Small SS<sub>min</sub> of 108 mV/dec. and high ON/OFF ratio higher than  $3.5 \times 10^5$  were observed at 150K.

## 1. Introduction

A Tunneling FET (TFET) is one of promising low power devices, because its subthreshold swing (SS) can be less than 60mV/dec. [1]. However, Si TFETs are suffering from low ON current due to the wide bandgap [2]. Therefore, small bandgap materials have been studied for TFET channel materials. Among them, Ge is a promising material for complementary TFETs, because it can be used as both n-type and ptype MOS structure channels. However, there have been very few studies on Ge p-channel TFETs (p-TFETs). One of the key technologies for superior TFETs performance is formation of defect-free and steep impurity profile source junctions. Our group has realized defect-less and steep impurity profile p<sup>+</sup>-n junctions in InGaAs by Zn diffusion from SOG and has demonstrated InGaAs TFET with low SS and high ON/OFF ratio [3]. On the other hand, Chui et al. reported that the diffusion coefficients of implanted P and As in Ge are proportional to the square of each concentration [4], as similar with that of Zn in InGaAs [3]. For that reason, we can expect that P and As provide the steep impurity profiles in Ge, as Zn in InGaAs. However, the examination of P and As profiles in Ge junctions formed by diffusion from SOG and the applications to TFETs have not been reported yet. In this study, we compared diffusion of three n-type dopants (P, As and Sb) from SOG into Ge to judge which dopant is proper for source junctions of p-TFETs. In addition, we fabricated Ge p-TFETs with source junctions formed by diffusion of these dopants and evaluated the electrical characteristics.

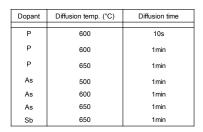

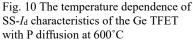

# 2. Impurity profiles of n-type dopants and $n^{\scriptscriptstyle +}\text{-}p$ junction characteristics

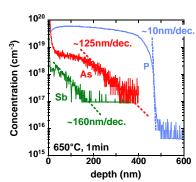

P-type (100) Ge substrates with the hole concentration of  $\sim 1.0 \times 10^{17}$  cm<sup>-3</sup> were used for dopant diffusion experiments. The diffusion condition and the fabrication process were shown in Table 1 and Fig. 1, respectively. Fig. 2 shows the *I*-*V* characteristics of n<sup>+</sup>-p diodes after RTA at 650°C for 1 min. All the diodes show high ON/OFF ratio (>10<sup>5</sup>) and ideality factors of nearly 1.0, indicating that their junctions have a low density of defects. The junctions formed by the other conditions also showed high ON/OFF ratio and good ideality factor (not shown). Fig. 3 and 4 show the depth profiles of n-type

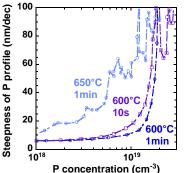

dopants after RTA. P showed higher impurity concentration and steeper profile than the other dopants. P diffusion by RTA at 600°C for 1 min showed not only the highest impurity concentration ( $\sim$ 7×10<sup>19</sup> cm<sup>-3</sup>) but also the steepest profile ( $\sim$ 10 nm/dec. at 1.0×10<sup>19</sup> cm<sup>-3</sup>). These results mean that P diffusion is proper for TFET source region formation, as expected. However, As does not have so steep a profile as P. This result does not agree with that by Chui *et al.* [4]. We would think that this difference can comes from the influence of the implantation damages on the previous result [4]. The implantation damages may enhance As diffusion in the damage regions and yield the apparent As concentration dependency as a result of the enhanced diffusion coefficient.

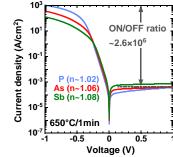

#### 3. Ge p-TFETs with source regions formed by SOG

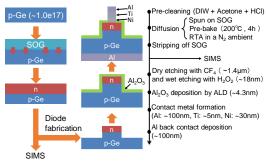

N-type (100) Ge substrates with a donor concentration of  $\sim 1.0 \times 10^{16}$  cm<sup>-3</sup> were used for TFETs. The fabrication process and the structure of the Ge TFETs are shown in Fig. 5. The RTA (1 min) temperature was 600 and 650 °C for P and 650 °C for Sb. An Al<sub>2</sub>O<sub>3</sub>(~2.5nm)/GeO<sub>x</sub>(~0.8nm)/Ge with plasma post oxidation gate stack was employed for reducing the MOS interface state density [5]. The measurements were performed with the source and substrate shorted.

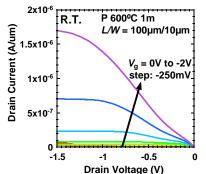

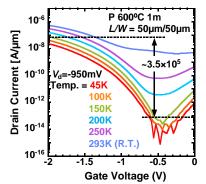

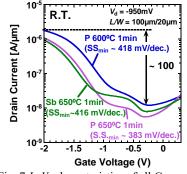

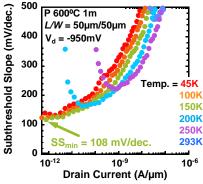

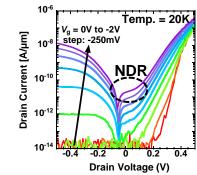

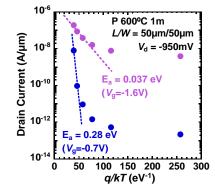

Fig. 6 shows the  $I_d$ - $V_d$  characteristics of a Ge p-TFET with P diffusion at 600°C. The high ON current of 1.7  $\mu$ A/ $\mu$ m was obtained at  $V_d$ =-1.5V and  $V_g$ =-2.0V. Fig. 7 shows the  $I_d$ - $V_g$ characteristics of all the Ge p-TFETs. P-TFETs with P diffusion at 600 °C exhibited the highest ON current due to the high impurity concentration and the steep impurity profile, though the ON/OFF ratio was low (~100) and  $SS_{min}$  was not low because of the high OFF current. Fig. 8 shows the  $I_d$ - $V_d$ characteristic of the Ge p-TFET with P diffusion at 600°C at 20K. The observed NDR-like characteristics indicate that the current is dominated by band-to-band tunneling (BTBT). Fig. 9 and 10 show the temperature dependence of  $I_{\rm d}$ - $V_{\rm g}$  and SS- $I_{\rm d}$ characteristics, respectively, of the TFET with P diffusion at 600°C. At 150 K, SS<sub>min</sub> of 108 mV/dec. and ON/OFF ratio higher than 3.5×105 were obtained. Under 150 K, SSmin is almost saturated around ~110mV/dec.. Fig. 11 shows the  $I_d$ q/kT characteristics of the TFET at  $V_{g}$ =-1.6 V and  $V_{g}$ =-0.7 V. The low (0.037 eV) and high (0.28 eV) activation energies were obtained at  $V_g$ =-1.6 V and -0.7 V, respectively. These results indicate that BTBT is dominant at  $V_g$ =-1.6V, while defect related thermal excitations can strongly affect the current at  $V_{g}$ =-0.7 V.

# 4. Conclusions

It has been found that P shows the highest impurity concentration ( $\sim 7 \times 10^{19}$  cm<sup>-3</sup>) and the steepest profile ( $\sim 10$ nm/dec. at  $1.0 \times 10^{19}$  cm<sup>-3</sup>) among solid-phase diffusion of P, As and Sb in Ge. We have demonstrated the operation of Ge p-TFETs with steep P profile source junctions formed by diffusion from SOG. SS<sub>min</sub> of 108 mV/dec. and ON/OFF ratio higher

# than $3.5 \times 10^5$ were observed at 150 K.

#### Acknowledgements

This work was supported by JST-CREST Grant Number JPMJCR1332, Japan.

## References

Table I

Diffusion condition used for SIMS and n<sup>+</sup>-p diode

Fig. 3 Chemical impurity profiles of n type dopants after 650°C/1min RTA

Fig. 9 The temperature dependence of  $I_{\rm d}$ - $V_{\rm g}$ characteristics of the Ge TFET with P diffusion at 600°C

Fig. 1 Fabrication process of samples for SIMS and n<sup>+</sup>p diode

+ SIMS

Fig. 4 Steepness of P profile vs P concentration after three RTA conditions

Fig. 7  $I_d$ - $V_g$  characteristics of all Ge TFETs

[1] A. Seabaugh et al., Proc. IEEE 98, 2095, 2010 [2] T. Krishnamohan et al., IEDM, pp. 947, 2008. [3] M. Noguchi et al., IEDM, pp. 683, 2013. [4] C.-O. Chui et al., Appl. Phys. Lett., 83, pp. 3275, 2003. [5] R. Zhang et al., IEEE TED, 59, 2, pp. 335, 2012.

Fig. 2 *I-V* characteristics of n<sup>+</sup>-p diodes after RTA at 650°C for 1min

Fig. 5 Fabrication process of the Ge TFET

Fig. 8 Id-Vd characteristics of the Ge TFET with P diffusion at 600°C at 20K

Fig. 11  $I_d$ -q/kT characteristics of the Ge TFET with P diffusion at 600°C at Vg=-1.6V and  $V_{g} = -0.7 V$