# Achieving BEOL footprint-efficient and low cost monolithic 3D<sup>+</sup> IoT chip using low thermal budget laser technology

Chih-Chao Yang<sup>1\*</sup>, Tung-Ying Hsieh<sup>1</sup>, Wen-Hsien Huang<sup>1</sup>, Jia-Min Shieh<sup>1</sup>, Hsing-Hsiang Wang<sup>1</sup>, Chang-Hong Shen<sup>1</sup>, Fu-Kuo Hsueh<sup>1</sup>, and Wen-Kuan Yeh<sup>1</sup>,

<sup>1</sup>National Nano Device Laboratories, No.26, Prosperity Road 1, Hsinchu 30078, Taiwan;

<sup>2</sup> Department of Electrical Engineering, National Tsing Hua University, Hsinchu, 30013, Taiwan;

\*Tel:+886-3-5726100-7565, Fax:+886-3-5722715, E-mail: samyang@narlabs.org.tw

#### Abstract

We have demonstrated a backend of line (BEOL) compatible  $3D^+$  IoT chip that monolithically integrate multi-functional logic and analog units, memories, sensors, energy harvester, and wireless-communication VCO (voltage- controlled oscillator). The sequentially stacked a-SiGeC TFPV device as an embedded ambient light energy harvester can provide electricity to the IoT circuits. The key to realize such miniaturized, self-powered, low cost, multi-functional  $3D^+$  IoT chip is to keep substrate temperature (T<sub>sub</sub>) lower than 400 °C using all low temperature and thermal budget laser processes.

## 1. Introduction:

Heterogeneous 3D integration that can connect multifunctional devices and circuits within a single chip is a promising technology for IoT application. However, conventional through silicon via (TSV) based 3D integration that relies on TSV or bump is more complex and costly. Monolithic 3D (M3D) integration seems a better solution for its higher connectivity, smaller form factor, and potential cost reduction. One example is the monolithic 3D NAND flash by stacking 64 layers of cell arrays [1]. For monolithic logic unit, we can be broadly classified into two groups: a) active layer transfer technology (e.g., CEA-Leti [2], IBM [3], Stanford niversity [4]) and b) direct active layer formation on a single wafer (e.g., AIST [5], UMC [6]).

We have demonstrated a monolithic  $3D^+IC$  using various low temperature and thermal budget laser processes  $(T_{sub} \le 400^{\circ}C)$  [7][8]. With these processes and integrated circuit design, we can sequentially integrate multifunctional devices, including logic and analog units, sensors, an energy harvester, a wireless-communication VCO (voltage-controlled oscillator), and a RRAM memory array. It paves the way for footprint efficient and low cost IoT chip fabrication.

## 2. 3D<sup>+</sup> device/circuit fabrication and 3D<sup>+</sup> IoT chip:

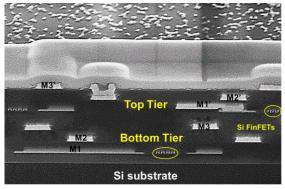

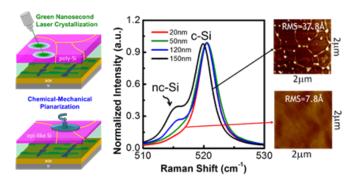

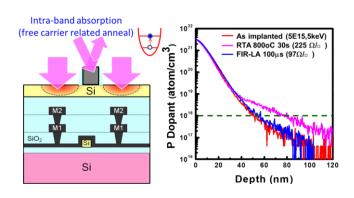

Our BEOL compatible monolithic 3D<sup>+</sup>IC with 3D stackable single-grained Si FET and multi-layered (M3-M3') tungsten (W) interconnects is illustrated in **Fig. 1**. We introduce three low thermal budget laser process to keep substrate temperature lower than 400°C for BEOL process integration. First, the green nanosecond laser ( $\lambda$ =532nm) helps to prepare large grain and highly crystallized poly-Si film. The following CMP and multi-step modification processes reduce surface roughness and enhance crystallinity of the channel (**Fig. 2**). Second, the far infrared ray laser anneal (FIR-LA,  $\lambda$ =10.6µm) is used to fully activate the

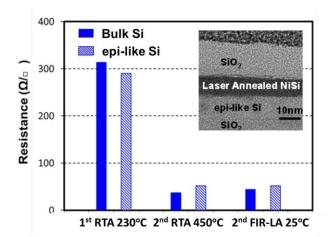

high doped and diffusionless source/drain region for scaling devices (**Fig. 3**). Third, two step laser-assisted self-aligned NiSi process with FIR-LA is proceeded for further reducing series and contact resistance of 3D stackable nano-devices (**Fig. 4**).

Fig. 1, FIB cross-section of two tiered monolithic  $3D^+$  IC.

Fig. 2, Illustration of green nano-second laser crystallization and CMP processes for highly crystallized Si channel preparation.

Fig. 3, Far infrared ray laser anneal for highly doped source/drain activation.

Fig. 4, Far infrared ray laser anneal for Salicide process.

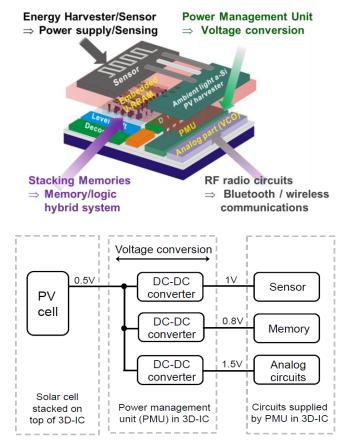

With these low thermal budget laser process, we demonstrated a self-powered fully functionalized monolithic  $3D^+$ -IC with light-electricity power management, wireless communication, and high density data-storage modules. The block diagram of the circuit are shown in **Fig. 5**. The a-SiGeC thin film photovoltaic (TFPV) serves as an ambient light energy harvester to generate electricity to the power management unit that converts the 0.5V PV source to three regulated power supplies for the memory, sensor, and radio-frequency (RF) circuits.

Fig. 5, Illustration and block diagram of the low-cost, low power, high driving current monolithic  $3D^+$  IoT chip including embedded non-volatile memory, communication device, and power controller.

#### **References:**

[1] K. Parat and C. Dennison" A Floating Gate Based 3D NAND Technology With CMOS Under Array" International Electron Devices Meeting (IEDM) Tech. Dig., p. 48, 2015.

[2] P. Batude, C. Fenouillet-Beranger, L. Pasini, V. Lu, F.Deprat, M. Cassé, B. Mathieu, B. Sklenard, F. Piegas-Luce, O. Billoint, O. Turkyilmaz, H. Sarhan, S. Sollier, J. Widiez, C. Tabone, M.-P. Samson, B. Previtali et al, "3D VLSI-CoolCube process: an alternative path to scaling", Symposia on VLSI Technology and Circuits (VLSI), p. 5-2, 2015.

[3] V. Deshpande, V. Djara, E. O'Connor, P. Hashemi, K. Balakrishnan, M. Sousa, D. Caimi, A. Olziersky, L. Czornomaz and J. Fompeyrine, "Advanced 3D monolithic hybrid CMOS with sub-50 nm gate inverters featuring replacement metal gate (RMG)-InGaAs nFETs on SiGe-OI Fin pFETs", International Electron Devices Meeting (IEDM) Tech. Dig., p. 209, 2015.

[4] Max M. Shulaker, Tony F. Wu, Asish Pal, Liang Zhao, Yoshio Nishi, Krishna Saraswat, H.-S. Philip Wong, Subhasish Mitra "Monolithic 3D Integration of Logic and Memory: Carbon Nanotube FETs, Resistive RAM, and Silicon FETs" International Electron Devices Meeting (IEDM) Tech. Dig., p. 638, 2014.

[5] Usuda, K. Kamata, Y. Kamimuta, Y. Mori, T. Koike, M. Tezuka, T. "High-performance tri-gate poly-Ge junction-less p- and n-MOSFETs fabricated by flash lamp annealing process", International Electron Devices Meeting (IEDM) Tech. Dig., p. 422, 2014.

[6] S. H. Wu, X. Y. Jia, M. Kui, C. C. Shuai, T. Y. Hsieh, H. C. Lin, D. Chen, C. B. Lin, J. Y. Wu, T. R. Yew, Y. Endo, K. Kato, and S. Yamazaki "Extremely low power C-axis aligned crystalline In-Ga-Zn-O 60 nm transistor integrated with industry 65 nm Si MOSFET for IoT normally-off CPU application", Symposium on VLSI Technology, pp. 58, 2016.

[7] C. C. Yang, J. M. Shieh, T. Y. Hsieh, W. H. Huang, H. H. Wang, C. H. Shen, F. K. Hsueh, P. Y. Hsieh, M. C. Wu and W. K. Yeh "Footprint-efficient and power-saving monolithic IoT  $3D^+$  IC constructed by BEOL-compatible sub-10nm high aspect ratio (AR>7) single-grained Si FinFETs with record high Ion of 0.35 mA/µm and steep-swing of 65 mV/dec and Ion/Ioff ratio of 8", International Electron Devices Meeting (IEDM) Tech. Dig., Sec. 9.1, 2016.

[8] F. K. Hsueh, C. H. Shen, J. M. Shieh, K. S. Li, H. C. Chen, W. H. Huang, H. H. Wang, C. C. Yang, T. Y. Hsieh, C. H. Lin, B. Y. Chen, Y. S Shiao, G. W. Huang, O. Y. Wong, P. Hung Chen, and W. K. Yeh, "First Fully Functionalized Monolithic 3D<sup>+</sup> IoT Chip with 0.5 V Light-electricity Power Management, 6.8 GHz Wireless-communication VCO, and 4-layer Vertical ReRAM", International Electron Devices Meeting (IEDM) Tech. Dig., Sec. 2.3, 2016.