# Enhanced-Mode InAs QWFETs with the Source Connected Field Plate Technique for Low Power Logic Applications

Jing-Neng Yao<sup>1</sup>, Yueh-Chin Lin<sup>2</sup>, Heng-Tung Hsu<sup>3</sup>, Ting-Jui Huang<sup>3</sup>, Min-Song Lin<sup>4</sup>, Ying-Chieh Wang<sup>2</sup>, Zhi-Yi Huang<sup>5</sup>, Simon M. Sze<sup>1</sup> and Edward Yi Chang<sup>1,2,3</sup>

<sup>1</sup> Department of Electronics Engineering, National Chiao-Tung University (NCTU).

1001 Ta Hsueh Road, Hsinchu 30010, Taiwan, R.O.C.

Phone: +886-986-659-775 E-mail: jimyao.ee01g@nctu.edu.tw

<sup>2</sup> Department of Materials Science and Engineering, National Chiao-Tung University (NCTU).

<sup>3</sup>International College of Semiconductor Technology, National Chiao-Tung University (NCTU).

<sup>4</sup>Institute of Photonics Technologies College, National Tsing Hua University (NCTU).

<sup>5</sup> Institute of Photonic System, National Chiao-Tung University (NCTU).

## Abstract

In this work, we present the enhanced mode InAs QWFETs with the source field plate technique for low power logic applications. Excellent SS value of 64.1 mV/dec, DIBL value of 44 mV/V and a very high Ion/IoFF ratio of  $2.4 \times 10^4$  were achieved. Meanwhile, the OFF-state current and the leakage current were 51%, and 64% suppressed, respectively, compared with the conventional InAs QWFETs.

## 1. Introduction

For post-CMOS, high electron mobility, III-V semiconductors have been the most promising materials for high performance and low power logic applications. The source connected field plate technique is used for AlGaN/GaN HEMTs to enhanced the power performance since this technique can not only smooth the electric field between the gate and drain and also reduce the leakage current. As the number of transistors in a microprocessor goes larger and larger, the leakage current issue becomes a much more severe problem for the low power logic application. Recently, many works of In<sub>x</sub>Ga<sub>1-x</sub>As based devices, like In<sub>0.53</sub>Ga<sub>0.47</sub>As QWMOSFETs and MOSFETs, have been widely investigated for low power logic applications.[1], [2] However, the leakage issue and the I<sub>ON</sub>/I<sub>OFF</sub> ratio are still the Achilles' heels of those reported lectures. It is little known that using the source connected field plate technique to improve the low power logic performance of the enhanced mode InAs quantum well field effect transistors (QWFETs). In this study, the enhanced mode InAs QWFETs with source connected field plate were studied to achieve excellent logic performance for low power logic applications.

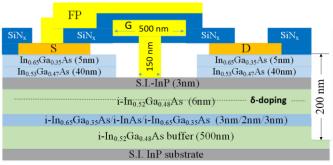

## 2. Device fabrication and measurement

The layer structure includes highly Si-doped,  $In_xGa_{1-x}As$  cap layers, an InP etch stop layer, an  $In_{0.52}Al_{0.48}As$  barrier layer, a Si planar doping layer, a thin  $In_{0.52}Al_{0.48}As$  spacer layer, and the  $In_{0.65}Ga_{0.35}As/InAs/In_{0.65}Ga_{0.35}As$  layers to improve the electron transport properties[3]. The device fabrication process includes mesa isolation, Ohmic metal deposition, silicon nitride passivation, gate recess, gate formation, and field plate structure. The device isolation was defined by

wet etch using an  $H_3PO_4$  base solution. Then, the non-alloy Ohmic metal (Ti/Pt/Au) was deposited and the source, drain spacing was  $3\mu$ m. The T-shaped gate was achieved using Ebeam lithography, and the Schottky gate metal (Pt/Ti/Pt/Au) was deposited. Finally, the source connected field plate was defined by E-beam lithography and the field plate metal (Ni/Au) was deposited by E-gun.

The electrical characteristics were measured by Agilent 4156C.

Fig. 1. Schematic of the source field plate InAs Quantum Well Field Effect Transistor.

#### 3. Results and discussions

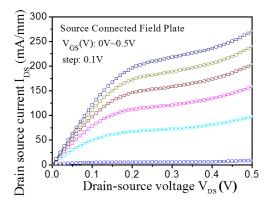

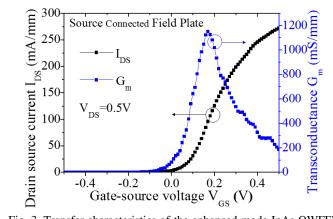

Fig. 2 shows the output characteristics (IDS-VDS curves) of the source connected field plate (SCFP) enhanced mode InAs QWFET. The maximum drain current ( $I_{DS}$  max) of the SCFP InAs QWFET was 272 mA/mm as the device drain voltage ( $V_{DS}$ ) and the gate voltage ( $V_{GS}$ ) were both biased at 0.5 V. Fig. 3. shows the transfer characteristics ( $I_{DS}$  vs.  $V_{GS}$ ) of the SCFP InAs enhanced mode QWFET. The maximum transconductance (Gm max) of the device was 1202 mS/mm at  $V_{DS}$ = 0.5V.

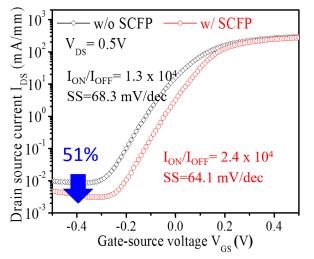

Fig. 4 compares the electrical characteristics (SS,  $I_{ON}/I_{OFF}$  ratio and the OFF-state current) of the enhanced mode InAs QWFETs with and without the SCFP at  $V_{DS}$ = 0.5V. The excellent value of subthreshold slope (SS) of the SCFP device is 64.1 mV/dec which is close to the ideal value of MOSFETs. For the SCFP InAs enhanced mode QWFET, the  $I_{ON}/I_{OFF}$  ratio is a high value of 2.4×10<sup>4</sup> which is higher than other In<sub>x</sub>Ga<sub>1-x</sub>As HEMTs owing to that the off-state current was effectively suppressed (51%) by the source connected field

plate technique. With an SCFP technique, the  $I_{ON}/I_{OFF}$  ratio was increased from  $1.3 \times 10^4$  to  $2.4 \times 10^4$ . Meanwhile, the subthreshold swing was also improved from 68.3 mV/dec to 64.1 mV/dec. The gate leakage was also reduced 64% (not shown here).

Fig. 2. DC characteristics of the enhanced mode InAs QWFET with source field plate ( $I_{DS}$ - $V_{DS}$  curves).

Fig. 3. Transfer characteristics of the enhanced mode InAs QWFET with source field plate at  $V_{DS}$ = 0.5V (I<sub>DS</sub> & Gm vs. V<sub>GS</sub>).

Fig. 4. SS &  $I_{ON}/I_{OFF}$  comparisons of the enhanced mode InAs with and without the source field plate technique at  $V_{DS} = 0.5$  V.

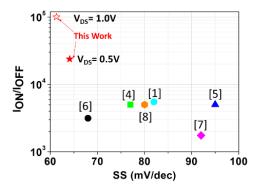

Fig. 5 shows the comparison of  $I_{ON}/I_{OFF}$  ratio as a function

of SS with other reported works of literature. Compared with other reports, the enhanced mode InAs QWFETs with the source connected field plate structure in this work demonstrated a high  $I_{ON}/I_{OFF}$  ratio of  $2.4 \times 10^4$  with pretty small SS value of 64mV/dec. As the  $V_{DS}$  was increased to 1.0V, the better performance was achieved with a  $I_{ON}/I_{OFF}$  ratio of  $1.0 \times 10^5$  and an extra low SS value of 61.3 mV/dec.

Fig. 5 Ion/IoFF vs. SS comparison of the normally-off SCFP InAs QWFET with other reported literature.[1], [4]–[8]

## 4. Conclusions

In this study, the enhanced mode InAs QWFETs with the source-connected field-plate structure were studied. The OFF-state current was 51% suppressed, and the gate leakage was 64% reduced compared with the conventional InAs QWFET. The excellent logic performance of SS = 64.1 mV/dec, DIBL = 44 mV/V and a high  $I_{ON}/I_{OFF}$  ratio of 2.4 ×10<sup>4</sup> were achieved. The results indicate that the enhanced mode InAs QWFETs with the source-connected field-plate is suitable for the low power logic applications.

#### Acknowledgements

This work was sponsored by NCTU-UCB I-RiCE program, Ministry of Science and Technology, Taiwan, under Grant No. MOST 106-2911-I-009-301. This work is particularly supported by "Aiming for the Top University Program" of the National Chiao Tung University and Ministry of Education, Taiwan, R.O.C

### References

- [1] X.Zhou et al., Symposium on VLSI Technology (VLSI Technology), pp. 166-167 (2014).

- [2] C. Y.Huang et al., International Electron Devices Meeting (IEDM), pp. 25.4.1-25.4.4 (2014).

- [3] E. Y.Chang, *et al.*, *Appl. Phys. Express*, vol. 6, no. 3, pp. 4–7 (2013).

- [4] S. Lee *et al.*, Symposium on VLSI Technology (VLSI Technology), pp. 54–55 (2014).

- [5] M. L.Huang et al., Symposium on VLSI Technology (VLSI Technology), no. 100, pp. T204–T205 (2015).

- [6] T.Vasen *et al.*, *Symposium on VLSI Technolgy (VLSI Technology)*, pp.160-161 (2016).

- [7] A.VThathachary et al., Symposium on VLSI Technolgy (VLSI Technology), T208-T209,(2015).

- [8] F.Xue et al., International Electron Devices Meeting (IEDM), no. 512, p. 27.5.1-27.5.4 (2012).