# First Study of High-Ge-Content Si<sub>0.16</sub>Ge<sub>0.84</sub> Gate Stack by Low Pressure Oxidation

Jun-Lin Zhang<sup>1</sup>, Wei-Li Lee<sup>1</sup>, Ming-Li Tsai<sup>1</sup>, Guang-Li Luo<sup>2</sup> and Chao-Hsin Chien<sup>1</sup>

<sup>1</sup> Development of Electronics Engineering and Institute of Electronics, National Chiao-Tung University

1001 University Road, Hsinchu 30010, Taiwan

<sup>2</sup> National Nano Device Laboratories, Hsinchu 30078, Taiwan

Phone: +886-3-5712121-54252 E-mail: chchien@faculty.nctu.edu.tw; glluo@narlabs.org.tw

#### Abstract

In this study, we employed low pressure oxidation (LPO) to achieve a high quality dielectric gate stack on high-Ge-content (HGC) Si<sub>0.16</sub>Ge<sub>0.84</sub>. We designed a Si-cap free passivation, and the interface trap density (D<sub>it</sub>) was reduced to  $5.1 \times 10^{12}$  eV<sup>-1</sup>cm<sup>-2</sup> by optimized process condition. X-ray photoelectron spectra of the interfacial layer (IL) showed that nearly GeO<sub>x</sub>-free IL was detected as 0.01 torr O<sub>2</sub> pressure at 600 °C was used. The gate leakage current in accumulation (V<sub>FB</sub>-1V) was also greatly reduced with EOT<1.5 nm. Finally, the mechanism of LPO oxidation of SiGe is proposed.

# 1. Introduction

HGC SiGe has been considered to be the promising material due to its high hole mobility and superior comparability with conventional Si substrate. However, forming the high quality passivation layer at SiGe surface remains challenges as undesired  $\text{GeO}_x$  creates high  $D_{it}$  in the bandgap [1-2]. Low pressure oxidation of SiGe surface is an effective method to suppress the  $\text{GeO}_x$  formation due to the difference in Gibb's free energy between SiO<sub>2</sub> and GeO<sub>2</sub> [3] and insufficient O<sub>2</sub> flux to react with the Ge atoms at SiGe surface [4].

In this study, we firstly demonstrate the high quality gate stack formed on HGC SiGe with the help of LPO process. We find that the composition of IL could be effectively controlled by temperature and pressure, and  $D_{it}$  value could be improved by this technique.

# 2. Experiment

Figures 1 (a) and (b) show the detailed process flow and MOSCAP structure. HGC Si<sub>x</sub>Ge<sub>1-x</sub> layer on relaxed Ge buffer layer was grown on low doped p-type Si (100) substrate by LPCVD system. The XRD analysis indicated that the Ge content of SiGe layer was approximately 0.84, as shown in Fig. 1(c). For the fabrication of MOSCAPs, the SiGe wafers were cleaned by diluted HF and DI water to remove native oxides. Then, we used LPO to form the  $GeO_x$ -free interfacial layer (IL), which the oxidation temperature and O<sub>2</sub> pressure were 400/600 °C and 0.3/0.01 torr, respectively. Subsequently, we used Plasma-Enhanced ALD (PE-ALD) to deposit 40 cycles HfO<sub>2</sub> at 250 °C. To improve the quality of gate stack, the post deposition annealing (PDA) in N2 ambient was used at 300 °C for 1 minute. For the gate electrode, TiN was sputtered and patterned using lift-off process. Finally, Ti/Al was deposited on the backside of wafer as the body contact. **Fig.1 (d)** shows the cross-sectional TEM image of the MOSCAP.

### 3. Results and Discussion

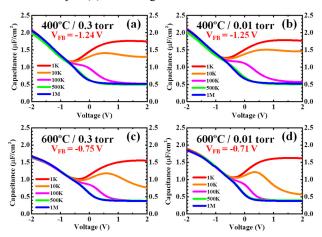

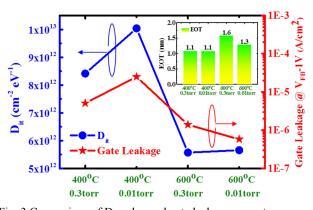

First, we investigated the effect of temperature and pressure on Si<sub>0.16</sub>Ge<sub>0.84</sub> surface oxidation. **Fig. 2** shows the multi-frequency Capacitance-Voltage (C-V) characteristics of the TiN/HfO<sub>2</sub>/IL/SiGe. The cases of 600 °C with two pressure conditions showed the smaller hump in the depletion and weak inversion regions, and the 600 °C/0.01 torr case depicted the least hump than other cases. **Fig. 3** shows the D<sub>it</sub> value extracted by conductance method and the MOSCAP gate leakage current with the inset of equivalent oxide thickness (EOT). It revealed that the value of D<sub>it</sub> was effectively reduced with higher temperature and lower O<sub>2</sub> pressure. Moreover, the gate leakage current in accumulation (V<sub>FB</sub>-1V) of 600 °C/0.01 torr case was around 1 order of magnitude smaller than other cases with a relatively moderate EOT (approximately 1.3 nm).

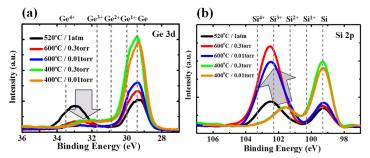

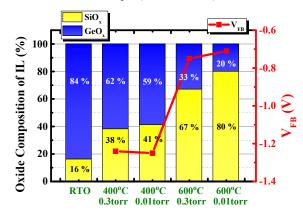

Next, we examined the XPS spectra of Si2p and Ge3d core levels, as illustrated in Fig. 4. As the temperature increased from 400 to 600 °C, the binding energy of Si-O bonds were increased, indicating that more stable oxide states (Si<sup>3+</sup>, Si<sup>4+</sup>) were formed in the IL. The growth of GeO<sub>x</sub> was effectively suppressed with decreasing O<sub>2</sub> pressure from 1 atm to 0.01 torr. In addition, we extracted the percentage of SiO<sub>x</sub> and GeO<sub>x</sub> in the IL by using the peak area and relative sensitivity factor, as shown in Fig. 5. It suggested that the case of 600 °C/0.01 torr possessed a higher SiO<sub>x</sub> composition with a relatively low GeO<sub>x</sub> formation in the IL, which could result in the reduction of D<sub>it</sub> value and significant decrease of gate leakage current. Moreover, the reason of V<sub>FB</sub> shift was possibly due to the change of dipole charge and oxide charge, which might be attributed to the increase of Ge concentration at the interface.

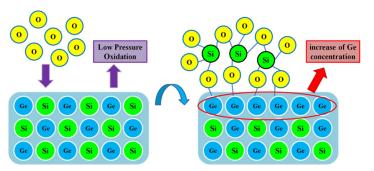

**Figure 6** shows the speculated schematic illustration of LPO process in the IL formation. During the LPO process, silicon is selectively oxidized leaving behind Ge atoms at the IL/SiGe interface; therefore, if more Si atoms participate in the oxidation reaction, the Ge concentration near the SiGe surface will increase significantly, which evidences that the preferable  $SiO_x$  concentration is controllable by using the LPO.

# 4. Conclusions

We firstly investigate the LPO to improve the properties

of  $\mathrm{Si}_{0.16}\mathrm{Ge}_{0.84}$  gate stack with moderate EOT  ${<}1.5$  nm and low gate leakage current while it greatly reduces the D<sub>it</sub> value (5.1x10<sup>12</sup> eV<sup>-1</sup>cm<sup>-2</sup>). The XPS spectra showed that preferable higher SiO<sub>x</sub> composition with lower GeO<sub>x</sub> composition in the IL is controllable by using the LPO. The LPO process is a promising approach to be applied on HGC SiGe channel MOSFETs.

#### Acknowledgement

Grant MOST This work was supported by 105-2119-M-009-004 from the Ministry of Science and Technology, Taiwan.

#### References

[1] N. Collaert et al., SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), 2015 IEEE.

[2] C. H. Lee et al., IEEE Symposium on VLSI Technology, 2016. [3] C. T. Chang et al., Tech. Dig. Int. Electron Devices Meet. 2015, 584.

[4] Rabie et al., J. Appl. Phys. 2005, 98,074904.

67 68 69

Omega (20)

Fig. 1 (a) Process flow and (b) schematic structure of the MOSCAPs. (c) XRD spectra for the HGC Si<sub>x</sub>Ge<sub>1-x</sub> layer grown on relaxed Ge layer. (d) TEM image of the MOSCAP.

Fig. 2 C-V characteristics of the TiN/HfO2/IL/SiGe MOSCAPs

with conditions of (a) 400 °C/0.3 torr (b) 400 °C/0.01 torr (c) 600 °C/0.3 torr (d) 600 °C/0.01 torr, respectively.

Fig. 3 Comparison of D<sub>it</sub> value and gate leakage current. Inset: Corresponding EOT of MOSCAPs extracted by C-V curve.

Fig. 4 XPS spectra of (a) Si 2p and (b) Ge 3d of the IL by LPO on SiGe substrate and control sample (520 °C / 1 atm).

Fig. 5 IL composition on Si0.16Ge0.84 determined by XPS curve fitting and VFB extracted by C-V curve.

Fig. 6 Illustrative cartoon of the LPO process in the IL formation.