# RTA-Temperature Dependence of Electrical Characteristics of PVD-TiN Metal Gate SOI-MOSFETs Fabricated on Half-Inch Minimal Wafers

Yongxun Liu<sup>1</sup>, Kazushige Sato<sup>2</sup>, Hiroyuki Tanaka<sup>1, 2</sup>, Kazuhiro Koga<sup>2</sup>, Sommawan Khumpuang<sup>1, 2</sup>, Masayoshi Nagao<sup>1</sup>, Takashi Matsukawa<sup>1</sup>, and Shiro Hara<sup>1, 2</sup>

<sup>1</sup> Nanoelectronics Research Institute (NeRI), National Institute of Advanced Industrial Science and Technology (AIST)

1-1-1 Umezno, Tsukuba, Ibaraki 305-8568, Japan, Phone: +81-29-861-3417, E-mail: yx-liu@aist.go.jp

<sup>2</sup> Minimal Fab General Incorporated Association (MINIMAL), 1-1-1 Umezono, Tsukuba, Ibaraki 305-8568, Japan

#### Abstract

PVD-TiN metal gate MOSFETs and CMOS ring oscillators have successfully been fabricated by using gate-first process on half-inch minimal SOI wafers with different RTA-temperatures ( $T_R$ 's), and the  $T_R$  dependence of their electrical characteristics have systematically been investigated. It was found that a positive shift of threshold voltage ( $V_t$ ), a smaller  $V_t$  variation and an enhanced electron mobility are observed with reducing  $T_R$ . Moreover, the successful operation of a 561-stage CMOS ring oscillator with a gate length ( $L_g$ ) of 0.36 µm has been demonstrated.

#### 1. Introduction

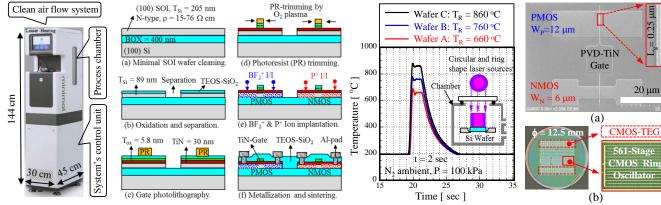

The minimal-fab concept was proposed in the early 2008 for producing low volume custom devices with a low investment cost [1]. After the proposal of minimal-fab concept, many kinds of minimal-fab machines have been developed rapidly, as shown in Fig. 1. Meanwhile, the spin on dopant (SOD) thermal diffusion based gate-last process has also actively been promoted using the developed minimal-fab machines [2-4]. In this work, we develop gate-first process using the minimal-fab leaser heating machine combined with mega-fab ion implantation (I/I), and fabricate PVD-TiN gate MOSFETs and CMOS ring oscillators on the half-inch minimal SOI wafers with different RTA-temperatures ( $T_R$ 's).

# 2. Device Fabrication

In the device fabrication, we used half-inch minimal SOI wafers, as shown in Fig. 2(a). First, thermal oxidation and device separation were performed to fabricate fully depleted (FD) SOI islands, as shown in Fig. 2 (b). Then, a 5.8-nm-thick gate oxide (Tox) layer formation, a 30-nm-thick PVD-TiN and a 100-nm-thick TEOS-SiO<sub>2</sub> layers deposition were continually carried out. To fabricate submicron gate patterns using conventional minimal-fab maskless exposure machine, we introduced over-expose and O<sub>2</sub> plasma techniques, as shown in Figs. 2(c) and 2(d). Submicron gates were successfully fabricated by RIE of TEOS-SiO<sub>2</sub> layer and wet etching of PVD-TiN layer, as shown in Fig. 4(a). After the gate formation, BF2<sup>+</sup> I/I for PMOS and P<sup>+</sup> I/I for NMOS were carried out separately using the same I/I conditions of dose =  $1.5 \times 10^{15}$  cm<sup>-</sup>  $e^2$ , energy = 10 keV, tilt = 0°, and twist = 0°, as shown in Fig. 2(e). After a 145-nm-thick TEOS-SiO<sub>2</sub> layer deposition, RTA was performed with different T<sub>R</sub> values but with the same time of 2 sec for different sample wafers using minimal-fab laser heating machine, as shown in Fig. 3. By using above I/I and RTA conditions, we also confirmed impurity activation with bulk Si wafers. Finally, conventional metallization and sintering were performed, as shown in Fig. 2(f). Figure 4(b) shows the photo-image of the process finished half-inch minimal SOI wafer that includes CMOS-TEG areas and 561stage CMOS ring oscillators, and so on.

# **3. Electrical Characteristics**

To investigate the  $T_R$  effect on electrical characteristics,

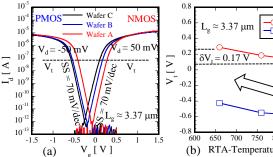

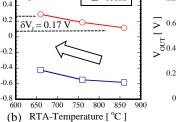

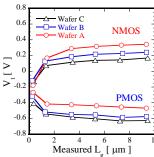

we evaluated  $I_d$ - $V_g$  characteristics of the fabricated MOSFETs with almost the same  $L_g$  of 3.37 µm on different sample wafers, as shown in Fig. 5(a). Note that almost the symmetrical  $I_d$ - $V_g$  curve is observed in the MOSFETs on wafer-A. Figure 5(b) shows  $V_t$  as a function of  $T_R$ . It is clear that a positive  $V_t$  shift is observed with reducing  $T_R$  and the  $V_t$  values of the MOSFETs on wafer-A are close to those in the case of gate-last process without RTA [3, 4]. This result indicates that work function of PVD-TiN gate approaches to that of as deposited one with reducing  $T_R$  lower than 660 °C [5]. As a result, the CMOS inverter fabricated on wafer-A shows better transfer characteristics than others, as shown in Fig. 6. Moreover, the  $V_t$  roll-off in MOS and roll-up in PMOS are observed at a submicron gate region, as shown in Fig. 7. Such short channel effects (SCE) can be improved by introducing source-drain (SD) extension regions and the gate sidewall.

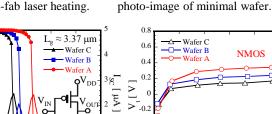

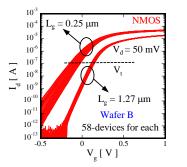

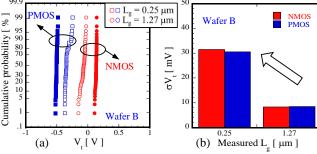

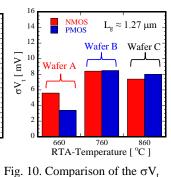

To investigate  $V_t$  variations, we evaluated 58-devices on etch sample wafer. As an example, Fig. 8 shows the I<sub>d</sub>-V<sub>g</sub> characteristics of the fabricated L<sub>g</sub> of 0.25 and 1.27  $\mu$ m NMOSFETs on wafer B, and the measured statistical V<sub>t</sub> variations are shown in Fig. 9. Note that  $\sigma V_t$  increases with scaling down device size owing to the large L<sub>g</sub> fluctuation caused by submicron gate formation. Figure 10 compares the  $\sigma V_t$ values of the fabricated MOSFETs with almost the same L<sub>g</sub> of 1.27  $\mu$ m on different sample wafers. It is clear that the smallest  $\sigma V_t$  is observed in the fabricated MOSFETs on wafer A with the lowest T<sub>R</sub> among three sample wafers.

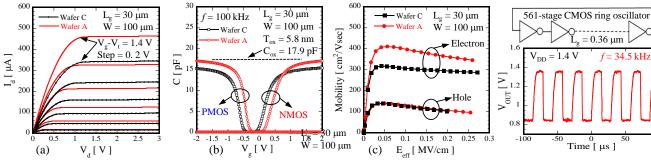

To evaluate effective mobility, we also fabricated large size MOSFETs with  $L_g = 30 \mu m$  and  $W = 100 \mu m$ . It is clear from Fig. 11 that a higher drain current, a large capacitance and an enhanced electron mobility are observed in the NMOSFET on wafer-A than those on wafer-C. The performance degradation in the MOSFETs on wafer-C should be resulted from the nitrogen atoms pile-up near the channel surface in  $T_{ox}$  layer due to the high  $T_R$  [5]. Figure 12 shows the oscillation wave form of the fabricated 561-stage CMOS ring oscillator with  $L_g = 0.36 \mu m$ . This result means that submicron gate 1122-transistors are operated simultaneously.

# 4. Conclusions

We have fabricated and characterized PVD-TiN gate SOI-MOSFETs with different  $T_R$  values. It was found that  $T_R$  of 660 °C is suitable for the fabrication of PVD-TiN gate CMOS, and the higher  $T_R$  than 660 °C results in device performance degradation. Moreover, the successful operation of a 561-stege CMOS ring oscillator has been demonstrated. This indicates that CMOS integrated circuits can be fabricated using the developed gate-first minimal-fab process.

#### References

[1] S. Hara et al., J. Jpn. Precis. Eng., 77, No. 3, (2011) 249. [2] S. Khumpuang and S. Hara, IEEE Trans. Semicond. Manuf., 28, NO. 3, (2015) 393. [3] Y. X. Liu et al., IEEE Int. Conf. Nanotechnology, Dig., (2016) 802. [4] Y. X. Liu et al., Jpn. J. Appl. Phys. 56, (2017) 06GG01. [5] Y. X. Liu et al., Jpn. J. Appl. Phys. 47, (2008) 2433.

Fig. 1. Photo-image of the developed minimal-fab machine.

Fig. 2. Ion implantation (I/I) based gatefirst device fabrication process flow for the PVD-TiN metal gate SOI-CMOS.

-O-- NMOS ----- PMOS

Fig. 3. RTA-temperature  $(T_R)$ Fig. 4. (a) SEM of CMOS pattern profiles of the wafers by using after TiN gate formation, and (b) minimal-fab laser heating.

Fig. 5. (a) I<sub>d</sub>-V<sub>g</sub> characteristics of the fabricated SOI-MOSFETs Fig. 6. Transfer characteristics of Fig. 7. V<sub>t</sub> as a function of L<sub>g</sub> for with almost the same  $L_g$  of 3.37  $\mu m$  on the different sample wafers, and (b)  $T_{R}$  dependence of the threshold voltage (V<sub>t</sub>).

Fig. 8.  $I_d$ - $V_g$  characteristics of the fabricated NMOSFETs with different  $L_{\rm g}$  values of 0.25 and 1.27  $\mu m.$

0.8

0.2

0.4 V<sub>IN</sub> [ V ]

the different sample wafers.

the fabricated CMOS inverters on the fabricated SOI-MOSFETs on the different sample wafers.

of the fabricated SOI-MOSFETs

with different T<sub>R</sub> values.

Fig. 9. (a) Statistical V<sub>t</sub> variations and (b)  $\sigma$ V<sub>t</sub> values of the fabricated MOSFETs with different L<sub>g</sub> values of 0.25 and 1.27  $\mu$ m.  $\sigma$ V<sub>t</sub> increases with scaling down L<sub>o</sub>.

Fig. 11. Comparison of electrical characteristics between the fabricated large size MOSFETs on wafer- Fig. 12. Oscillation wave A and wafer-C. (a) I<sub>d</sub>-V<sub>d</sub> characteristics of NMOSFETs at the same V<sub>g</sub>-V<sub>t</sub>, (b) split C-V characteristics, form of the fabricated 561and (c) effective mobility. Electron mobility enhancement is observed in the NMOSFET on wafer-A.

stage CMOS ring oscillator.