# A Novel Experimental Approach to Extracting Negative Capacitances: Newly found Negative DIBL Effect in 14nm NC-FinFET and the Way to Achieve Hysteresis-free

Y. C. Luo<sup>1</sup>, E. R. Hsieh<sup>2</sup>, C. J. Su<sup>3</sup>, Steve S. Chung<sup>2</sup>, T. P. Chen<sup>4</sup>, S. A. Huang<sup>4</sup>, T. J. Chen<sup>4</sup>, and Osbert Cheng<sup>4</sup> <sup>1</sup>Department of Electrical Engineering, National Tsing Hua University, Taiwan, <sup>2</sup>Department of Electronics Engineering, National Chiao Tung University, Taiwan, Taiwan, <sup>3</sup>National Nano Device Laboratories(NDL), Taiwan, <sup>4</sup>United Microelectronics Corporation (UMC), Taiwan

Abstract- For the first time, we have developed experimental approaches to quantitatively extracting negative capacitance and revealing a new negative DIBL effect in NC- FinFET. From this method, the growth mechanism of ferroelectric HZO can be well explained. It was found that DIBL with NC effect decreases along with the increase of  $V_{ds}$ . Furthermore, we found  $\sigma V_t$  dramatically reduced with NC effect in addition to the S.S. reduction. For body effect, in the presence of NC effect, NC effect increases sensitivity so that hysteresis of NC-FinFET can be eliminated. In addition to a steeper SS of NC-FinFET, our work has proven that by suitably choosing body bias, NC-FinFET can not only help to improve the short-channel effect but also exhibit hysteresis-free, which makes it more applicable in low-power and high-performance apps in the future.

### **1. Introduction**

NC-FET has become one of the most promising low-power transistors with high performance in IoT and HPC. NC-FET offers steep SS(< 60mV/dec) experimentally[1-3]. Nano- fabrication which NC-FETs require is compatible with that of the mainstream FinFET technology [4-5]. However, the negative capacitance values have not been quantitatively characterized till now although NC behavior can be indirectly observed in SS or CV. Furthermore, in addition to NC effect, a ferroelectric thin film is usually accompanied by a hysteresis, which increases tremendous complexity to circuit designs [2, 6]. In this work, we aim to develop an experimental approach to directly extracting NC values and examining the short-channel and body effects of an HZO MIM gated FinFET, from which zero hysteresis operation of NC-FET can be achieved. The experimental methods will also be used to extensively investigate the  $\sigma V_{th}$ , SS, DIBL, I<sub>off</sub>, and body sensitivity on the fabricated 14nm HZO-gated FinFET. The results in this work will provide very valuable on understanding more device physics of NC effect so as to design appropriate electrical characteristics of NC-FinFET.

#### **2. Device Preparation**

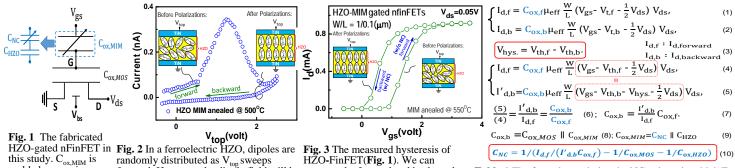

TiN/HZO(9nm)/TiN samples whose area=  $100\mu m^2$  were prepared in annealing temperature from  $400^{\circ}C$  to  $700^{\circ}C$ . The FinFET is based on the UMC 14nm technology platform. MIM is then electrically connected to the gate of 14nm-nFinFET with W/L=1/0.1 (µm) for the whole measurement. (Fig.1)

#### 3. Results and Discussions

#### A. Approaches to Experimentally Extracting NC Values

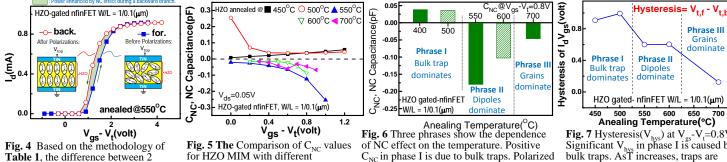

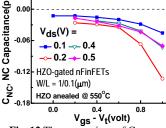

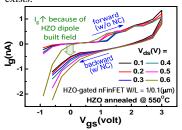

Fig. 1 is the experimental setup. When  $V_{gs}$  is applied on MIM, HZO will modulate the channel carriers of the transistor. In the presence of NC-effect, it is assumed that effective negative capacitance( $C_{NC}$ ) will be serially connected to HZO MIM cap( $C_{HZO}$ ). In Fig. 2, we observe flip-flops of bulk dipoles in an HZO MIM. Before voltage sweeps, bulk dipoles are randomly distributed. But, as external bias is across MIM, bulk dipoles will be aligned in an opposite direction to this external field. As a result, a built-in field of dipoles is polarized and induces NC effect. From this observation, we expect NC effect appears during the backward sweep but not for the forward one. Therefore, in a gated HZO-FinFET, Fig. 1, we should observe corresponding forward and backward routes of  $I_dV_{gs}$  as in Fig. 3. The forward route of Fig.3 is  $I_dV_{gs}$  without NC effect, while the backward is  $I_dV_{gs}$  with NC effect, from which we see the hysteresis. It should be noted that NC effect from UZO only affect of a FinFET; by storaging that NC effect from HZO only affects Cox of nFinFET; hysteresis just influences  $V_t$ , and  $\mu_{eff}$  will not respond to remote scattering events from HZO because of filed-screening from gate metals. Therefore, we extract C<sub>NC</sub> in HZO MIM by the derivations in Table 1. In Fig. 4, it is of interest to find that the current of backward route is higher than the forward one, which is an evidence showing NC-effect on  $I_d V_{gs}$  of nFinFET. B. Effects of Annealing Temperatures on HZO MIM

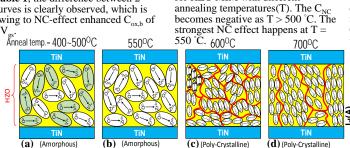

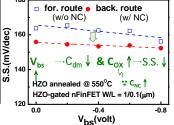

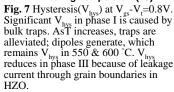

We show  $C_{NC}$  of HZO-gated nFinFET at different annealing temperatures(T) of HZO (Fig.5). Fig. 6 is the result of Fig. 5. Under the condition at  $V_{gs}$ - $V_t$ =0.8V, as T< 550°C,  $C_{NC}$  is positive, but it turns to be negative as T> 550°C, which means NC effects just happen when T > 550°C. However, after 550°C,  $C_{NC}$  decays inversely. On the other hand, in Fig. 7, hysteresis ( $V_{hys}$ ) is the largest as T<550°C and maintains a relatively higher level at T= 550°C ~600°C but decays quickly while T>700°C. To explain  $C_{NC}$ and  $V_{hys}$  obtained in Figs. 6 and 7, we divide T into 3 phases (Fig. 8). At phase I, T<550°C, bulk traps( $V^{2+}$ ) dominate in HZO.  $V^{2+}$ - $O^{2-}$  will induce dipole charges, in addition to few bulk dipoles, resulting in a significant  $V_{hys}$ . However,  $V^{2+}$ - $O^{2-}$  cannot contribute to NC effect. Thus,  $C_{NC}$  is positive in phase I. As T rises to 600°C, phase II, higher T passivates bulk traps and helps to generate more bulk dipoles, resulting in the occurrence of negative  $C_{NC}$ . Thanks to elimination of bulk traps,  $V_{hys}$  starts to decrease. When T > 600°C (phase III), the amorphous state of HZO changes into polycrystalline and grains form. Leakage current flows easily polycrystalline and grains form. Leakage current flows easily through boundaries, and  $C_{NC}$  and hysteresis drops at T= 700<sup>o</sup>C.

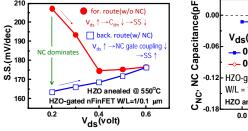

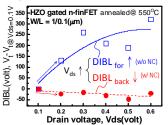

## C. Short-channel Effect of NC-FinFET

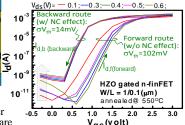

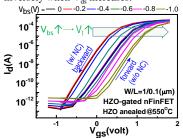

Fig. 9 shows  $I_dV_{gs}$  of HZO-gated nFinFET.  $\sigma V_t$  of the backward route is much smaller than that of forward one since a dipole built-in field of HZO enhances gate controllability of nFinFET. Moreover, DIBL of backward route decays with increasing  $V_{ds}$ , which is a typical NC effect. (Fig. 10) SS of back-branch  $I_dV_{gs}$  also improves owing to NC effect, but SS slowly increases along with  $V_{ds}$  because a higher  $V_{ds}$  reduces the gate coupling of HZO so as to decay the NC effect (Fig. 12). Then, in Fig. 9, I<sub>off</sub> of the backward route is clearly larger than that of the forward one because the dipole built-in field of HZO increases gate leakage (Fig.13). As a result, NC effects strengthen short-channel effect not only in a smaller SS but also a better  $\sigma V_t$ and a negative DIBL effect. However, Ioff increases as a drawback. D. Body Effect of NC-FinFET

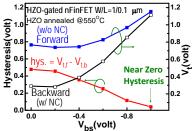

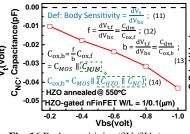

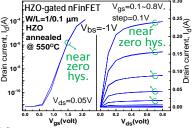

By applying a larger  $V_{bs}$ , we can observe a shift of  $V_t$  which is a classical body effect (Fig. 14). Fig. 15 shows  $V_t$  trend of forward and backward routes as function of  $V_{bs}$ . Compared to that of forward route, Vt increase of backward route is more sensitive to  $V_{hs}$ , resulting in a decrease of hysteresis, which even approaches zero. In addition to the extraction of negative  $C_{NC}$ , we developed another approach to obtain  $C_{NC}$  by body sensitivity  $(\delta V_t/\delta V_{bs}=C_{dm}/C_{ox})$ . The results have shown that  $C_{NC}$  becomes more negative as  $V_{bs}$  boosts (Fig. 16). Furthermore, SS of the backward branch with the investor  $S_{NC}$ backward branch with the increase of  $V_{bs}$  is steeper than that of the forward one since a lower  $C_{dm}$  induced by body biases and a higher  $C_{ox}$  caused by NC effects (Fig. 17). Since hysteresis can be excluded by a suitable  $V_{bs}$ , by taking this benefit, a near hysteresis-free can be achieved, Fig. 18.

In summary, we have developed simple approaches to successfully characterizing negative capacitances in an HZO-gated FinFET. An appropriate annealing temperature  $(550^{\circ}C)$  is necessary to create NC effect inside HZO, which can be well explained by growth mechanisms of HZO. In terms of the short-channel effect, we clearly observed negative DIBL effect. Moreover, new findings include:  $\sigma V_t$  is dramatically suppressed but  $I_{off}$  enlarges reversely as NC effect appears. Moreover, we can achieve a hysteresis-free NC-FET by applying a suitable  $V_{bs}$ . Furthermore,  $V_{bs}$  was also reduced S.S. Through these efforts, device physics of NC- FinFET can be well-understood, which will be helpful for design and fabrication of chips with ultra-low power and high performance in a near future.

Acknowledgments This work was support in part by the *Ministry of Science and Technology, Taiwan,* under *Research of Excellence program contract No. 107-2633-E009-003.*

References: [1] K. S. Li, et al., IEEE IEDM, p. 620, 2015. [2] E. Ko, et al., IEEE EDL, p. 418, 2017. [3] A. Rusu, et al., IEEE IEDM, p. 395, 2010. [4] T. S. Böscke, et al., APL, p. 102903, 2011. [5] K. Mistry, et al., IEEE IEDM, p. 247, 2007. [6] W. X. You, et al., IEEE TED, p. 3476, 2017.

this study.  $C_{ox,MIM}$  is molded as a series connection of  $C_{HZO}$  (ferroelectric cap.) and C<sub>NC</sub>(NC cap.)

Fig. 2 in a reflected in Lies, supers at the forward and by distributed as  $V_{top}$  sweeps forward. However, the dipole field will be separate the forward and backward built and polarized when  $V_{top}$  sweeps backward. As a result, NC effect exists forward) and  $I_d V_{gs}$  w/ NC effect(the forward) and I\_d V\_{gs} w/ NC effect (the forward) and I\_d V\_{gs} w/ NC effect(the forward) and I\_d V\_{gs} w/ NC effect (the forward) and I\_d V\_{gs} w/ NC e when polarized in the backward direction. backward).

Table 1 The formulas to derive the NC values, in which Eq (10) can be calculated from the measred forward, backward currents, and the NC effect and the respective ferroelectric and transistor capacitances.

Fig. 4 Based on the methodology of Table 1, the difference between 2 curves is clearly observed, which is owing to NC-effect enhanced  $C_{ox,b}$  of I<sub>d</sub>V

Fig. 8 (a) Both vacancies(bulk traps),  $V^{2}$ - $O^{2}$  and  $Zr^{2}$ - $O^{2}$  dipoles exist in HZO when annealing temperature(T) = 400 °C ~500 °C. Amount of the former is larger than that of the latter. As a result, hysteresis is serious. (b) As T increases, traps are passivated, and Zr2+-O2- dipoles generate while T=550 °C. Therefore, NC effect can be observed as T>550 °C. (c) As T further increases, the phrase of HZO gradually changes from amorphous to poly-crystalline; grains form in HZO as T approaches 600 °C. (d) Grains grow even larger when T reaches 700 °C. The leakage can flow through boundaries, in terms of reduction of both  $C_{NC}$  &  $V_{hys}$ . 210

Fig. 11 Without NC, S.S. of the backbranch is steeper than that of the forone w/o NC, but it slowly increases as  $V_{ds}$  ramps because the NC gate coupling effect is reduced when  $V_{ds}$  increases.

**Fig. 15** Body sensitivity  $(\delta V_t / \delta V_{bs})$  of the backward with NC is more sensitive than that of the forward without NC such that hysteresis reaches zero at a larger V<sub>bs</sub>.

**Fig. 12** The comparison of  $C_{NC}$  as function of  $V_{ds}$ , it is double confirmed that  $C_{NC}$  decreases when  $V_{ds}$  is raised because of the reduction for gatecoupling of  $C_{\rm NC}$  to the channel.

Fig. 16 Body sensitivity  $(\delta V_t / \delta V_{bs}) =$  $C_{dm}^{\prime}/C_{ox}^{\prime}$ . We can directly extract  $C_{NC}^{\prime}$  as function of  $V_{bs}$  through the body sensitivity.  $C_{NC}^{\prime}$  increases as  $V_{bs}$  is raised.

of NC effect on the temperature. Positive C<sub>NC</sub> in phase I is due to bulk traps. Polarized dipoles in HZO MIM result in significant negative  $C_{NC}$  in phase II. Reduced negative  $C_{NC}$  in phase III caused by leakage current through grain boundaries in HZO bulk.

**Fig. 9** The comparison of  $I_dV_{gs}$  for different  $V_{ds}$ :  $I_{d,b}$  with NC effect exhibits a better  $\sigma V_{th}$  than  $I_{d,f}$  without NC, in terms of a better short channel effect. But however, with NC effect, it decays  $I_{off}$  increases reversely when NC effect exists

Fig. 13 In Fig. 9, it was observed that. w/NC, the  $I_{off}$  increases, which can be well explained that the electric field built by dipoles inducing the gate leakage of nFinFET.

**V**<sub>bs</sub>(volt) **Fig. 17** The larger  $V_{bs}$  is, the smaller S.S. becomes, owing to reduced  $C_{dm}$  and increased  $C_{ox}$ . The former is a body effect; the latter is because  $C_{NC}$  enlarges as  $V_{bs}$  is raised.

Phrase III dominate HZO gated- nfinFET W/L = 1/0.1(µm)

Fig. 10 The comparisons of DIBL for the forward and backward. Without the NC effect, the DIBL increases as V<sub>ds</sub> raises; inversely when  $V_{ds}$  increases.

Fig. 14 The comparison of  $I_d V_{gs}$  w/o NC(forward) and w/ NC(backward) as function of  $V_{\rm bs}$ . The typical body effect has been observed. The larger the  $V_{\rm bs}$  is, the higher the V<sub>t</sub> becomes.

Fig. 18, The body bias can be applied to achieve a zerohysteresis and a low Ioff leakage.