# Stochastic Simulation of Breakdown Process for High-k Dielectrics

Wei Liu, Bing Chen, Shifan Gao, Zejie Zheng and Yi Zhao\*

College of Information Science and Electronic Engineering, Zhejiang University, Hangzhou, China \*E-mail: yizhao@zju.edu.cn

## Abstract

We developed a new toolkit for simulating the breakdown behaviors of high-k dielectric using Monte Carlo method. The simulation is performed by considering the microscopic migration of oxide vacancies (Vo). The impact of Vo-generation barrier energy and Vo-migration barrier energy is investigated. Both the cases of four migration directions and eight migration directions are studied in our simulation. The results show that the treatment of eight migration directions is more reasonable by considering the experimental reports in literatures. The toolkit developed in this work can be used for studying the breakdown process in high-k gate dielectrics in MOS transistors and the set/reset process of resistive switching layers in RRAM.

## 1. Introduction

The integrated circuit based on CMOS transistors is the building block of the information evolution in the past decades. According to Moore's law, the gate length of MOS transistors is scaling down for several decades. However, this scaling is expected to be approaching to its physical limit, and to scale the transistor further, high-k gate dielectric has been used to replace SiO<sub>2</sub> to suppress the sever gate leakage current. Even though lots of studies about high-k gate dielectrics have been conducted, some important issues about the reliability of high-k gate dielectrics, like breakdown process are not totally understood [1]. On the other hand, high-k dielectrics (HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> et al.) are also widely studied in other applications, like RRAM devices.

Since in both the cases of transistors and RRAM devices, there will be a large electrical field through the dielectric, understanding the breakdown behaviors is critical. In the microscopic model, the breakdown process in high-*k* dielectrics is studied by considering the oxygen vacancy forming and transfer under electrical fields [2-3]. This is because usually there are amounts of oxygen vacancies in a high-*k* dielectric due to its ionic oxide character.

In this work, we simulated the breakdown behavior of high-k dielectric by constructing a 2-D resistor network. The I-V characteristic between two Vo sites is linear. Otherwise, the I-V characteristic of two resistors is described as [4-6]:

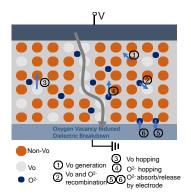

$$I = \frac{\sinh(\alpha U)}{R} \tag{1}$$

$$P \propto e^{-\beta(E - \Delta \varphi)} \tag{2}$$

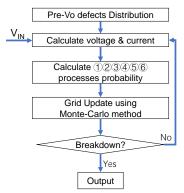

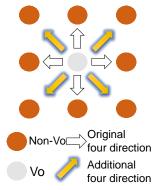

The probability of Vo generation is decided by the equation (2). As can be seen in the equation, the probability could be modulated by the grid potential. An external electric field can increase the probability of Vo generation, significantly. We used Monte Carlo method to simulate the motion of Vo and O<sup>2</sup>. At each step, we generated a random number corresponded with the probability to decide whether to move or not. Fig. 1 shows the total microscopic process simulated in our study. Fig. 2 shows the simulation flow. Key parameters used in our simulation are listed in Fig. 3. In our simulation, Vo possible motion paths are not only the traditional 4-directions [6] but also other four directions, as shown in Fig. 4.

#### 2. Results and Discussion

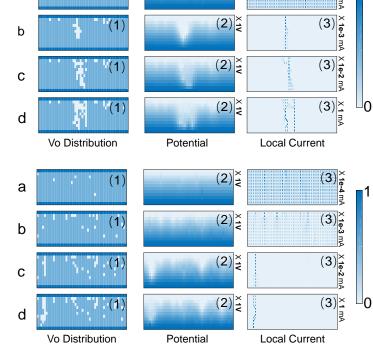

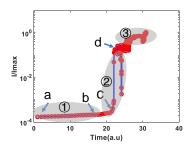

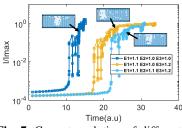

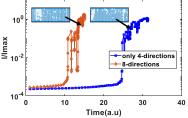

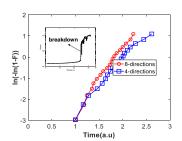

Fig. 5 shows the current evolution in the dielectric under a continuous stress. There are three typical stages of the current evolution. In the first stage, the current increases slowly and with a rapidly increase in the second stage and then becomes stable in the final stage. Fig. 6 shows the Vo distribution, local potential and current refer to the stress time (a)-(d) in Fig. 5. At the time (a), only sparse Vo could be found, and the potential is uniform. Therefore, the local current is relatively small. At the time (b), there are more Vo generated, and the potential distribution becomes more and more nonuniform. Also, Vo tends to align at the place where the electrical field is high. The current increases a little near the Vo site. The time (c) is a special and important timing. At this timing, Vo forms a conductive channel for the first time. Once the conductive channel is formed, the current will increase significantly. At the time (d), the conductive channel will increase a bit and then the system will be in a final stable state. We compared the cases of different energy barriers in our simulation. Fig. 7 shows the current evolution of different Vo generation barriers and Vo migration barriers. The simulation results show that the low interface Vo barrier will enhance conductive channel forming process which indicates that improving the interface might be a promising way to avoid TDDB in high-k gate dielectrics. Fig. 8 shows the current evolution of both using only 4-directions and improved 8-directions. The final Vo distribution by using 8-directions simulation tends to form one thick conductive channel rather than two or more thin conductive channel which often appears in the 4-directions simulation. A thicker conductive channel should be more reasonable compared with experiments according to the experimental results in literatures [7-8]. Fig. 9 shows the Weibull distribution of breakdown time extracted from our simulations. The linearity verified our simulation is self-consistence. This fact reflects the stochastic behavior of the failure mechanism of dielectric.

# 3. Conclusions

In this study, we have presented a dielectric breakdown simulation toolkit. The toolkit can be used for simulating the breakdown process based on the Vo generation and migration, and O<sup>2-</sup> migration under the external electric field. We also found that the treatment of 8-directions migration is more reasonable than the 4-directions one.

# Acknowledgements

This work was supported in part by the National Science and Technology Major Project of the Ministry of Science and Technology of China (No. 2017ZX02315001-07), the NSFC under Grant of No. 61704152 and the National Key Research and Development Program (2017YFA0207600).

## References

[1] G. Ribes *et al.*, IEEE. Trans. Device Mat. Rel., vol. **5** (2005) 5. [2] A. Ranjan *et al.*, IEEE IRPS (2016) 7A-4. [3] C. H. Yang *et al.*, IEEE IRPS (2016) 7A-1 [4] Y.S. Chen *et al.*, IEDM Tech. Dig (2011) 717 [5] G. Bersuker *et al.*, IEDM Tech. Dig (2010) 456. [6] P. Huang *et al.*, Proc. SISPAD (2012) 312 [7] S. Zhao *et al.*, IEEE INEC (2016) 1 [8] S. Chung, IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC) (2015) 360

**Fig. 1.** The micromechanics of Vo and  $O^{2-}$  in high-k dielectric.

Fig. 2. Simulation flow.

а

| Key Parameters                             | Value      |

|--------------------------------------------|------------|

| Vo_i: Initial Vo concentration             | 0.5%       |

| υ: Vibration frequency                     | 1e13       |

| E1: Vo generation barrier inside           | 1.1 eV     |

| E2: Vo generation barrier at the interface | 1.0~1.1 eV |

| E3: Vo migration barrier                   | 1.0~1.2 eV |

| R1                                         | 1e3 Ω      |

| R2                                         | 1e10 Ω     |

| Length                                     | 25 nm      |

| Thickness                                  | 5 nm       |

| Distance between two Vo sites              | 0.5 nm     |

**Fig. 3.** Key parameters used in this simulation.

(E)

**Fig. 4.** Vo migration directions. White arrows represent the traditional four directions. Golden arrows represent the additional four directions used in this work.

(2) ×

**Fig. 6.** (1) Vo distribution (2) Potential distribution (3) Current distribution. The 12 inner figures above represent simulation with 8 directions while the 12 inner figures below represent simulation with 4 directions. Figure (a) $\sim$ (d) corresponded to time(a) $\sim$ (d) in figure 5.

**Fig. 5.** The current evolution of high-k dielectric breakdown under continuous external electric field stress.

**Fig. 7.** Current evolution of different Vo generation barrier and Vo migration barrier. It can find that lower Vo generation barrier at the interface will result in more serious breakdown. Inner figure represents Vo distribution.

**Fig. 8.** Current evolution of 4-directions and 8-directions method. It can find that 8-directions methods will form a thick conductive channel rather than several thin channels, which is more reasonable.

**Fig. 9.** Weibull distribution simulated using our toolkit. The breakdown judgement is plotted in the inner figure.