# **Printed Flexible Resistive Switching Memory**

Ari Alastalo<sup>1</sup>, Kim Eiroma<sup>1</sup>, Mika Suhonen<sup>1</sup>, Dewei Chu<sup>2</sup> and Sean Li<sup>2</sup>

VTT Research Centre of Finland, Tietotie 3, 02150 Espoo, Finland

Phone: +358-40-537-6198 E-mail: ari.alastalo@vtt.fi

School of Materials Science and Engineering, University of New South Wales, Sydney, 2052 New South Wales, Australia

### **Abstract**

Resistive-switching memory (ReRAM) devices are fabricated on a flexible plastic substrate using inkjet printing. Current-voltage-cycling and endurance properties of the memory devices are characterized. The technology is meant for large area electronics such as sensor arrays.

### 1. Introduction

Resistive switching random-access memory (RRAM) is a candidate for future high-density IC memory because it can help to reduce power consumption and footprint as well as to increase the switching speed. In addition, RRAMs have been proposed for new computing paradigms such as multilevel memory, neuromorphic computing and neural networks [1]. For large-area electronics, logic based on RRAMs can be used to perform sensor-array readout and event detections functions in analog fashion for distributed systems [2], [3]. RRAMs have typically a simple vertical metal-insulatormetal (MIM) device structure, where one electrode material is inert such as gold while the other electrode material (such as silver) can diffuse / migrate through the insulator layer and the insulator is a metal oxide. For the insulator, a wide selection of oxide materials have been used such as Al<sub>2</sub>O<sub>3</sub>, CeO<sub>2</sub> and ZrO<sub>2</sub>[4]. Most of the focus has been on fabrication methods such as sputtering, PLD and ALD but recently solution processing has also been reported [3], [5] using coating methods for the oxide such as dip-coating or spin coating. Patterning of the oxide layer by printing would avoid material-removing steps and thus limit waste and enable an easy access to bottom electrode contact.

This paper reports inkjet-printed CeO<sub>2</sub> memory devices on ITO-PEN substrate. The continuous ITO layer serves as the bottom electrode and the top electrode is fabricated using a commercial Ag nanoparticle ink. For the CeO<sub>2</sub> layer, a nanocube dispersion is used<sup>5</sup>. The devices are characterized for IV cycling and endurance up to 1000 cycles. The samples also passed a simple bending test for 25 mm radius.

### 2. Fabrication

ITO-coated PEN plastic (Teonex-Q65 PEN substrate coated by Geomatec Co Ltd) was selected as the substrate. For the oxide layer, a CeO nano-cube dispersion previously reported in [5] was used. The dispersion was deposited on the substrate by inkjet printing using a PiXDRO LP50 printer driving a Fujifilm Dimatix DMC-11610 printhead with a nominal drop volume of 10 pL. An area of 20 mm x 15 mm

was printed using a 500 Hz jetting frequency, a 30  $^{\circ}$ C printhead and substrate temperature, and a 500 dpi x 500 dpi printing resolution. A total of 22 layers were printed on top of each other to build the oxide thickness. The total deposited oxide volume was 25  $\mu$ L and the duration of the printing was 9 minutes. The oxide layer was annealed under UV light (Fusion UV H-bulb at 27 cm distance) for 60 minutes to remove solvents and organic additives (oleic acid, OLA) of the dispersion.

The top electrodes were fabricated by inkjet printing using the Ag nanoparticle ink ANP DGP 40LT-15C of Advanced Nano Products Co. LT. The top electrodes were printed in two sizes on top of the oxide layer as circular contacts of 50  $\mu m$  and 100  $\mu m$  in diameter.

### 3. Characterization

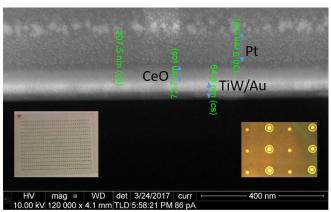

Thickness of the printed oxide layer was determined by fabricating samples on Au-coated silicon wafer, milling a step using focused ion beam (FIB) and taking a side-view SEM image.

Electrical measurements for IV cycling were done using a Keithley SCS 4200 system. Endurance measurements were performed by successively programming the memory to its low-resistance and high-resistance states using positive and negative voltage pulses, respectively. After each programming pulse, the memory state was determined by a current measurement at low voltage that did not alter the state of the memory. To program long pulse sequences for endurance measurement, a customized measurement board was constructed. The board consists of a transimpedance amplifier that provides three voltage outputs which are proportional to the current through the memory device at different current ranges and transimpedance gains.

### 4. Results

The UV power during the annealing of the oxide layer was estimated to be 57 mW/cm2 and 80 mW/cm2 at UVA and UVC, respectively, using an UV meter (Honle UV Tech).

The oxide thickness for 16 printed layers was 72.7 nm as measured using FIB and SEM (see Fig. 1). Therefore, it was estimated that the oxide thickness of the memory devices with 22 layers is about 100 nm.

The UV annealing time of 60 minutes was determined by Raman spectroscopy to result in removal of the organic additives (OLA) of the dispersion.

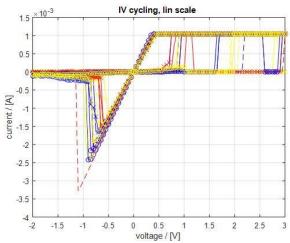

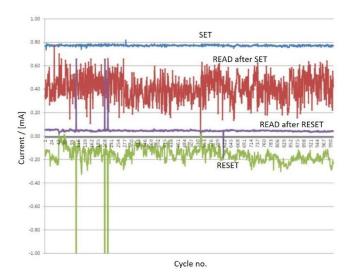

IV cycling results are shown in Fig. 2 for 20 consecutive cycles. The current compliance is at 1 mA for positive voltages and at 10 mA for negative voltages. The SET voltage varies between 0.75 V - 3 V and the RESET current varies between -1 mA - -3.3 mA. Typically, for SET, the first transitions occurred at higher voltages and after that, the voltages were closer to the lower limit. The RESET transition occurs at voltages between -0.5 V - -1.1 V. For memory operation, the SET and RESET voltages need to be selected taking the device variation and cycle-to-cycle variation into account. Fig. 3 shows an endurance measurement of another device with  $V_{SET} = 2 \text{ V}$  and  $V_{RESET} = -2 \text{ V}$ . For both SET and RESET transitions, the readout voltage is  $V_{READ} = 0.25 \text{ V}$ . During the 1000 measured cycles, the device fails 4 times since there is no current level that can be used to decide if the memory is in the high-resistance or low-resistance state for all the measurements. In the figure, these four failures can be seen where the red and magenta curves meet. One method to improve the retention performance is to repeatedly program the device as suggested in [6]. A simple bending test was performed for the devices, where the sample was bent 10 times for radius of 25 mm. No change in memory performance could be concluded.

Fig. 1: SEM image of sample cross section on Si. Insets show the sample on PEN (left) and a magnification for the electrodes (right).

Fig. 2: IV cycling for 20 cycles.

Fig. 3: Endurance measurement (current for readout voltage) up to 1000 programming cycles. The blue and green curves show the current through the device during the set and reset transitions at 2 V and -2 V excitations. The red and magenta curves show the current after the switching at 0.25 V excitation voltage.

#### 5. Conclusions

Printed flexible resistive oxide memory devices were presented. The results are relevant for large-area electronics for which resistive memories can enable new data-storage and logic solutions.

### Acknowledgements

This work is supported by Australian Advanced Materials Pty. Ltd. and the Academy of Finland (project ROXI grant No. 305450).

## References

- [1] H. S. P. Wong *et al.*, "Metal-oxide RRAM," *Proc. IEEE*, vol. 100, no. 6, pp. 1951–1970, 2012.

- [2] N. Ge *et al.*, "An efficient analog Hamming distance comparator realized with a unipolar memristor array: A showcase of physical computing," *Sci. Rep.*, vol. 7, no. December 2016, pp. 1–7, 2017.

- [3] J. Smith, S. Chung, J. Jang, C. Biaou, and V. Subramanian, "Solution-Processed Complementary Resistive Switching Arrays for Associative Memory," *IEEE Trans. Electron Devices*, vol. 64, no. 10, pp. 4310–4316, 2017.

- [4] D. Kumar, R. Aluguri, U. Chand, and T. Y. Tseng, "Metal oxide resistive switching memory: Materials, properties and switching mechanisms," *Ceram. Int.*, vol. 43, no. May, pp. S547–S556, 2017.

- [5] A. Younis, D. Chu, I. Mihail, and S. Li, "Interface-Engineered Resistive Switching: CeO 2 Nanocubes as High-Performance Memory Cells," pp. 2–7, 2013.

- [6] G. Wang *et al.*, "Impact of program/erase operation on the performances of oxide-based resistive switching memory," *Nanoscale Res. Lett.*, vol. 10, no. 1, 2015.