# Analysis of Natural Local Self-Boosting Effect due to Down-coupling Phenomenon in 3D NAND Flash Memory

Youngseok Jeong<sup>1</sup>, Gwanho Lee<sup>1</sup>, Jongwook Jeon<sup>2</sup>, Hee-Sauk Jhon<sup>3</sup>, Yoon Kim<sup>4</sup> and Myounggon Kang<sup>1</sup>

Dept. of Electronics Engineering, Korea National University of Transportation, Room No.307, IT building, 50 Daehak-ro, Chungju-si, Chungbuk 27469, Republic of Korea

Dept. of Electronics Engineering, Konkuk University, Seoul, Korea

Dept. of Electronics, Information and Communication Engineering, Mokpo National University

Dept. of Nanoenergy Engineering, Pusan National University

Phone: +82-10-9860-2846 E-mail: mgkang@ut.ac.kr

## Abstract

In this paper, we analyzed the effect of natural local self-boosting (NLSB) due to the down-coupling phenomenon (DCP) in 3dimensional (3D) NAND flash memories. The inhibited channel in the 3D NAND flash structure can be in the floating state easily because its channel is not directly connected to its body. The DCP phenomenon reduces the channel potential and it leads to have negative effects on memory operation. This is because the DCP is dominant with increasing triple level cell (TLC) and quad level cell (QLC), where the bits of the cell are increased. Therefore, the NLSB effect is reduced because of DCP and the program disturb in inhibit string is increased due to the decrease of channel potential.

#### 1. Introduction

The NAND flash memory market has rapidly increased in demand and supply in the 21st century due to the development of mobile devices such as USB memory, digital cameras, smart phones and tablet PCs. As NAND flash technology shrinks, it gains greater size and power. However, as the devices are scale down, problems such as cell to cell interference (CCI) and lithography patterning are faced with limitations [1-4]. The main cell channel of 3D NAND flash memory is not connected to the body. As a result, the channel can be floating because the body bias should not be applied to the main cell's channel [5]. In order to solve this problem, a 3D NAND flash memory structure stacks cells in a vertical direction. Therefore, it has been found that a NLSB effect occurs [6]. The NLSB effect does not need to use the Local Boosting Scheme used in 2D NAND because it can achieve a sufficiently high potential even if the number of stacks increases. In addition, we examined the NLSB phenomenon according to pattern and bias change in the previous research [7]. However, the DCP phenomenon negatively affects the NLSB effect. Since the 3D NAND flash structure is different from the 2D NAND flash structure, understanding of the new phenomenon in 3D NADN flash is important for obtaining high performance and good reliability [8]. In this paper, we analyzed the NLSB effect due to DCP phenomenon in detail. To analyze this phenomenon, 3D Technology computer-aided design (TCAD) simulation (ATLAS Silvaco<sup>TM</sup>) was used [9].

## 2. Experimental methods

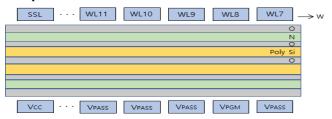

Fig. 1 Simplified vertical diagram of 3D NAND flash

To do this research, we used a 3D NAND flash memory structure with 16 layers [5-7]. Fig. 1 is a vertical cross-sectional view. To verify the DCP phenomenon, the Program Voltage ( $V_{PGM}$ ) to the Word-Line (WL) 8 during the read operation and applied the Pass Voltage ( $V_{PASS}$ ) to the other WLs. Assuming that WL7, 8, 9 threshold voltage ( $V_t$ ) is 1 V and the other WLs have  $V_t$  having 3 V, when the read operation is completed and  $V_{PASS}$  falls below 3 V, Except for WL 7, 8 and 9, the others WL are turned off and the WL 7, 8 and 9 channels are changed to a floating state. Therefore, the channel bias is changed with WL bias. That is, the channel potential of WL7,8 and WL9 becomes -3 V. Therefore, it can be expressed as Equation (1) [5].

$\Delta V down-couple = -V_t$ , neighborcells (1)

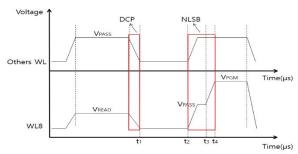

Fig. 2 The timing Diagram of DCP and NLSB

Fig. 2 shows the timing diagram used for verification and program sequence. After the verification is completed, that is, in the t1 state, the channel potential is reduced due to the DCP effect. When  $V_{PGM}$  is applied from t2 to t4, the channel electrons of the adjacent cell move to the WL cell selected by the potential difference. At this time, in order to supply electrons, the 3D NAND flash structure has no N + region or body contact, so that the upper cell remains off. Therefore, the channel of the selected WL cell was localized automatically [6]. That is, the NLSB effect due to  $V_{PGM}$  rise occurs only in the channel of the selected WL cell. Although the channel potential increases due to the NLSB effect, the NLSB phenomenon is negatively affected because the channel potential is already decreased due to the DCP phenomenon.

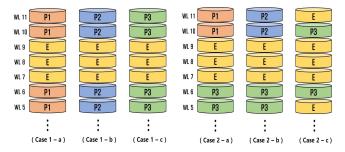

Fig. 3 NLSB effect on DCP phenomenon according to the pattern

Fig. 3 is the analysis of the NLSB effect according to the DCP phenomenon according to the various patterns seen in the previous research [5]. In this case, E, P1, P2, P3 pattern means WL Vt and E = -1 V, P1 = 1 V, P2 = 2 V, and P3 = 3 V. The Case 1 shows that the DCP phenomenon differs by 1 V. However, when the channel potential is checked after the NLSB effect, the difference rapidly increases to 12.45 V, 9.55 V, and 7.45 V, respectively. Therefore, the larger the DCP phenomenon, the less NLSB effect, which has a negative effect on the channel potential, resulting in a program disturbance. Therefore, it is necessary to minimize the DCP phenomenon.

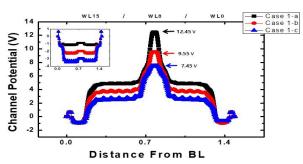

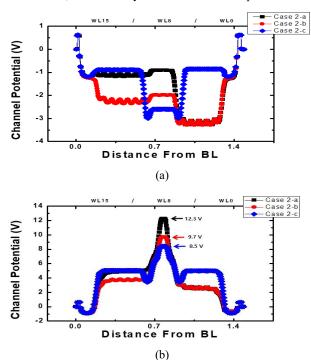

Fig. 4 (a) Channel potential at T1 (b) Channel potential at T4

In case 2-a of Fig.4 (a), the channel potential of WL8 is -1 V. These turns off when the lower cell (WL6  $\sim$  0) is at 3 V, but turns off when the upper cell (WL10  $\sim$  15) is at 1 V. Therefore, when the voltage is less than 1 V, both adjacent cells of the WL8 are turned off to be in a floating state, and the channel bias changes along with the WL bias. Case 2-b is different from case 2-a, and the upper cell is turned off when the voltage is less than 2 V. Therefore, when the voltage is less than 2 V, both adjacent cells of the WL8 are floated, and the channel bias changes with the WL bias, so that the channel potential of the WL8 becomes -2 V. Therefore, it can be expressed as Equation (2).

$$V_t$$

, neighborcells<sub>n-1</sub>  $< V_t$ , neighborcells<sub>n+1</sub>  $\Delta V$  down-couple  $= -V_t$ , neighborcells<sub>n-1</sub> (2)

Case 2-c shows that the DCP phenomenon occurs in two adjacent cells. WLs other than WL6 and WL10 are E patterns, but WL6 and 10 are P3 patterns, so they turn off when they become 3 V or less. Therefore, WL7, WL8, and WL9 become a floating state, and the WL bias also changes due to the channel bias. At this time, the channel potential of the WL8 is higher than -3 V because of the charge sharing effect. Fig. 4 (b) shows the channel potential after the NLSB effect. This shows that the channel potentials are 12.3 V, 9.7 V, and 8.5 V, respectively and the NLSB effect is reduced due to the DCP phenomenon even though the same voltage is applied.

#### 3. Conclusions

In this paper, we investigated analysis of NLSB effect ue to the DCP in 3D NAND flash memory. It is confirmed that the DCP phenomenon is determined by the  $V_{\rm t}$  of the adjacent cell irrespective of the cell  $V_{\rm t}$ . Although we observed DCP phenomenon in one cell, we observed that the channel potential slightly increases due to the charge sharing effect, but it is difficult to say that the channel potential of the other WLs is reduced to the contrary, which is a good phenomenon. That is, regardless of the other cells, the DCP phenomenon increases as the  $V_{\rm t}$  of the adjacent cell increases. This reduces the NLSB effect and reduces the channel potential during program operation, resulting in program disturb. DCP phenomenon increases because  $V_{\rm t}$  increases with TLC and QLC. Therefore, it is important to reduce the DCP phenomenon in order to maximize the NLSB effect and reduce the program disturb.

### Acknowledgements

This work was supported by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (2016R1D1A3B03933150) and in part by National R&D Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science, ICT and Future Planning (2017M1A7A1A01016265) and Basic Science Research Program through the National Research Foundation of Korea(NRF) funded bv the Ministry of Education (2018R1A6A1A03023788) and MOTIE(Ministry of Trade, Industry & Energy (10085645) and KSRC(Korea Semiconductor Research Consortium) support program for the development of the future semiconductor device.

#### References

- [1] M. Kang, et al., "An accurate compact model considering direct-channel interference of adjacent cells insub-30-nm NAND flash technologies", IEEE Electron Device Lett., vol. 33, no. 8, pp. 1114-1116, Aug. 2012

- [2] Y. Kim and M. Kang, "Predictive modeling of channel potential in 3-D NAND flash memory," IEEE Trans. Electron Devices, vol. 61, no. 11, pp. 3901-3904, Nov. 2014

- [3] M. Kang, et al., "The compact modeling of channel potential in sub-30nm NAND flash cell string," IEEE Electron Device Lett., vol. 33, no. 3, pp. 321–323, Mar. 2012.

- [4] M. Kang, et al., "A compact model for channel coupling in sub-30 nm NAND flash memory device," Japanese Journal of Applied Physics, vol. 50, no. 10, p.0204, 2011.

- [5] Y. Kim and M. Kang, "Down-coupling phenomenon of floating channel in 3D NAND flash memory", IEEE Electron Device Lett., vol. 37, no. 12, pp. 1566–1569, Dec. 2016.

- [6] M. Kang and Y. Kim, "Natural Local Self-Boosting Effect in 3D NAND Flash Memory", IEEE Electron Device Lett., vol. 38, no. 9, pp. 1236–1239, Sept. 2017

- [7] G. Lee, Y. Kim, J. Jeon, M. Kang, "Analysis of NLSB Effect depending on Cell Pattern and Bias Conditions in 3D NAND Flash Memory", ICEIC 2018, pp. 962-963, Jan. 2018.

- [8] Y. Kim and M. Kang, "Predictive modeling of channel potential in 3-D NAND flash memory," IEEE Trans. Electron Devices, vol. 61, no. 11, pp. 3901–3904, Nov. 2014, doi: 10.1109/TED.2014.2355918.

- [9] Atlas User's Manual, Silvaco Version. 5.19.20. [Online]. Available: http://www.silvaco.com/products/tcad/device\_simulation/atlas/at-las.html