# Charge and Discharge Characteristics of On-chip CeO<sub>x</sub> Electric Double Layer Decoupling Capacitors

Kazuya Hisatsune, Yoshitaka Takaku, Kohei Sasa, Takuya Hoshii, Iriya Muneta, Hitoshi Wakabayashi, Kazuo Tsutsui, Kuniyuki Kakushima Tokyo Institute of Technology

4259 Nagatsuta-cho, Midori-ku, Yokohama, Kanagawa 226-8502, Japan Phone: +81-45-924-5847 E-mail: hisatsune.k.ab@m.titech.ac.jp

#### **Abstract**

Charge and discharge properties of a metal-insulator-metal (MIM) capacitor with ionic-oxygen-conductive  $CeO_x$  layer was characterized. Transient capacitance response upon charge and discharge suggested the ionic movement in the  $CeO_x$  layer. From transient discharging current, a high capacitance of over  $100\mu F/cm^2$  can be obtained. A large capacitance can be used to back the on-chip decoupling capacitors.

## 1. Introduction

Decoupling capacitors with on-chip MIM structures have been widely used to suppress the high-frequency noise in the power supply line [1]. With large demands to increase the capacitance density along with the technology node, MIM capacitors with thin high-k insulators [2] or 3-plate MIM capacitors [3], effectively increasing the electrode area, have been reported so far. As these approaches may be limited by the leakage current through the electrodes, scaling in the insulators requires higher dielectric constant must be explored. Recent study on solid electric-double-layer (EDL) transistors has shown that a large capacitance density of several µF/cm<sup>2</sup> can be achieved by the movement of ions in the insulators [4]. Although there exists a drawback in the speed for charge/discharge, a large capacitance density may be useful to back the conventional MIM decoupling capacitors. In this work, the charge and discharge properties of EDL capacitors with a CeO<sub>x</sub> layer are characterized.

#### 2. Device fabrication

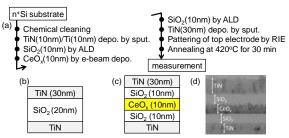

Fig. 1 shows the fabrication flow of the MIM capacitor. An e-beam deposited  $CeO_x$  layer is sandwiched by atomic layer deposited  $SiO_2$  layers. Oxygen deficiency with an x of 1.6 [5] was intentionally introduced to enhance the oxygen-ionic conductivity [6]. The top and bottom electrodes are both sputter-deposited TiN. After patterning the top electrode, the capacitors are annealed at  $420^{\circ}C$ . As a reference, a capacitor without the  $CeO_x$  layer is fabricated as well. The differential capacitance measured by LCR meter and the charging and discharging transient current were measured under different temperature.

# 3. Charge and discharge characteristics

# 3.1 Frequency dispersion of the capacitors

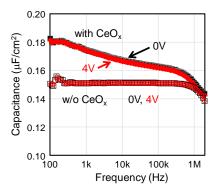

The frequency-dependent capacitance of the MIM capacitors under 0 V and 4 V are shown in Fig. 2. The capacitance of the MIM capacitor without  $CeO_x$  showed a constant value of  $0.15~\mu F/cm^2$ , where the value is reasonable for  $SiO_2$  with a dielectric constant of 3.9 and its thickness.

Figure 1 (a) Fabrication process of the  $CeO_x$  EDL capacitor. Structures of the MIM capacitors (a) without and (b) with  $CeO_x$  layer. (d) TEM image of the fabricated EDL capacitors.

Figure 2 Frequency dependent capacitance without and with CeO<sub>x</sub> layer.

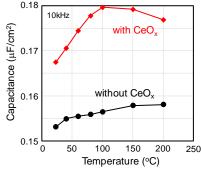

Figure 3 Temperature dependent capacitance of the MIM capacitors at 0 V with and without CeO<sub>x</sub> layer.

With the insertion of  $CeO_x$  layer, an even higher capacitance value can be observed. Along with the strong frequency dispersion in the capacitance, the obtained differential capacitance suggests the response of oxygen ions the  $CeO_x$  layer [7]. A slight decrease in the capacitance is due to the

presence of voltage coefficient of capacitor (VCC). Fig.3 shows the capacitance values measured at 10 kHz under elevated temperature. While increasing the temperature, capacitance showed an increase up to 100°C and turned back to a slight decrease at high temperature. The behavior can be understood from the different temperature coefficient of capacitance (TCC) of SiO<sub>2</sub> and CeO<sub>x</sub>; positve for SiO<sub>2</sub> and negative for CeO<sub>x</sub>, which compensates at elevated tempeature.

## 3.2 Transient response of the capacitors

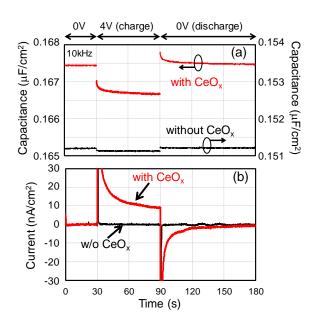

The time responses of the capacitance and the current after a step voltage of 4 V application (t=30s) and back to 0 V (t=90s) are shown in Fig. 4. When a voltage was applied to the top electrode, an exponential decrease in the capacitance was observed. A charging current corresponding to the change in the capacitance change was also observed in the same time range. The discharging behavior also showed an exponential decrease in the capacitance back to the steadystate capacitance value, with a corresponding change in the discharging current. One needs to note that MIM capacitor without CeO<sub>x</sub> showed no tail in the current. Therefore, transient behavior with a time constant of about 30 s, extracted from both capacitance and discharge current, should be related to the ionic movement in the CeO<sub>x</sub> layer. From the integral of the discharge current, an additional capacitance of 115 uF/cm<sup>2</sup>, three orders of magnitude enhancement, can be achieved.

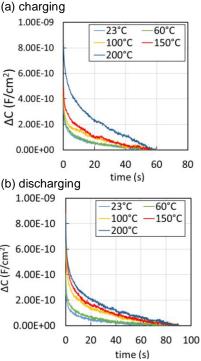

The capacitance change during charging and discharging at different temperatures are shown in Fig. 5. A temperature-dependent time constant change was hardly observed among the data. However, a larger change the capacitance can be observed at a higher temperature. This fact suggests that even higher amount of charges can be stored in the capacitors. Although further studies are needed to shorten the time constant of the charge and discharge, a high capacitance on-chip MIM may be useful to back the decoupling on-chip MIM

Figure 4 Time dependence of (a) capacitance and (b) current during charge at 4V and discharge.

capacitors.

Figure 5 Transient capacitance change at elevated temperature; (a) charging at 4 V and (b) discharging.

## 4. Conclusions

Charge and discharge properties of an EDL-MIM capacitor with  $CeO_x$  layer was characterized. With the ionic movement in the  $CeO_x$  layer, a high capacitance of over  $100\mu F/cm^2$  can be obtained. A large capacitance can be used to back the onchip decoupling capacitors.

### Acknowledgement

This work was partly supported by Canon Foundation.

#### References

- [1] T. Charania, et al., IEEE Trans. VLSI systems, **21**, p. 648 (2013).

- $[2] \quad T. \ Ando, \ et \ al., \ IEDM, \ p. \ 236 \ (2016).$

- [3] K. Fischer, et al., IIT/MAM, p. 5 (2015).

- [4] T. Tsuchiya, et al., Appl. Phys. Lett., 103, 073110 (2013).

- [5] M. Mamatrishat, et al., Vacuum, 86, p. 1513 (2012).

- [6] E. C. Subbarao, *et al.*, Solid State Ionics, **11**, p. 317 (1984)

- [7] M. M. El-Nahass, *et al.*, J. Mater. Sci.: Mater. Electron, 28, p. 1501 (2017).