# Scalable Pentacene-based Pseudo-CMOS Inverter Realized by Threshold Voltage Control utilizing Nitrogen-doped LaB<sub>6</sub> Interfacial Layer

Yasutaka Maeda, Mizuha Hiroki, Yuki Komatsu, and Shun-ichiro Ohmi

Department of Electrical and Electronic Engineering, Tokyo Institute of Technology J2-72, 4259 Nagatsuta, Midori-ku, Yokohama, Kanagawa 226-8502, Japan Phone: +81-45-924-5481 E-mail: maeda.y.al@m.titech.ac.jp, ohmi@ee.e.titech.ac.jp

#### **Abstract**

In this paper, pentacene-based enhancement/depletion-type pseudo-CMOS inverter was investigated with threshold voltage ( $V_{TH}$ ) control utilizing Nitrogen-doped (N-doped) LaB<sub>6</sub> interfacial layer (IL) for the first time. It showed the inverter characteristics with logic swing of 1.8 V for operation voltage at -5 V. In addition, the common-gate geometry was realized for the fabricated pseudo-CMOS inverter, and it is suitable for the scaling of organic CMOS inverter.

#### 1. Introduction

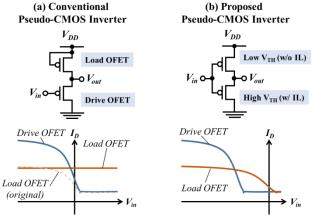

Organic field-effect transistors (OFETs) have attracted much attention because of their unique properties such as flexible and light weight, although the mobility is worse compared to that of Si. Pentacene is well known as p-type organic semiconductor, and a high hole mobility such as 1  $cm^2/(V \cdot s)$  was reported [1]. We have investigated pentacene-based CMOS inverter utilizing nitrogen-doped (N-doped) LaB<sub>6</sub> interfacial layer (IL) which has a low work function of 2.4 eV and oxidation immunity [2, 3]. We have demonstrated negative shift of threshold voltage (V<sub>TH</sub>) and steep subthreshold swing of p-type pentacene-based OFETs by introducing N-doped LaB<sub>6</sub> IL [4]. In this paper, we proposed pentacene-based pseudo-CMOS inverter with common-gate geometry utilizing N-doped LaB6 IL for the drive OFET. As shown in Fig. 1, pentacene-based enhancement/depletion-type pseudo-CMOS inverter with common-gate geometry would be realized due to V<sub>TH</sub> control of the drive OFET to negative direction by N-doped LaB<sub>6</sub> IL.

Fig. 1 Equivalent circuit diagrams and ideal  $I_D\text{-}V_{in}$  characteristics for each OFET of (a) conventional and (b) proposed pseudo-CMOS inverter in this study.

## 2. Experimental Procedure

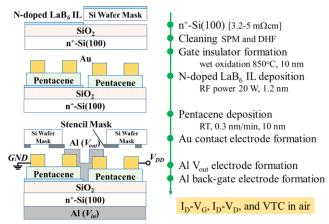

The fabricated pentacene-based pseudo-CMOS inverter consisted of the back-gate/top-contact pentacene-based OFETs, as shown in Figs. 2 and 3. Heavily doped  $n^+$ -Si(100) substrate was cleaned by SPM (H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> = 4:1) and DHF (HF: $H_2O = 1:100$ ). Then, 10-nm-thick SiO<sub>2</sub> was formed on the substrate as a gate insulator by wet oxidation at 850°C. Then, 1.2-nm-thick N-doped LaB<sub>6</sub> IL was formed to control the V<sub>TH</sub> of the drive OFET by RF sputtering at an RF power of 20 W at room temperature (RT) [4]. The patterning of N-doped LaB<sub>6</sub> IL was realized by Si wafer covering. Next, 10-nm-thick pentacene (99%, Aldrich) film was deposited by using thermal evaporation at RT with deposition rate of 0.3 nm/min through a stencil mask for isolation. Then, Au top-contact electrode was formed by thermal evaporation. Finally, Al was evaporated for Vout and back-gate electrodes. The device size of each OFET was  $L_D/W_D = 50 / 1700 \mu m$  for the drive OFET and

Fig. 2 Schematic cross-section of the process flow of fabricated pentacene-based pseudo-CMOS inverter with common-gate geometry.

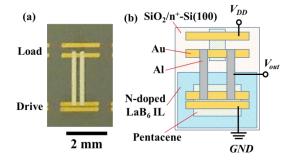

Fig. 3 (a) Top view and (b) schematic configuration of the fabricated pseudo-CMOS inverter.

$L_L/W_L=300\ /\ 500\ \mu m$  for the load OFET taking into account the channel resistance. The fabricated pseudo-CMOS inverter was evaluated by  $I_D\text{-}V_G,\ I_D\text{-}V_D,$  and voltage transfer characteristics (VTC) utilizing Agilent 4156C in air.

# 3. Results and Discussion

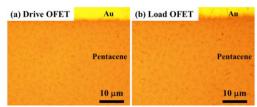

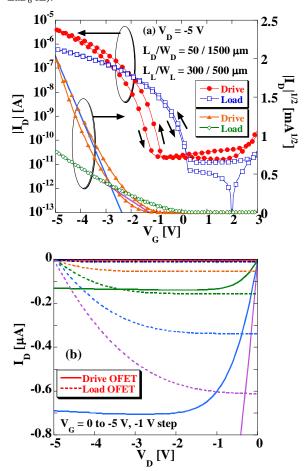

Figure 4 shows surface morphology of pentacene film observed by optical microscopy. The pentacene films were deposited on a 50-nm-thick  ${\rm SiO_2}$  gate insulator for easy to observe the morphology. Both pentacene films in drive and load OFETs showed typical dendritic grains, and their grain size were approximately 2–3  $\mu$ m. Figure 5 shows  ${\rm I_D\text{-}V_G}$  and  ${\rm I_D\text{-}V_D}$  characteristics of each OFET in the fabricated pseudo-CMOS inverter. The  ${\rm V_{TH}}$  of drive and load OFETs were extracted as -2.4 V and -1.3 V, respectively.

Fig. 4 Surface morphology of pentacene films for (a) drive OFET (with N-doped LaB<sub>6</sub> IL) and (b) load OFET (without N-doped LaB<sub>6</sub> IL).

Fig. 5 (a)  $I_D$ - $V_G$  and (b)  $I_D$ - $V_D$  characteristics of drive and load OFETs in the fabricated pseudo-CMOS inverter.

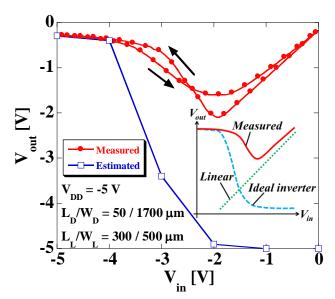

Fig. 6 VTCs measured and estimated from operation points in Fig. 5(b) of the fabricated pseudo-CMOS inverter. The inset shows speculated characteristics of measured and ideal inverter.

Figure 6 shows VTC of the fabricated pseudo-CMOS inverter. The VTC shows typical inverter characteristic by the operation voltage at -5 V, although the linear characteristic began to appear at  $V_{\rm in} =$  -2 V or smaller, as shown in the inset of Fig. 6. Inverter characteristic was realized by  $V_{\rm TH}$  control between load and drive OFETs with N-doped LaB<sub>6</sub> IL, as shown in Fig. 5(a). However, logic swing was 1.8 V, although the logic swing estimated from operation points in Fig. 5(b) was 4.7 V. This was because linear characteristic degraded inverter characteristic probably caused by small  $V_{\rm TH}$  difference of 1.1 V. Therefore, we believe that the adequate design of  $V_{\rm TH}$  and scaling would realize further improvement of the inverter characteristic.

## 4. Conclusion

In this study, we demonstrated pentacene-based pseudo-CMOS inverter utilizing N-doped LaB $_6$  IL. Inverter characteristic was realized of the operation voltage at -5 V even in air by introducing N-doped LaB $_6$  IL. Common-gate geometry of this pseudo-CMOS inverter would be suitable for the scaling, and the adequate design of  $V_{TH}$  and further scaling would improve the inverter characteristics.

### Acknowledgements

The authors would like to thank Prof. Emeritus H. Ishiwara and Mr. S. Kudoh of Tokyo Institute of Technology, the late Prof. Emeritus T. Ohmi and Associate Prof. T. Goto of Tohoku University, Dr. Y. Fujisaki of Hitachi, Ltd., and Mr. K. Takahashi of Sumitomo Osaka Cement Co., Ltd. for their supports and useful discussion for this research. This research was partially supported by JSPS KAKENHI Grant Numbers15K13969 and 18J14821.

# References

- [1] S. Lee, et al., Appl. Phys. Lett. 88, 162109 (2006).

- [2] H. Ishii, et al., ECS Trans. 66, 41, pp. 23–28 (2015).

- [3] Y. Maeda, et al., IEICE Trans. Electron. E99-C, p. 535 (2016).

- [4] Y. Maeda, et al., Jpn. J. Appl. Phys. 56, 04CL06 (2017).