# Ambipolar operation of asymmetric Ge Schottky tunneling source field-effect transistor fabricated on Ge-on-Insulator

Keisuke Yamamoto<sup>1</sup>, Kohei Nakae<sup>1</sup>, Dong Wang<sup>1</sup>, Hiroshi Nakashima<sup>1</sup>, Zhongying Xue<sup>2</sup>, Miao Zhang<sup>2</sup> and Zengfeng Di<sup>2</sup>

Kyushu University, 6-1, Kasuga-koen, Kasuga, Fukuoka 816-8580, Japan Phone: +81-92-583-7292 E-mail: keisuke.yamamoto.380@m.kyushu-u.ac.jp

State Key Laboratory of Functional Materials for Informatics,

Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences,

865 Changning Road Shanghai 200050, China

#### **Abstract**

Asymmetric Schottky tunneling source (STS) FET was fabricated on Ge-on-Insulator (GOI) substrate. GOI was made by using Smart-Cut<sup>TM</sup> technique. Fabricated STS FET with PtGe and TiN electrodes well operated as both n- and p-FETs, which means carrier injection was succeeded in both PtGe/Ge and TiN/Ge interfaces.

#### 1. Introduction

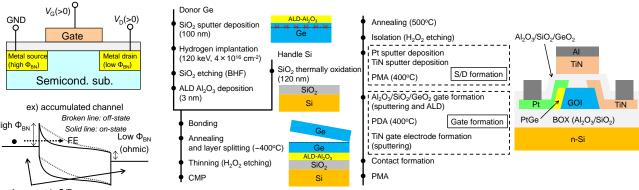

Asymmetric Schottky tunneling source (STS) FET is an alternative device structure to overcome problems related advanced scaling. Its operation principle is carrier injection by field emission (FE) to the channel under strong accumulation or inversion condition induced by gate voltage ( $V_G$ ), as shown in Fig. 1 [1-4]. Ideally, this device structure can completely suppress short channel effect because of no depletion layer in channel/drain junction. Furthermore, it can be apply to steep slope tunneling FET by addition of heavily doped ( $n^+$  or  $p^+$ ) source pockets [5,6].

We have reported Ge STS FET with PtGe and TiN source/drain fabricated on bulk Ge substrate [7]. PtGe and TiN have high electron and hole barrier heights for Ge, respectively. The device well operated as n-FET, which means that electron is successfully injected from PtGe source to accumulated channel. However, p-FET operation has not succeeded. In addition, it is necessary to introduce Ge-on-Insulator (GOI) substrate for performance improvement

In this study, we fabricated Ge asymmetric STS FET on GOI substrate. GOI was fabricated by using wafer bonding and layer splitting methods which are well known as Smart-Cut<sup>TM</sup> [8]. Fabricated device successfully shows ambipolar operation as both n- and p-FETs.

## 2. Experimental

Sample fabrication procedure is shown in Fig. 2. In this study, we prepared (100) n-Ge with  $N_{\rm D}$  of  $1.7\times10^{17}$  cm<sup>-3</sup> and (100) n-Si with  $N_{\rm D}$  of  $7\times10^{14}$  cm<sup>-3</sup> as donor and handle substrates, respectively. After H<sup>+</sup> implantation through 100 nm-thick SiO<sub>2</sub> and subsequent SiO<sub>2</sub> removal, 3 nm-thick ALD-Al<sub>2</sub>O<sub>3</sub> was deposited on Ge substrate. On the other hand, 120 nm-thick thermally grown SiO<sub>2</sub> was formed on Si substrate. Ge and Si were manually bonded in cleanroom environment. Layer splitting was carried out by annealing at 400°C. In order to remove defective layer, Ge was thinned

by wet etching used dilute H<sub>2</sub>O<sub>2</sub> solution. Then chemical mechanical polishing (CMP) was performed to make flat surface. For electrical property improvement, the sample was annealed at 500°C for 1h in N<sub>2</sub> ambient [8]. Then, Ge isolation was performed to island shape for device region by H<sub>2</sub>O<sub>2</sub> wet etching. Device fabrication procedure is almost the same as our previous work [7]. Pt and TiN electrodes were deposited and patterned using sputtering and liftoff techniques. After post metallization annealing (PMA) at 400°C, Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/GeO<sub>2</sub> gate insulator was formed using combination of sputtering and ALD. After postdeposition annealing (PDA) at 400°C, TiN gate electrode was formed using sputtering. Finally, contact holes for S/D were opened and contact Al pads were made by resistive evaporation.

#### 3. Result and Discussion

Figure 3(a) shows an AFM image of the GOI surface after isolation. CMP effectively improves surface flatness of the GOI. Figure 3(b) shows a side wall of the isolated Ge island. Wet etching by  $H_2O_2$  made taper shape side wall. This may be caused Ge isotropic etching by  $H_2O_2$ .

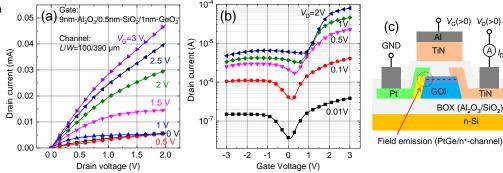

Output characteristic  $(I_D-V_D)$  and transfer characteristic  $(I_D-V_G)$  of the fabricated device are shown in Fig. 4(a) and 4(b), respectively. Here, circuit connection and applied voltage are set for n-FET operation, as shown in Fig. 4(c). It showed typical n-FET operation, which is the same with our previous study on bulk Ge substrate [7]. Positive  $V_G$  induces electron accumulation layer in the GOI island and current conduction mechanism at on-state may be estimated as FE tunneling between PtGe and GOI channel (Fig. 4(c)). However, large off and small on current must be improved.

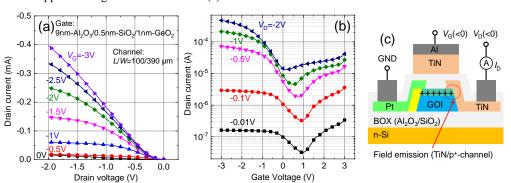

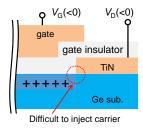

Figures 5(a) and 5(b) are  $I_D$ - $V_D$  and  $I_D$ - $V_G$  characteristics under p-FET circuit connection, which is also shown in Fig. 5(c). Similar to Fig. 4, normal p-FET operation was observed. Negative  $V_G$  makes hole inversion channel in the GOI. Therefore, possible current conduction mechanism is FE tunneling between TiN and GOI inversion channel (Fig. 5(c)). We had not observed p-FET operation in our previous work on bulk Ge [7]. Difference between the previous and this studies is interfacial structure of TiN/Ge contact. Planer interface in previous study prevents efficient carrier transport, as shown in Fig. 6. On the other hand, taper shape TiN/Ge interface under gate stack supports carrier transport. Therefore, GOI and taper shape metal-channel interface is suitable to realize STS p-FET.

## 4. Conclusions

We fabricated asymmetric STS FET on GOI substrate. Fabricated device successfully operated as both n- and p-FETs. Taper shape GOI side wall may support efficient carrier injection between TiN and inverted channel.

## Acknowledgements

This study was partially supported by MEXT/JSPS "Leading Initiative for Excellent Young Researchers (LEADER)" program.

References

[1] R. Hattori et al., JJAP 31 (1992) L1467. [2] Y. Wu et al., Ex-

tended Abstracts of SSDM2012, p. 68. [3] R. Jhaveri et al., IEEE

TED 56 (2009) 93. [4] K.B. Parizi et al., Solid-State Electron. 54

(2010) 48. [5] S. Guin *et al.*, IEEE TED **61** (2014) 2515. [6] K. Jeon *et al.*, VLSI2010 Technology, p. 121. [7] K. Yamamoto *et al.*,

Mat. Sci. Semicond. Processing 70 (2017) 283. [8] J. Kang et al.,

Mat. Sci. Semicond. Processing 42 (2016) 259.

Fig. 2 Sample fabrication procedure and cross sectional image of fabricated STS FET on GOI.

Fig. 4 (a)  $I_D$ - $V_D$ , (b)  $I_D$ - $V_G$  characteristics under n-FET operation. Circuit connection and applied voltages are also shown in (c).

Sa: 0.31 nm <sup>8</sup>

Fig. 3 AFM images of the GOI. (a) surface roughness and (b) side wall of the isolated GOI island.

Fig. 5 (a)  $I_D$ - $V_D$ , (b)  $I_D$ - $V_G$  characteristics under p-FET operation. Circuit connection and applied voltages are also shown in (c).

Fig. 6 Schematic image of TiN/Ge interface for STS FET fabricated on bulk Ge in our previous work [7]. Planer shape junction seems hard to inject carrier.