# Negative bias instability of β-Ga<sub>2</sub>O<sub>3</sub> nanomembrane field-effect transistors

## Jiyeon Ma and Geonwook Yoo

School of Electronic Engineering, Soongsil University, Seoul, 06938, South Korea

Phone: +82-2-820-0938 E-mail: gwyoo@ssu.ac.kr

### **Abstract**

In this poster, we report on negative bias stress (NBS) instability of β-Ga<sub>2</sub>O<sub>3</sub> nanomembrane FETs fabricated by mechanical exfoliation. Although the devices exhibit high electrical performance of field-effect mobility ~ 71.6 due to high crystal quality of β-Ga<sub>2</sub>O<sub>3</sub>, we observe abnormal threshold voltage shift under NBS condition. The result indicates device high quality of surface passivation is required to ensure device's performance.

## 1. Introduction

Recently, gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) has attracted much attention for next generation power device applications, because of its large bandgap (Eg) and high Baliga's figure of merit (BFOM) compared to those of SiC and GaN [1]. It also shows n-type conductivity attributed to oxygen vacancies and unintentional Si incorporation with Ga<sub>2</sub>O<sub>3</sub> powder. β-Ga<sub>2</sub>O<sub>3</sub>'s monoclinic structure has relatively a large lattice constant of 12.23Å along the [100] direction, while that of in the [010] and [001] direction is 3 Å and 5.8 Å, respectively [2]. Although β-Ga<sub>2</sub>O<sub>3</sub> is not a two dimensional van der Waals layered materials, this unique structure allows a facile cleavage into nanomembrane along [100] direction, and there have been several reports based on the exfoliation method [3,4]. For our best knowledge, however, this is the first report on NBS instability of β-Ga<sub>2</sub>O<sub>3</sub> FETs with bottom-gate configuration using mechanically exfoliated β-Ga<sub>2</sub>O<sub>3</sub> nanomembrane from its bulk crystal.

## 2. Device fabrication and Measurement

Heavily doped p-type Si substrate with thermally grown 300nm SiO<sub>2</sub> layer were cleaned in acetone and IPA (Isopropyl alcohol) for 5min. Using conventional scotch tape method, β-Ga<sub>2</sub>O<sub>3</sub> nanomembrane was transferred to the substrate, which was mechanically exfoliated from unintentionally doped Bulk β-Ga2O3 crystals (Tamura corp., Japan) with a (-201) surface orientation; its effective donor carrier concentration (N<sub>d</sub>-N<sub>a</sub>) approximately was 4.8 x 10<sup>17</sup> cm<sup>3</sup>. The source and drain region were defined by conventional photolithography, followed by Cr/Au (20/100 nm) metallization using evaporator and then lift-off process patterned source and drain electrodes. We investigated the electrical parameters and bias instability of β-Ga<sub>2</sub>O<sub>3</sub> nanomembrane field-effect transistors (FETs) using current-voltage (I-V) measurement and negative gate bias stress test at room temperature using a semiconductor parameter analyzer (HP 4145B). Channel thickness was analyzed by AFM (PSIA, XE-150).

### 3. Results and discussions

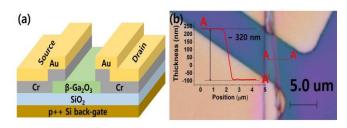

Fig. 1 (a) cross-sectional schematic of β-Ga<sub>2</sub>O<sub>3</sub> nanomembrane FET, (b) optical microscope image of fabricated β-Ga<sub>2</sub>O<sub>3</sub> nanomembrane FET (Inset) Thickness profile of channel layer (Device B).

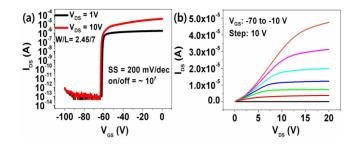

Fig. 2 (a) Transfer characteristics and (b) Output characteristics of the measured β-Ga<sub>2</sub>O<sub>3</sub> nanomembrane FET (Device B).

Fig. 1(a) and (b) show cross-sectional schematic and optical microscope image of the fabricated β-Ga<sub>2</sub>O<sub>3</sub> nanomembrane FET. We confirmed the thickness of β-Ga<sub>2</sub>O<sub>3</sub> channel layer was ~ 320 nm using AFM as shown in the inset of Fig.1 (b). Channel width (W) and length (L) were 2.45 μm and 7 μm, respectably. The capacitance of 300nm SiO<sub>2</sub> was 1.15 x  $10^{-8} \, \text{F/cm}^2$ .

Fig. 2(a) represents the measured transfer curve of I<sub>DS</sub>- $V_{GS}$  for  $V_{DS} = 1$  and 10 V. At  $V_{DS} = 1$  V, it shows on/off ratio of  $10^7$ , field effect mobility ( $\mu_{EF}$ ) of 71.6 cm<sup>2</sup>/V·s and subthreshold (SS) of 200 mV/dec, which were calculated from following eq. (1) and (2), respectably.

$$\mu_{EF} = \left(\frac{L}{W}\right) \cdot \frac{g_m}{C_{OX} \cdot V_{DS}}$$

(1)

$$SS = \frac{d(V_{GS})}{d(\log_{10}(V_{DS}))}$$

(2)

$$SS = \frac{d(V_{GS})}{d(\log_{10}(I_{GS}))} \tag{2}$$

Low SS indicates high quality of the interface between β-Ga<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> was formed. Threshold voltage (V<sub>TH</sub>) was about -60 V extracted from the linear extrapolation of transfer characteristics curve. Fig. 2(b) shows output curves with good saturation and pinch-off at high  $V_{DS}$  bias; it was measured from  $V_{GS}\!=\!$  -70 to -10 V as 10 V step, sweeping from  $V_{DS}\!=\!0$  to 20 V. electrical parameters of the fabricated devices are summarized in Table I

Table I Summary of electrical parameters

| Device | V <sub>TH</sub><br>[V] | $\begin{array}{c} \mu_{EF} \\ [cm^2/V \!\cdot\! s] \end{array}$ | SS<br>[mV/dec] | On/off           |

|--------|------------------------|-----------------------------------------------------------------|----------------|------------------|

| A      | -82.1                  | 26.02                                                           | 260            | $4.10^{6}$       |

| В      | -61.02                 | 71.57                                                           | 200            | $2 \cdot 10^{7}$ |

| C      | -47.25                 | 18.82                                                           | 266            | $7.10^{7}$       |

| D      | -84.9                  | 33.53                                                           | 301            | $9.10^{5}$       |

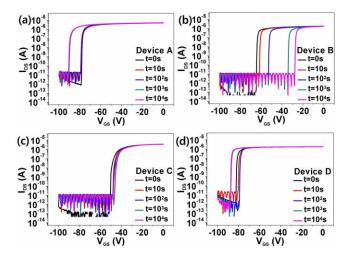

Fig. 3 NBS at device A, B, C and D (a) typically negative shift, (b) abnormally positive shift, (c) and (d) turnaround to negative direction.

To investigate electrical instability, we performed transfer characteristics measurements under NBS condition for 10,000 s at  $t_{stress} = 0$ ,  $10^1$ ,  $10^2$ ,  $10^3$ ,  $10^4$  s. In order to set effective gate bias (=  $V_{GS}$  -  $V_{TH(initial)}$ ) of -20  $\sim$  -15 V, different gate bias ( $V_{GS}$ : -100  $\sim$  -70 V) were applied.

Fig.3 shows  $\Delta V_{TH}$  from the four measured devices. In general,  $V_{TH}$  tends to shift negative direction under NBS, as shown in Fig.3 (a). This is because the electrons, trapped in interface between semiconductor and SiO<sub>2</sub>, release into channel layer. However, Fig.3 (b), (c) and (d) shows the observed abnormal  $\Delta V_{TH}$ ; Device B exhibits positive  $V_{TH}$  shift from -63.9 V to -27 V (i.e.  $\Delta V_{TH} = 36.9$  V). The amount of  $\Delta V_{TH}$  of C and D were 3.69 V and 3.5 V by  $10^3$  s and  $10^2$  s. Then, interestingly enough,  $\Delta V_{TH}$  of C and D shows turnaround behavior forward negative direction after  $t_{stress} = 1,000$  s and 100

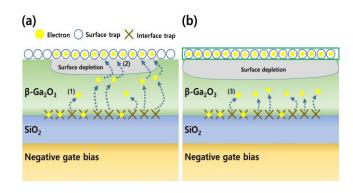

These unusual cases can be explained by surface depletion effects due to defects (i.e. oxygen vacancy) and absorbed traps such as water and oxygen molecules on channel surface. In the case of Device B, as illustrated in Fig. 4(a), surface electron trapping causes surface depletion, which leads to considerable  $V_{TH}$  shift depending on the channel thickness [5]; Surface trapping seems to exceed released electrons into the channel. In return,  $\Delta V_{TH}$  is positive.

Fig. 4 Schematic of surface and interface trapping at NBS: (a) electron release into channel (1). Simultaneously, surface electron trapping occurs (2). (b) After surface trapping fully, electron release into channel only (3).

Using eq. (3), we calculated the surface trapped electron concentration ( $\Delta n$ ) after 10,000s. The  $\Delta n$  of Device B was estimated to 2.65 x  $10^{12}$  cm<sup>-2</sup>. Table II summarize the surface trapped electron concentration  $\Delta n$  of Device B, C and D.

$$\Delta n = Q/e = C_{OX} \cdot (\Delta V_{TH}) \tag{3}$$

Table II surface trapped electron concentration

|                        | 1.1                  |               |                       |

|------------------------|----------------------|---------------|-----------------------|

| Device                 | B by $10^4$ s        | C by $10^3$ s | D by $10^2$ s         |

| Δn [cm <sup>-2</sup> ] | $2.65 \cdot 10^{12}$ | 2.65·1011     | 2.52·10 <sup>11</sup> |

As illustrated in Fig. 4(b), once the surface traps are filled with electrons, the fully trapped surface acts as passivation layer. Consequently, the additional electrons released into the channel lead to charge accumulation in the channel and  $\Delta V_{TH}$  is negative from that point; Device D's  $\Delta V_{TH}$  was -8.84 V from  $10^2$  s to  $10^4$  s. By using eq. (3), Accumulated electron concentration also can be calculated. Since turnaround, the value of Device D was estimated to 6.35 x  $10^{11}\,\rm cm^{-2}$

#### 4. Conclusions

In this study, we report on abnormal positive and turnaround threshold voltage shift of the  $\beta\text{-}Ga_2O_3$  FET under negative bias stress. It results from the surface depletion effects due to surface states and absorbed oxygen and water molecules. This result suggests a high quality of passivation treatment is needed to acquire high electrical performance and stability of the  $\beta\text{-}Ga_2O_3$  FET.

## References

- [1] S. I. Stepanov, V. I. Nikolaev, V. E. Bougrov, and A. E. Roma nov, Rev. Adv. Mater. Sci. 44, 63 (2016).

- [2] M. Higashiwaki, K. Sasaki, H. Murakami, Y. Kumagai, A.Koukitu, A.Kuramata, T. Masui, and S. Yamakosh, Semicond. Sci. Technol. 31, 034001 (2016).

- [3] J. Kim, S. Oh, M. Mastro, and J. Kim, Phys. Chem. Chem. Phys. 18, 15760 (2016).

- [4] H. Zhou, K. Maize, G. Qiu, A. Shakouri, and P. D. Ye, Appl. Phys. Lett. 111, 092102 (2017).

- [5] H. Zhou, M. Si, S. Alghamdi, G. Qiu, L. Yang, and P. D. Ye, IEEE Electron Device Lett. 38, 103 (2017).