# High mobility Si TFTs on crystalline Si stripe formed by micro chevron laser beam scanning

Wenchang Yeh, Mitsuki Hirasue and Toshiaki Tsuchiya

Shimane University Nishikawatsu-cyo 1060, Matsue City Shimane 690-8504, Japan Phone: +81-852-32-8902 E-mail: yeh@riko.shimane-u.ac.jp

#### Abstract

Top gate n-ch thin film transistors (TFTs) were fabricated on crystalline Si stripe having grain length more than hundred microns that was formed by micro chevron laser beam scanning method. Here sputtering SiO<sub>2</sub> was used as gate insulator of TFTs. Maximum field effect mobility was 422cm<sup>2</sup>/Vs, with subthreshold swing of 0.485 V/Dec and on/off ratio of 2.8 x 10<sup>6</sup>.

#### 1. Introduction

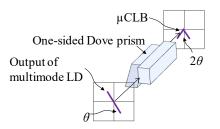

Resolution as well as definition have been increasing in flat panel displays with all sizes since its advent in market several decades before. For small size OLED displays, increasing definition result in miniaturization of pixel size and pixel driving TFTs. Variations in the number of grain boundaries within the channel of pixel driving poly-Si TFTs come to the surface, which cause luminance unevenness among pixels. For large size LCD displays, increasing resolution and flame rate will shorten selected term of a gate line, so higher mobility is demanded. In order to match the above demands for all display sizes, we have proposed micro-chevron laser beam scanning (µCLBS) method<sup>1</sup> for forming long grain crystalline Si stripe. In this method, µCLB, was formed by passing an output of multi-mode UV laser diode through a one-sided Dove prism (Fig.1), and was scanned through Si film to form 5-7 µm wide crystalline Si stripe having grain length more than hundred microns at the scanned path. In recent by adding SiO<sub>2</sub> capping film with a thickness more than 200 nm on the Si film, (100)-faced single grain with a length more than 3mm was also formed. In this study, TFTs was fabricated on the crystalline Si stripe without using SiO<sub>2</sub> capping film on Si, and characteristics of the TFTs will be shown.

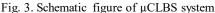

Fig.1 Mechanism of µCLB formation

## 2. Experimental method

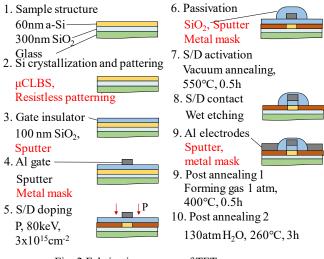

Figure 2 shows fabrication process of TFTs. 1. Dehydrogenated 60nm-thick CVD a-Si film on  $SiO_2$  film as precursor

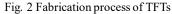

for laser crystallization. 2. About 10µm-wide crystalline Si stripe was formed in Si film by µCLBS, and then non annealed amorphous Si region was selectively removed by a-Si etchant to leave only the crystalline Si stripe as channel island of TFTs without using photolithography technique. Figure 3 shows schematic of µCLBS system here. 3. 100nm-thick SiO<sub>2</sub> film was deposited on the Si stripe by reactive pulse DC sputtering method at 340°C as a gate insulator. 4. 300nmthick Al gate electrode was formed by sputtering through the 1st metal mask. 5. S/D ion implantation at an acceleration voltage of 80 keV and at a dose of 3 x 10<sup>13</sup> cm<sup>2</sup>. 6. Capsulation of channel region by 200nm-thick sputtering SiO<sub>2</sub> film through the 2nd metal mask at room temperature. 7. S/D region dopant activation at 550°C in vacuum for 0.5h. 8. SiO<sub>2</sub> film on S/D region removed by 1% HF solution to expose S/D region for contact. 8. S/D Al electrode deposition using sputtering through 3rd metal mask 9. Forming gas ( $\sim$ 5% H<sub>2</sub> in N<sub>2</sub>) annealing (FGA) at 400°C and at 1atm for 0.5 h as a 1st post annealing. 10. 120 atm high pressure  $H_2O$  annealing (HPA) at 260°C for 3h for the 2nd post annealing. Effect of two general post annealing method on TFT characteristics was compared.

# 3. Results and discussion

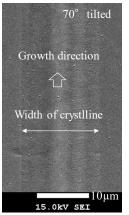

Figure 4 shows scanning electron microscopy (SEM) image of crystalline Si stripe with a tilting angle of 70°. The laser scanning direction is from downside toward upside in the figure. The stripe is convexed and smooth at the center which was a single lateral grain, and is flat and longitudinally undulated toward outside at the side region which was composed of longitudinal lateral grains. The stripe is thick at the center because of agglomeration during melting, and is very flat at that region because no

Fig.4 SEM image of Si stripe

impingement of lateral growth grain there.

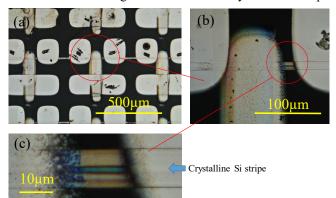

Figure 5 shows optical microscope image of fabricated TFTs. TFT channel region was formed on crystalline Si stripe.

Fig.5 Optical micrograph of fabricated TFTs

Blue colored region at the center of crystalline Si stripe in Fig.5(c) again indicates a thicker film thickness there. The channel dimension was measured from Fig.5 to be  $L/W=95.2\mu m/11.2\mu m$ .

Figure 6(a) and Fig.6(b) shows respectively  $I_dV_g$  and  $I_dV_d$ characteristics. In Fig.6(a), both gate leak current  $I_g$  ( $V_d$  =0.1V) and electron field effect mobility  $\mu_n$  were also shown. The  $\mu_n$  were calculated from transconductance of the TFT at  $V_d$  of 1V, and have been confirmed to be the same as a value calculated at  $V_d$  of 0.1V. Parameter of the TFT were summarized in Table.1. The maximum  $\mu_n$  was 422 cm<sup>2</sup>/Vs, thanks to single grain Si stripe formed by  $\mu$ CLBS. This value is expected to be further increased if lateral grains at the side region of crystalline Si stripe can be removed. Besides, it is worth noting that sputtering SiO2 film was used as gate insulator here. S value might be lower than that in TFTs with CVD SiO<sub>2</sub> due to surface high energy particle impingement during sputtering, but this value is still acceptable for actual

| $\mu_{\rm n}$    | 422 cm <sup>2</sup> /Vs (Maximum value) |

|------------------|-----------------------------------------|

| $V_{\rm th}$     | -1.4 V                                  |

| S                | 0.485 V/dec. (Average value)            |

| $R_{\rm on/off}$ | $2.8 \times 10^{6}$ (Id@Vg = 5V to -5V) |

application to displays. Besides, there is no significant difference on characteristics between TFTs after FGA and further after HPA.

## 4. Conclusions

Top gate n-ch TFTs were fabricated on crystalline Si stripe having grain length more than hundred microns that was formed by micro chevron laser beam scanning method. Here sputtering SiO<sub>2</sub> was used as gate insulator. Maximum field effect mobility was  $422 \text{ cm}^2/\text{Vs}$ , with subthreshold swing of 0.485 V/Dec and on/off ratio of 2.8 x 10<sup>6</sup>. The µCLBS method is expected to provide a new method for fabricating high mobility TFTs.

## Acknowledgements

This study is partially supported by ASTEP-FS project from Japanese Science and Technology Agency.

# References

- W. Yeh, S. Yamazaki, A. Ishimoto and S. Morito, APEX 9,025503(2015).

- [2] W. Yeh, T. Shirakawa, A.H. Pham, and S. Morito, Jpn. J. Appl. Phys., 58, SBBJ06 (2019).