# **Texture Control for Cu Hybrid Bonding Pads using a PVD Cu Process**

Joke De Messemaeker, Nicolas Jourdan, Philip Nolmans, Soon-Wook Kim and Gerald Beyer

imec

Kapeldreef 75, 3001 Leuven, Belgium Phone: +32-16-28-1743 E-mail: joke.demessemaeker@imec.be

## Abstract

Reduction of the Cu diffusion bonding temperature is key for extending the wafer-to-wafer hybrid bonding technology to low-temperature applications. One possible route is based on texture control, aiming for <111> oriented Cu pads which are predicted to enable significantly higher surface diffusion and creep. We report on the development of a PVD Cu process which produces a hightemperature <111> fiber texture and demonstrate its applicability on 540 to 1620 nm hybrid bonding pads.

### 1. Introduction

Wafer-to-wafer (W2W) hybrid bonding of patterned Cudielectric surfaces is a key technology enabling submicron pitch scaling in 3D IC integration [1]. A high temperature anneal (e.g. 350 °C) is used for diffusion bonding of the Cu pads. Reduction of this temperature could open the technology to more applications. Direct bonding of Cu on the {111} crystal plane was shown to allow a bonding temperature reduction, likely due to the higher surface diffusion on this plane [2].

The goal of our study is to verify the impact of Cu crystal orientation on W2W hybrid bonding. We use a PVD Cu process, which has a strong tendency to produce a <111> film after deposition due to the low surface energy for this orientation. The challenge is to maintain this <111> texture at the bonding temperature, as grain growth is expected to occur more rapidly than diffusion bonding. This paper reports on the PVD Cu process development, which was done first on blanket wafers and then transferred to patterned wafers.

### 2. Experimental

### Wafer processing

All wafers were processed in the 300 mm line at imec. Deposition of barrier (thickness 6 nm) and PVD Cu films occurred without vacuum break. Patterned wafers have  $\sim 500$  nm deep pad trenches in a SiO<sub>2</sub> dielectric layer. To evaluate texture changes during grain growth, Cu films are annealed for 20 min at 420 °C.

### Characterization

The film texture is reported as the crystal direction parallel to the wafer normal. It was determined from XRD  $\theta$ -2 $\theta$  measurements by integrating the intensity I under the (111) and (200) peaks and correcting for the structure factor, and is reported as the ratio I(111)/[(I(111)+I(200)]. On Cu pads after CMP, top-down EBSD measurements were done at 20 kV.

Room temperature film stress was calculated from wafer level curvature measurements using the Stoney equation. Thermal cycling measurements were done on coupons.

Fig. 1 Orientation maps for plated Cu hybrid bonding pads. (a,b) 540 nm, and (c,d) 900 nm pads; (a,c) without, and (b,d) with postplating anneal of 20 min at 420 °C. The legend is shown in Fig. 5c.

#### 3. POR plated Cu pad texture

Fig. 1 shows a representative set of orientation maps from EBSD measurements for imec POR hybrid bonding pads, with a width of 540 and 900 nm, with and without anneal. These pads are filled with Cu plated on top of a 100 nm PVD Cu seed layer. None of the maps indicate any preferred orientation, and the POR texture is random.

## 4. Thin film processing development

Impact of barrier type and film thickness

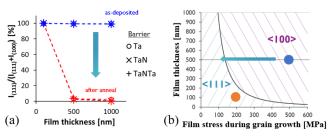

The as-deposited Cu film texture is close to 100 % <111>, regardless of barrier type (TaNTa, TaN or Ta) or Cu film thickness (100, 500 or 1000 nm), Fig. 2a. After annealing this is preserved only for the 100 nm film, and replaced by a <100> fiber texture (possibly complemented with minor other components) for the thicker films.

This orientation selection during grain growth follows from the competition between surface energy minimization on the one hand, depending on film thickness and favoring <111> oriented grains, and strain energy minimization on the other hand, depending on film stress and favoring <100> oriented grains [3]. This results in the texture dominance diagram in Fig. 2b, showing that the threshold stress level during grain growth to preserve the as-deposited <111> orientation is lower for 500 and 1000 nm films, than for a 100 nm film.

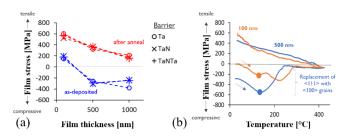

To verify this analysis the film stress was measured before and after annealing (Fig. 3a). The impact from barrier type is again small. The stress after deposition transitions

Fig. 2 (a) Part of <111> component in film texture. (b) Texture dominance diagram; orange and blue dots correspond to dots in Fig. 3b.

Fig. 3 (a) Film stress as function of (a) film thickness, and (b) temperature (for TaNTa barrier, 100 and 500 nm films).

from tensile (islands coalescing) to compressive (atoms forced to enter film, so-called "atomic peening") as film thickness increases.

After annealing the stress is tensile for all samples as a result of stress relaxation at high temperature, as shown for 2 samples with TaNTa barrier in Fig 3b. Upon heating, for both samples the Cu stress becomes more compressive due to the difference in coefficient of thermal expansion with the Si substrate. Around 150 °C, stress relaxation due to grain growth sets in; from around 250 °C there is also stress relaxation due to creep. For the sample with 500 nm film thickness, grain growth sets in at a stress of ~ 500 MPa. This stress is almost fully relaxed by replacement of the <111> grains with <100> grains (strain minimization). For the 100 nm film, uniform grain growth of <111> grains sets in at ~ 200 MPa, and the accompanying stress relaxation is considerably smaller.

In order to preserve the <111> texture also for thicker films then, Fig. 2b predicts that the stress at 150 °C needs to be reduced to  $\sim 150$  MPa, corresponding to a stress after deposition which is slightly tensile.

#### Impact of processing parameters

To generate a thicker film with reduced compressive or even tensile stress, in a second experiment the PVD Cu process parameters were varied for a constant film thickness of 550 nm, with the aim of reducing the atomic peening effect. This was done by increasing the Ar gas pressure (0.3 - 3 - 9 mTorr), and by lowering the DC bias (38 - 27 - 15 kV) and the AC bias (1.1 - 0.6 - 0 kV).

Fig. 4 (a) Film stress, and (b) part of <111> component in film texture, as function of PVD process parameters.

Fig. 3 Orientation maps of 1080 nm pads targeting (a)  $\sim 100 \%$  <111> and (b)  $\sim 0 \%$  <111>. (c) Color legend for wafer normal.

The resulting impact on film stress is shown in Fig. 4a. For our PVD process only the AC bias reduction has the desired effect, where a value of 0 kV even produces a slightly tensile stress. After anneal the texture for this sample is close to 100 % <111> (Fig. 4b, blue arrow), in line with the prediction from Fig. 2b. At the same time, we can identify a process which allows reaching close to 0 % <111> after annealing (15 kV DC bias, purple arrow in Fig. 4b). This may serve as a control texture when investigating the impact of the <111> orientation on hybrid bonding.

#### 5. Process transfer to patterned wafers

After applying the 0 kV AC bias PVD Cu process to patterned wafers, the <111> target texture is maintained at the pad bottom and even sidewall, which confirms the potential of this process for pad texture control. However, the filling behavior is poor, as can be expected for a PVD process. To avoid this drawback, pads filled by plating were recessed 75 nm by wet etch, and the selected 550 nm PVD Cu films were deposited on top. In between the plated and PVD Cu, a barrier was deposited to avoid that the larger plated grains would consume the smaller PVD grains in grain growth. The wafer was then annealed and the Cu and barrier on field removed in CMP. The orientations of the resulting pads demonstrate the successful transfer to pads both for the  $\sim 100$  % <111> texture target and the opposite  $\sim 0$  % <111> texture (Fig. 5). These results were confirmed for pad sizes in the range of 540 to 1620 nm, from center and edge of the wafer.

#### 6. Conclusions

Based on the relation between film stress and texture a PVD process and integration approach were developed, allowing control of the Cu pad texture to  $\sim 100 \% < 111$  or  $\sim 0 \% < 111$ , stable at the high temperatures used for Cu diffusion bonding. In a next step the bonding behavior of these pads will be evaluated to determine the impact of orientation.

#### Acknowledgements

This work was supported by the IIAP of imec and the combined efforts of the 3D team at imec, and its partners.

#### References

- [1] E. Beyne et al., 63<sup>rd</sup> IEDM (2017) 32.4.1.

- [2] J-Y Juang et al., Sci.Rep. 8 (2018) 13910.

- [3] H. Lee et al., J.Appl.Phys. 93 (2003) 3796.