# Characteristics of Ni-silicided Schottky barrier MOSFET using Microwave annealing of low thermal budget

Hyun-Seok Choi, Eun-Ki Hong and Won-Ju Cho\*

Department of Electronic Materials Engineering, Kwangwoon Univ. Cahmbit-kwan, B 104, Wolgye 1-dong, Nowon-gu, Seoul 139-701, Korea Phone: +82-2-940-5163\*E-mail: chowj@kw.ac.kr

#### Abstract

In this study, we applied a new heat treatment method of microwave annealing (MWA) to form Ni silicide films. MWA is a volumetric heating method using microwave energy and has the advantages of high energy transfer efficiency and low thermal budget by transferring energy directly. To evaluate Ni silicide films formed with MWA, electrical characteristics and x-ray diffraction (XRD) measurements were performed. In addition, schottky-barrier (SB) MOSFETs were fabricated. Rapid thermal annealing (RTA), which is widely used for the formation of conventional silicide, was also fabricated and compared. In particular, Ni-silicide SB MOSFETs using MWA showed better electrical characteristics than Ni-silicided SB MOSFETs using RTA.

### 1. Introduction

Metal silicide is used as interconnect and contact materials in complementary metal-oxide-semiconductor (CMOS) technology because of its low contact resistance and compatibility with Si. [1,2] Among metal silicides, Ni silicide are attracting attention in next-generation deep submicron CMOS devices because they offer superior performance at the nanoscale level. [3] In particular, there are many advantages such as low resistivity, less Si consumption, low formation temperature, and little or no resistivity degradation on narrow lines/gates. [4,5] On the other hand, RTA was mainly used as an annealing method to form silicide. However, because of the vacuum process, the process time is relatively long and the thermal budget is high. MWA, on the other hand, is a volumetric heat method using microwave, which directly transfers energy, thereby enabling high energy transfer efficency and selective heating. It also has a short reaction time. [6]

Therefore, in this work, we applied MWA as a method of forming Ni silicide. For comparison, Ni silicide was formed by RTA. To evaluate the Ni silicide films, the electrical characteristics were measure through the sheet resistance and the physical characteristics to confirm the crystal structure were measured using XRD. The SB MOSFETs were fabricated by RTA and MWA and compared.

#### 2. General Instructions

To confirm the electrical characteristics and cryscal structure, the substrates used in this study were a p-type (100) 10-20  $\Omega$ ·cm Si wafer. After RCA cleaning, the Si wafers were loaded into the E-beam evaporator with a

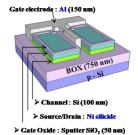

basepressure of  $3 \times 10^{-6}$  Torr. Ni was deposited to a thickness of 30 nm on the sample surface. MWA process at a power of 250-1000 W in the N2 ambient for 2 min was performed for silicide formation. For comparison, RTA process was conducted at 500 °C for 2 min in N<sub>2</sub> ambient. Then, the unreacted Ni was removed using  $H_2SO_4$ :  $H_2O_2$  = 1:1 soulution at room temperature. The substrates were used a p-type (100) SOI wafers with a 100-nm-thick top silicon layer and 750-nm-thick buried oxide (BOX) layers for SB MOSFET. First, standard RCA cleaning was performed to remove surface contamination and native respectively. The active region of SB-TFTs was defined by photolithography and dry etching. In order to form the metallic junctions, 30-nm-thick Ni layers were deposited by E-beam evaporator. The deposition rate was 0.2 Å/s. Silicides formation were performed by MWA process at a power of 600 W in the N<sub>2</sub> ambient for 2 min. The RTA process was conducted at 500 °C for 2 min in N2 ambient for comparison. Then, the unreacted Ni was removed using  $H_2SO_4$ :  $H_2O_2$  = 1:1 soulution. Subsequently, a SiO<sub>2</sub> of 50-nm-thick was deposited for the gate oxide by using RF magnetron sputtering. Finally, a 150-nm-thick aluminum layer for gate electrodes was deposited by E-beam evaporator. Figure 1 shows the schematic structure of the fabricated Ni-silicided SB MOSFETs.

Figure 1. Schematic structure of the fabricated Ni-silicided SB MOSFETs.

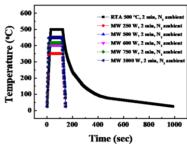

Figure 2. Temperatrue profiles of RTA and MWA process.

Figure 2 shows the temperature profile of RTA and MWA process. The RTA process took about 15 minutes to reach

room temperature after heat treatment as shown in figure 2 and had a thermal budget of  $2.84 \times 10^5$  °C·s. The MWA process was a direct heating method using electromagnetic waves. Thus, a process temperature within about 20 seconds could be reached and a very short ramp-down time of 10 seconds was required. The thermal budget of MWA 250 W, 500 W, 600 W, 750 W and 1000 W were  $0.48 \times 10^5$ ,  $0.55 \times 10^5$ ,  $0.56 \times 10^5$ ,  $0.58 \times 10^5$  and  $0.64 \times 10^{5}$ °C·s, respectively. This indicates that the thermal budget applied to the sample in the MWA process is smaller than the RTA process.

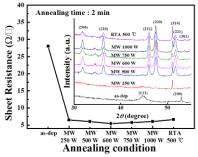

Figure 3. Sheet resistance of Ni silicide according to annealing conditions. Inset shows XRD patterns of Ni silicide.

Figure 3 shows the sheet resistance of Ni silicide measured by a four-point probe according to annealing conditions. The as-deposited Ni films had a sheet resistance of 28.01  $\Omega/\Box$ . After the silicidation, the sheet resistance showed a very low value of about 6  $\Omega/\Box$  in all the heat treatment conditions. The silicide devices fabricated by MWA showed lower sheet resistance than RTA. In particular, it showed the lowest value of 5.43  $\Omega/\Box$  in MWA 600 W heat treatment. Inset shows the XRD patterns of Ni silicide layers annealed various conditions. As shown in inset, the XRD pattern of as-deposited Ni films, which are black lines, showed (111) and (200) peaks, which are pure Ni peaks. However, the XRD patterns of the thin films annealed at RTA 500 °C, MWA 500 W, 600 W, 750 W, and 1000 W were (200), (210), (211), (220), (310), (221), (301) peaks. In particular, it was found that Ni silicide can be formed even though the microwave power is as low as 250 W.

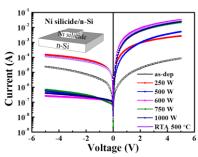

Figure 4. I-V characteristics of Ni silicide Schottky diode according to annealing conditions. Inset shows the schematic structure of Schottky diode.

Figure 4 shows the I-V characteristics of the Ni-silicide Schottky diodes according to annealing conditions. It can be seen that a Schottky diode fabricated with MWA 600W has the highest on-current and lowest off-current, resulting in

the highest on-off ratio. In comparison, the Schottky diode fabricated with RTA 500 °C showed a large leakage current.

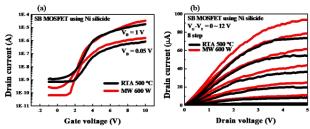

Figure 5. (a) Transfer and (b) output characteristic curves of the Ni-silicided SB MOSFETs at MWA 600 W or RTA 500 °C.

Figure 5 shows the electrical characteristics of Ni-silicided SB MOSFETs at MWA 600 W or RTA 500 °C. The channel width/length (W/L) of the fabricated devices were 10/10  $\mu m$ . The transfer curves measured at a drain voltage (V\_D) of 0.05 and 1 V are shown in Fig. 5(a). The Ni-silicided SB MOSFETs using MWA had a mobility of 170.67 cm²/V·s, subthreshold swing (SS) of 323.62 mV/ dec, V\_th of 2.15 V, and  $I_{on}/I_{off}$  of 3.38  $\times$  10 $^5$  with a lower leakage current. On the other hand, the Ni-silicide SB MOSFET fabricated at RTA 500 °C showed a higher leakage current than the device fabricated at MWA 600 W and had lower electrical characteristic parameters.

#### 3. Conclusions

We fabricated Ni-silicided SB MOSFET by applying MWA. MWA 600 W with the lowest sheet resistance was applied. For comparison, SB MOSFET was fabricated using RTA. The Ni-silicided SB MOSFET using MWA showed better electrical characteristics than the devices using RTA. In conclusion, the MWA method is expected to be used as a silicide process in future CMOS technology because it has less power consumption and is more efficient in thermal budget than the convetional RTA method.

### Acknowledgements

This study was supported by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science, and Technology (No. 2016R1A2B4008754).

## References

[1] K. Hoummada, C. Perrin-Pellegrino, and D. Mangelinck, J. Appl. Phys. 106,063511 (2009)

[2] B. A. Julies, D. Knoesen, R. Pretorius, and D. Adams, Thin Solid Films, 347 (1999)

[3] P. L. Tam and L. Nyborg, Surf. Coat. Technol. 203 (2009)

[4] A. S. W. Wong, D. Z. Chi, M. Loomans, D. Ma, M. Y. Lai, W. C. Tjiu, S. J. Chua, C. W. Lim, and J. E. Greene, Appl. Phys. Lett. 81 (2002)

[5] C. G. Ahn, T. Y. Kim, J. H. Yang, I. B. Baek, W. J. Won, and S. Lee, Mater. Sci. Eng. B, 147 (2008)

[6] J. W. Shin and W. J. Cho, Physica Status Solidi (a), 215 (2018)