# Demonstration of n-MOSFET operation and internal charge analysis of SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> gate dielectric on (111) oriented 3C-SiC

Ryusei Oka<sup>1</sup>, Keisuke Yamamoto<sup>1</sup>, Dong Wang<sup>1</sup>, Hiroshi Nakashima<sup>1</sup>, Shigeomi Hishiki<sup>2</sup> and Keisuke Kawamura<sup>1,2</sup>

<sup>1</sup>Kyushu University 6-1, Kasuga-koen, Kasuga, Fukuoka 816-8580, Japan Phone: +81-92-583-7292 E-mail: yamamoto.keisuke.380@m.kyushu-u.ac.jp <sup>2</sup>Air Water Inc. 2290-1, Toyoshinatakibe, Azumino, Nagano, 399-8204, Japan

#### **Abstract**

We fabricated n-MOSFET with SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> gate dielectric on (111) oriented 3C-SiC substrate. Fabricated device operated as inversion mode MOSFET successfully. We also analyzed fixed charge and interfacial dipole of SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> gate dielectric on (111) n-type 3C-SiC. Both the SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> have negative fixed charge and the gate stack includes large dipole which shifts flatband voltage to negative direction. These results may open a way for application of 3C-SiC electronic device.

#### 1. Introduction

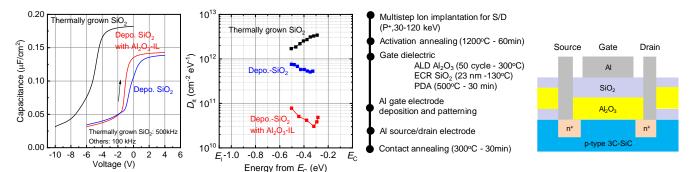

Silicon carbide (SiC) has been attracting much interest as a material for high efficient and small size power devices due to its high breakdown field. Among some polytypes of SiC, (111) oriented 3C-SiC can be grown on Si (111) surface [1]. Therefore, 3C-SiC/Si hetero-epitaxial substrate has a potential for on-chip hetero-integrated electronic device. In order to apply high feasibility of 3C-SiC for electronic devices, it is necessary to form good dielectric on 3C-SiC with high interfacial quality for MOS gate and surface passivation layer. We have succeeded fabrication of 3C-SiC MOS capacitor with high interfacial quality (interface state density:  $D_{\rm it} < 10^{11} \, \rm cm^{-1}$ <sup>2</sup>eV<sup>-1</sup>) by using SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stacked gate dielectric (Fig. 1) [2]. The MOS capacitor showed slightly negative flatband voltage  $(V_{\rm fb})$ . In order to switch MOSFET by appropriate supply voltage, the  $V_{\rm fb}$  and threshold voltage control is important. Concerning layer stacked gate dielectric, fixed charge  $(Q_{fix})$  in each layer and interface dipole ( $\delta_{\text{dipole}}$ ) influence  $V_{\text{fb}}$ . In this article, firstly we demonstrated operation of 3C-SiC n-MOSFET with this gate dielectric. Secondly, we investigated  $Q_{\rm fix}$  and  $\delta_{\rm dipole}$  in SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> dielectric on 3C-SiC in anticipation of  $V_{\rm th}$  control.

## 2. 3C-SiC n-MOSFET operation

The substrate used for n-MOSFET was (111) oriented p-type 3C-SiC epitaxially grown on p-Si (111) substrate. Hole concentration of 3C-SiC is on the order of  $10^{16}$  cm<sup>-3</sup>. Fabrication overview is summarized in Fig. 2. Source/drain (S/D) region was formed by multistep ion implantation of P (30-180 keV) and subsequent activation annealing at  $1200^{\circ}$ C. The gate stack was formed by the same method with our former study [2]. After substrate cleaning,  $Al_2O_3$  by ALD and  $SiO_2$  by ECR plasma sputtering were deposited as a gate dielectric. Next, post deposition annealing (PDA) was performed at  $500^{\circ}$ C in  $N_2$  ambient. Al electrode was formed by thermal evaporation, and it was patterned for gate electrode by lithography and wet etching.

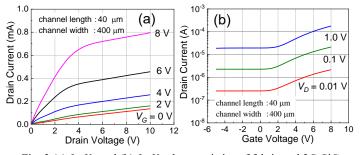

Figures 3(a) and 3(b) show  $I_D$ - $V_D$  and  $I_D$ - $V_G$  characteristics of the fabricated MOSFET, respectively. They showed typical MOSFET operation curve, thus the SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> gate dielectric successfully controlled inversion carrier. However, leakage current at S/D junction is large. S/D formation by ion implantation must be optimized in the next step.

## 3. Fixed charge ( $Q_{\rm fix}$ ), interface dipole ( $\delta_{ m dipole}$ ) analysis

The substrate used for charge analysis in the gate stack was (111) oriented n-type 3C-SiC epitaxially grown on n-Si (111) substrate. Donor (nitrogen) concentration of 3C-SiC is on the order of  $10^{16}$  cm<sup>-3</sup>. In this study, we fabricated lateral MOS capacitors and the fabrication detail is the same with MOSFET fabrication. In Fig. 4, the principle of  $Q_{\rm fix}$  and  $\delta_{\rm dipole}$  evaluation is illustrated. If non-mobile charges in the gate stack are centralized at interfaces and bulk charges can be negligible,  $V_{\rm fb}$  can be expressed by the equation (1) in Fig. 4 and  $V_{\rm fb}$ -EOT plot shows liner relationship [3]. By changing SiO<sub>2</sub> thickness (EOT<sub>1</sub>) and Al<sub>2</sub>O<sub>3</sub> thickness (EOT<sub>2</sub>), we can evaluate  $Q_{\rm fix1}$  and  $Q_{\rm fix2}$  from the slope of  $V_{\rm fb}$ -EOT<sub>1</sub> and  $V_{\rm fb}$ -EOT<sub>2</sub> plot. Vertical intercept corresponds  $\delta_{\rm dipole}$ .

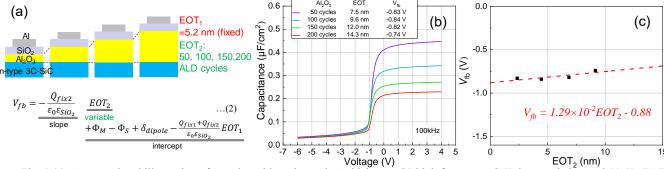

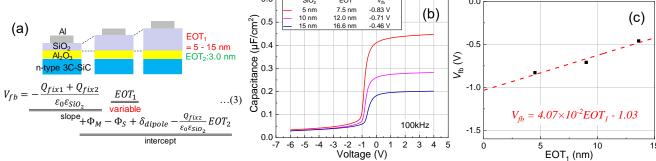

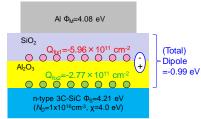

Figure 5(b) shows high frequency (100 kHz) C-V characteristics for samples with various Al<sub>2</sub>O<sub>3</sub> thickness. Typical ntype C-V curves were obtained for all samples, and V<sub>fb</sub> shifts to positive direction with increasing EOT. V<sub>fb</sub>-EOT<sub>2</sub> plots for these samples are summarized in Fig. 5(c). It shows good liner relationship which means the effect of bulk charges are weak. Qfix2 located at Al2O3/SiC interface are obtained as - $2.77 \times 10^{11}$  cm<sup>-2</sup> from the slope. Similarly, *C-V* characteristics and  $V_{\rm FB}$ -EOT<sub>1</sub> plot for the samples with various SiO<sub>2</sub> thickness are shown in Figs. 6(b) and 6(c), respectively. From the slope of Fig. 6(c) and  $Q_{\text{fix2}}$ ,  $Q_{\text{fix1}}$  located at SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> interface was obtained as -5.96×10<sup>11</sup> cm<sup>-2</sup>. By using workfunctions of 3C-SiC (4.21 eV) [4] and Al (4.08 eV),  $\delta_{\text{dipole}}$  is calculated as -0.99 eV. Analyzed charge distribution is illustrated in Fig. 7. Since the dipole strength is relatively large, material (especially gate electrode) and process should be well designed for device application.

### 4. Conclusions

We demonstrated operation of n-MOSFET with  ${\rm SiO_2/Al_2O_3}$  gate dielectric on (111) oriented 3C-SiC. We also analyzed internal charge of the same gate dielectric. The  ${\rm SiO_2}$  and  ${\rm Al_2O_3}$  have negative  $Q_{\rm fix}$ , and the gate stack includes large dipole of -0.99 eV. This large dipole should be considered for device application.

Fig. 1 (a) C-V characteristics and (b) D<sub>it</sub> distributions for 3C-SiC MOS capacitors with various structures [2].

Fig. 2 Fabrication procedure and cross sectional illustration of 3C-SiC n-MOSFET.

$V_{fb} = \Phi_M - \Phi_S + \delta_{dipole} - \frac{Q_{fix2}}{\varepsilon_0 \varepsilon_{SiO_2}} (EOT_1 + EOT_2) - \frac{Q_{fix1}}{\varepsilon_0 \varepsilon_{SiO_2}} EOT_1$   $\Phi_M, \Phi_S; \text{ workfunction of the gate electrode and the semiconductor}$   $\Delta_{\text{apole: total dipole in the gate stack}$   $Q_{\text{fix.}} EOT_1; \text{ fixed charge and EOT of the top gate dielectric}$   $Q_{\text{fix.}} EOT_2; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_2; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_2; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_2; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_2; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_2; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_2; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_2; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_2; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_2; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_2; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_2; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_3; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_3; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_3; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_3; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_3; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_3; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_3; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_3; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_3; \text{ fixed charge and EOT of the bottom gate dielectric}$   $Q_{\text{fix.}} EOT_3; \text{ fixed charge and EOT of the bottom gate dielectric}$

Fig. 3 (a)  $I_D$ - $V_D$  and (b)  $I_D$ - $V_G$  characteristics of fabricated 3C-SiC n-MOSFET with SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> gate dielectric.

Fig. 4 Sample cross-sectional illustration and  $V_{\rm FB}$  equation.

Fig. 5 (a) Cross sectional illustration of samples with various Al<sub>2</sub>O<sub>3</sub> thickness, (b) high frequency C-V characteristics, and (c) V<sub>fb</sub>-EOT<sub>2</sub> plot for Q<sub>fix2</sub> and  $\delta$ <sub>dipole</sub> estimation.

Fig. 6 (a) Cross sectional illustration of samples with various SiO<sub>2</sub> thickness, (b) high frequency C-V characteristics, and (c) V<sub>fb</sub>-EOT<sub>1</sub> plot for Q<sub>fix1</sub> estimation.

Fig. 7 Analyzed charge distribution in this study.

**Acknowledgement** Prof. Baba in CMS, Kyushu institute of technology kindly supported for ion implantation.

#### References

- [1] S. Nishino et al., Appl. Phys. Lett., 42 (1983) 460.

- [2] K. Yamamoto et al., SSDM2018, p. 871.

- [3] H. Kamata et al., Appl. Phys. Lett., 110 (2017) 102106.

- [4] J. Kuriplach et al., Phys. Rev. B, 59 (1999) 1948.