# Effects of Plasma Nitrided Trilayer High-k Gate Dielectric on Electrical Characteristics of FinFET

Kuan-Yu Lai, Kuei- Shu Chang-Liao\*, Yan-Lin Li, Dun-Bao Ruan, Shang-Hua Hsu, Ying-Zhuang Chien, and Bo-Xun Lu

Department of Engineering and System Science, National Tsing Hua University, Hsinchu 30013, Taiwan, R.O.C.

\*Tel: +886-3-5742674, E-mail: lkschang@ess.nthu.edu.tw

#### Abstract

The stacked high-k gate dielectric on FinFET is rarely seen, although its application on MOSFET was proposed to reduce equivalent oxide thickness. A higher on-current, a higher on/off current ratio, and a smaller subthreshold swing value can be achieved by a TiO2 inserted trilayer gate dielectric. Since the gate leakage current and reliability characteristics of FinFETs are degraded due to the inserted TiO2, a HfON inserted at Si/high-k interface is helpful to reduce gate leakage current and improve reliability.

#### 1 Introduction

The high dielectric constant (k) film is widely used as gate oxide in MOSFETs for sub-40 nm technology node. A gate dielectric with a higher k than HfO2 is desirable to reduce the equivalent oxide thickness (EOT). The dielectric constant of TiO<sub>2</sub> can be up to 80 [1], which is 3.2 times higher than that of HfO<sub>2</sub> [2]. However, it was reported that TiO<sub>2</sub> is apt to diffuse into the channel interface during a high temperature process [3], inducing a large gate leakage current. The leakage current in gate dielectric increases with increasing the contents of TiO<sub>2</sub> [2]. Therefore, a HfO<sub>2</sub> with good thermal stability added at the high-k/channel interface is useful to reduce the diffusion of TiO2 into the channel. In addition, a HfON formed by HfO2 treated with NH3 plasma is proposed to reduce both the EOT and gate leakage current, although its bandgap slightly decreases [4]. In this work, four stacked combinations of HfO2 and/or TiO2 as the gate dielectric on electrical characteristics of FinFET were investigated. A HfON formed by HfO2 treated with NH3 plasma was also studied to reduce both the EOT and gate leakage current.

#### 2 Experiments

FinFETs were fabricated on 6-inch p-type SOI (100) wafers. The patterns of dummy fins were defined by I-line lithography. Reactive ion etching (RIE) process was performed to form four parallel fins with a fin height of  $\sim\!40$  nm. Then, a trimming was performed on the fins with H<sub>2</sub> plasma for 300 s. Afterwards, the SiO<sub>2</sub> IL was formed in H<sub>2</sub>O<sub>2</sub> solution at 75 °C for 10 min. Then, a 4 nm thick HfO<sub>2</sub>, a 4 nm thick HfON, a 1.5 nm/2.0 nm/0.5 nm thick HfO<sub>2</sub>/TiO<sub>2</sub>/HfO<sub>2</sub> (HfO<sub>2</sub>TiHf), and a 1.5 nm/2.0 nm/0.5 nm thick HfO<sub>2</sub>/TiO<sub>2</sub>/HfO<sub>2</sub> (HfONTiHf) were deposited by an atomic layer deposition (ALD). Afterward, a 100-nm thick TiN film was deposited by

sputtering to serve as metal gate. After patterning gate stack, phosphorous implantation (at 40 keV for a dose of  $5 \times 10^{15}$  cm<sup>-2</sup>) and activation (750 °C for 30 s) were performed on all samples. Passivation and metallization processes were performed, followed by a sintering at 400 °C for 30 min to complete the device fabrication. The sample splits are shown in Table 1.

### 3 Results and Discussion

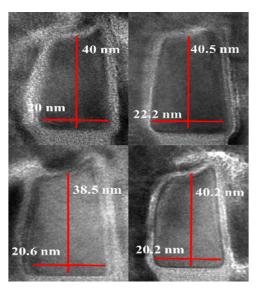

Fig. 1 shows transmission electron microscopy (TEM) images of FinFET structure. The height and width of fin channel are about 40 nm and 20 nm, respectively. The thickness of gate dielectric is ~4.0 nm for all samples, which can also be seen from the TEM images.

Table. 1: Sample splits of FinFETs in this work

| Sample              | HfO <sub>2</sub>        | HfON        | HfO₂TiHf                                                                | HfONTiHf                                                   |

|---------------------|-------------------------|-------------|-------------------------------------------------------------------------|------------------------------------------------------------|

| Sinter              | 400 °C 30 min           |             |                                                                         |                                                            |

| Contact             | Al-Si-Cu 200nm          |             |                                                                         |                                                            |

| Activation          | RTA 600°C 30s           |             |                                                                         |                                                            |

| Metal gate          | TiN 100nm               |             |                                                                         |                                                            |

| High-k              | HfO <sub>2</sub><br>4nm | HfON<br>4nm | HfO <sub>2</sub> +TiO <sub>2</sub> +HfO <sub>2</sub><br>1.5nm+2nm+0.5nm | HfON+TiO <sub>2</sub> +HfO <sub>2</sub><br>1.5nm+2nm+0.5nm |

| Trimming            | 300s H <sub>2</sub>     |             |                                                                         |                                                            |

| Channel<br>material | Single Crystal-Si       |             |                                                                         |                                                            |

| Substrate           | SOI                     |             |                                                                         |                                                            |

Fig.1: TEM images of FinFETs with (a) HfO<sub>2</sub>, (b) HfON, (c) HfO<sub>2</sub>TiHf and (d) HfONTiHf gate stacks in this work.

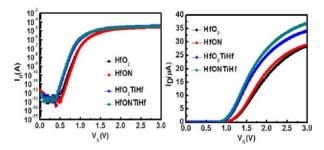

Fig. 2 shows (a) drain current (in log) versus gate voltage (I<sub>d</sub>-V<sub>g</sub>) and (b) drain current (in linear) versus gate voltage (I<sub>d</sub>-V<sub>g</sub>) of FinFETs with HfO<sub>2</sub>, HfON, HfO<sub>2</sub>TiHf and HfONTiHf gate stacks, respectively. The n-FinFET with stacked high-k HfONTiHf has the highest on current about 3.7x10<sup>-5</sup>A. However, the HfON sample has the lowest off current about 2.8x10<sup>-13</sup>A, and its on/off current ratio is about 8 orders. The subthreshold swing (S.S.) values of FinFETs were also extracted from the I<sub>d</sub>-V<sub>g</sub> curves. The S.S. values of devices with HfO<sub>2</sub>, HfON, HfO2TiHf, and HfONTiHf gate dielectric are 72.13, 70.84, 68.93, and 68.92 mV/dec, respectively. Hence, it is found that the S.S. value of FinFET can be reduced with a TiO2 inserted trilayer high-k gate dielectric stack. Besides, it is clear from Fig. 2(b) that devices with a TiO<sub>2</sub> inserted trilayer high-k gate dielectric have higher drain currents. The improvement can be attributed to the higher dielectric constant of titanium oxide than that of hafnium oxide so that the EOT of TiO<sub>2</sub> inserted gate dielectric stack decreases. In addition, the devices with HfON in high-k gate stack have higher drain currents than those with HfO2 one, because the k value of HfON is higher than that of HfO<sub>2</sub> one.

Fig. 2 (a)  $I_d$ - $V_g$  in log curves and 2 (b)  $I_d$ - $V_g$  in linear curves for FinFETs with HfO<sub>2</sub>, HfON, HfO<sub>2</sub>TiHf and HfONTiHf gate stacks.

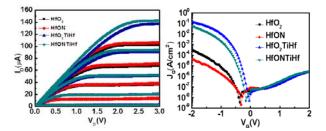

Fig. 3 shows (a) drain current versus drain voltage (I<sub>d</sub>-V<sub>d</sub>) and (b) gate leakage current versus gate voltage (J<sub>g</sub>-V<sub>g</sub>) curves of FinFETs with HfO<sub>2</sub>, HfON, HfO<sub>2</sub>TiHf and HfONTiHf gate stacks, respectively. It is found in Fig. 3(a) that the drive current of device with both titanium oxide-inserted gate dielectric stack and HfON are the highest among all samples. The higher drive current can be due to the higher k value. In Fig. 3(b), the gate leakage current of device with hafnium oxide is much lower than that with titanium oxide. The gate leakage current of device with a HfON can be even lower, thanks to the reduced oxygen vacancy by plasma nitirdation. Besides, the high leakage current of the TiO<sub>2</sub> dielectric layer can be due to the small bandgap compared with hafnium oxide. In addition, titanium is easy to diffuse during thermal process, resulting in a leakage path.

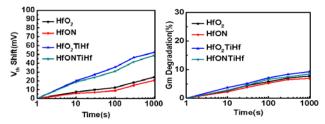

Fig. 4 shows (a) threshold voltage shift (V<sub>th</sub>-shift) and (b) degradation of maximum trans-conductance (Gm,max) versus stress time at a constant voltage stress (E=9 MV/cm) for FinFETs with HfO<sub>2</sub>, HfON, HfO<sub>2</sub>TiHf and HfONTiHf gate stacks. The Vt-shift values of devices with TiO<sub>2</sub> stacked gate dielectric are obviously larger. Some defects are formed between the interface of titanium dioxide and hafnium oxide. Consequently, some

Fig. 3 (a) I<sub>d</sub>-V<sub>d</sub> curves and 3 (b) J<sub>g</sub>-V<sub>g</sub> curves for FinFETs with HfO<sub>2</sub>, HfON, HfO<sub>2</sub>TiHf and HfONTiHf gate stacks.

hot electrons are trapped in these defects. On the other hand, the Vt-shift values of devices can be reduced by a HfON stacked gate dielectric. The improvement can be again attributed to the reduced oxygen vacancy in HfO<sub>2</sub> by plasma nitirdation. As for the Gm degradation, all devices in this work show the similar results, suggesting the high-k/Si interface is not affected by the high-k gate stack.

Fig. 4 (a)  $V_{th\text{-shift}}$  and (b)  $G_{m\text{-max}}$  degradation versus F-N stress time for FinFETs with HfO<sub>2</sub>, HfON, HfO<sub>2</sub>TiHf and HfONTiHf gate stacks.

#### 4 Conclusions

The stack combinations of HfO<sub>2</sub> and/or TiO<sub>2</sub> as the gate dielectric on electrical characteristics of FinFET were investigated in this work. It is found that FinFET with a TiO<sub>2</sub> stacked gate dielectric has a large drain current, higher on/off current ratio, and a smaller S.S. value. A HfON formed by HfO<sub>2</sub> treated with NH<sub>3</sub> plasma is shown to reduce both the EOT and gate leakage current. Therefore, a titanium oxide-inserted gate dielectric stack and HfON are promising to improve performance of FinFET.

## References

- [1] S. J. Rhee et al., "Improved electrical and material characteristics of hafnium titanate multi-metal oxide n-MOSFETs with ultra-thin EOT (/spl sim/8/spl Aring/) gate dielectric application,", IEEE IEDM, (2004), pp. 837-840.

- [2] S. J. Rhee et al., "Optimization and reliability characteristics of TiO/sub 2//HfO/sub 2/multi-metal dielectric MOSFETs," VLSI Technology, (2005), pp. 168-169.

- [3] J. Huang et al., "Gate first high-k/metal gate stacks with zero SiO x interface achieving EOT= 0.59 nm for 16nm application," VLSI Technology, (2009), pp. 34-35.

- [4] C. Lai et al., "Very low voltage SiO<sub>2</sub>/HfON/HfAIO/TaN memory with fast speed and good retention," VLSI Technology, (2006), pp. 44-45.