# Impact of Low Temperature Formed GeO<sub>x</sub>/Al<sub>2</sub>O<sub>3</sub> Tunneling Layer on Reliability of Junctionless Poly-Ge Charge-Trapping Flash Memory Device

Te-Yu Chiang<sup>1</sup>, Kuei-Shu Chang-Liao<sup>1\*</sup>, Hsin-Kai Fang<sup>1</sup>, Po-Yao Lin<sup>1</sup>, Wen-Hsien Huang<sup>2</sup>, Chang-Hong Shen<sup>2</sup> and Jia-Min Shieh<sup>2</sup>

<sup>1</sup> Department of Engineering and System Science, National Tsing Hua University No. 101, Section 2, Kuang-Fu Road, Hsinchu, Taiwan, R.O.C. \*E-mail: lkschang@ess.nthu.edu.tw <sup>2</sup> Taiwan Semiconductor Research Institute No.26, Prosperity Road I, Hsinchu Science Park, Hsinchu, Taiwan, R.O.C.

### **Abstract**

Operation characteristics of poly-Ge charge-trapping flash memory devices with low temperature formed GeO<sub>x</sub>/Al<sub>2</sub>O<sub>3</sub> tunneling layer were studied. Similar program/erase speed are found for devices with or without GeO<sub>x</sub> interfacial tunneling layer. Without any operation speed degradation, reliability characteristics are improved by O<sub>2</sub> plasma treatment and Al<sub>2</sub>O<sub>3</sub> tunneling layer since the interfaces quality in tunneling layer is improved by additional GeO<sub>x</sub> layer.

## 1. Introduction

Due to the fast increase demands of non-volatile memory market, polycrystalline channel has been widely applied on high density flash devices [1]. Since polycrystalline Ge (Poly-Ge) based MOS device has caught lots of attention in recent years [2], it is likely a promising channel material to flash devices for high density or embedded memory applications due to its low process temperatures. On poly-Ge devices, the interfacial layer may play an important role since the performance of Ge based device is very sensitive to the quality of GeO<sub>x</sub>. An interfacial GeO<sub>x</sub> can suppress the undesirable Ge diffusion into gate dielectrics. However, the additional oxide layer may slow down the operation speed of poly-Ge chargetrapping (CT) flash memory. An addition interface in tunneling layer may also affect the reliabilities of CT flash device. The impact of GeO<sub>x</sub> on poly-Ge CT flash devices is rarely seen yet. In this work, poly-Ge CT devices with different stack tunneling layers are investigated. Different tunneling layer was formed on poly-Ge channel. Operation characteristics of poly-Ge CT devices with 1. pure thermal atomic layer deposition (ALD) formed Al<sub>2</sub>O<sub>3</sub> tunneling layer (A), 2. O<sub>2</sub> plasma formed GeO<sub>x</sub> and thermal formed Al<sub>2</sub>O<sub>3</sub> (GA), and 3. O<sub>2</sub> plasma formed GeO<sub>x</sub> and plasma enhance formed Al<sub>2</sub>O<sub>3</sub> (GPA) stacked tunneling layer are studied and compared.

# 2. Device Fabrication

A nanocrystalline-Ge film was deposited after a series of  $SiO_2$  and  $Si_3N_4$  layer deposition. Then, a laser annealing (LA) was performed to increase the grain size. Implantation and activation were performed after the LA process. Then the poly-Ge active region formation is very similar as in [3]. A thin  $GeO_x$  buffer tunneling layer was then grown on the surface of poly-Ge by an  $O_2$  plasma treatment in ALD system

for **GA** and **GPA** devices. Then all samples were sent to deposited an Al<sub>2</sub>O<sub>3</sub> tunneling layer in thermal or plasma enhance mode by ALD system. HfO<sub>2</sub> trapping layer and Al<sub>2</sub>O<sub>3</sub> blocking layer were sequentially deposited. Gate formation, passivation, and metallization were performed as the same as in [4].

### 3. Results and Discussion

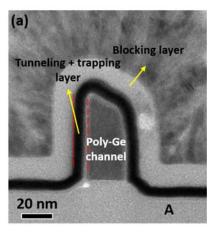

Fig. 1 (a) Cross-sectional TEM images of poly-Ge channel (b) EDS mapping profile of poly-Ge CT flash device.

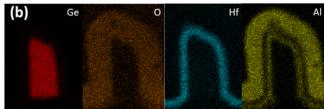

Fig. 1 (a) depicts the transmission electron microscopy (TEM) images of poly-Ge channel in  $\bf A$  device. Fig. 1 (b) present the Energy-dispersive X-ray spectroscopy (EDS) mapping profile of  $\bf A$  device. The trapping and blocking dielectrics layers can be clearly seen and identified in TEM image and EDS profile. Initial  $\bf I_d$ - $\bf V_g$  characteristic of all samples with different  $\bf V_d$  and temperature are shown in Fig. 2. The GA device shows best transfer characteristics and with best subthreshold swing (S.S.) due to better interface quality, indicating that the  $\bf Al_2O_3$  in tunneling layer formed by thermal

Fig. 2 Initial  $I_d$ - $V_g$  characteristics of (a) A, (b) GA and (c) GPA poly-Ge CT flash devices (d) Subthreshold swing comparison of all devices in different temperature.

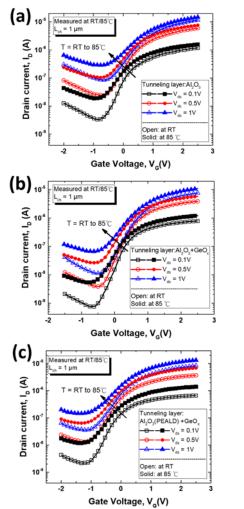

Fig. 3(a) Program and (b) erase speed of A, GA and GPA poly-Ge CT flash device.

mode has better  $GeO_x/Al_2O_3$  quality than plasma enhance mode. The program/erase speeds of all devices are shown with  $V_g=\pm 14$  and  $\pm 16$  V in Fig. 3(a)-(b). The programming/erasing (P/E) operations in this work were all performed by the Fowler–Nordheim (FN) tunneling mechanism. Despite the devices are with different tunneling layer, the program/erase speed of all devices does not show much difference, which can be attributed to the extremely short F N mean free path in  $GeO_x$  for GA and GPA devices during program/erase operation. The retention characteristics of A, GA

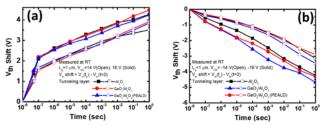

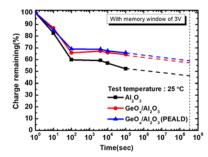

Fig. 4 Retention characteristic of A, GA and GPA poly-Ge CT flash device.

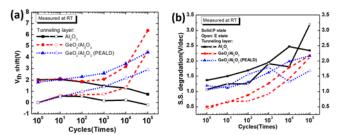

Fig. 5 (a)Endurance characteristic and (b)S.S. degradation of A, GA and GPA poly-Ge CT flash device.

and **GPA** devices is shown in Fig. 4. Both **GA** and **GPA** devices have better retention characteristic, suggesting the GeO<sub>x</sub> was formed by O<sub>2</sub> plasma treatment and effectively reduce the chance of trapped charge escape from trapping layer. The endurance characteristics of all devices is shown in Fig. 5(a). The initial window of all devices was about 2 V. Devices with GeO<sub>x</sub> exhibit larger memory even after 10<sup>5</sup> program/erase cycle. On the contrary, the memory window of **A** device narrowed to less than 1 V. However, the addition interface in tunneling layer of **GA** and **GPA** may trap extra charges as the P/E cycle increase, which cause the V<sub>th</sub> of program and erase state become more positive. Fig. 5(b) present the S.S. degradation of all devices. Without the GeO<sub>x</sub> interfacial tunneling layer, the S.S. of **A** device remains the largest of all device.

# 4. Conclusions

Operation characteristics of poly-Ge CT flash memory devices with different low temperature formed GeO<sub>x</sub>/Al<sub>2</sub>O<sub>3</sub> tunneling layer are studied in this work. Similar operation speed and improved retention characteristics are achieved owning to additional GeO<sub>x</sub> between Al<sub>2</sub>O<sub>3</sub> tunneling layer and poly-Ge channel. Therefore, a GeO<sub>x</sub> interfacial tunneling can improve interface quality and is necessary for poly-Ge CT flash memory.

## References

- [1] Hang-Ting Lue et al., VLSI Symp. Tech. Dig (2010) 131.

- [2] Chan-Yu Liao et al., IEEE Electron Device Lett. 39 (2018)

- [3] Hsin-Kai Fang et al., Microelectronics Reliability. 91, (2018) 319.

- [4] Chun-Yuan Chen *et al.*, IEEE Electron Device Lett, (2013) 993.