# Optimal Bias Condition of Dummy WL for Sub-Block Erase Operation in 3D NAND Flash Memory

## Youngseok Jeong, Ilsik Ham and Myounggon Kang

Dept. of Electronics Engineering, Korea National University of Transportation, Room No.307, IT building, 50 Daehak-ro, Chungju-si, Chungbuk 27469, Republic of Korea Phone: +82-43-841-5164 E-mail: mgkang@ut.ac.kr

#### **Abstract**

NAND Flash memory inherently performs erase operation in block unit. The block size of 3D NAND flash memory is enlarged due to an increase of the number of layers. Because of the large size block, which must be erased all at once, it leads to increase program/erase (P / E) cycling in 3D NAND flash memory. To solve this problem, a sub-block erase operation is that dummy word line (DWL) is specified and two blocks are separated and operated based on DWL as a block. However, due to the capacitive coupling effect caused by the DWL, erase operation in the word line (WL) adjacent to the DWL is not normally performed. Therefore, we propose an optimal bias condition for sub-block erase operation using DWL in 3D NAND flash memory.

#### 1. Introduction

NAND flash memory is advantageous in high integration and large capacity storage. It can be used for large-capacity applications because it can minimize cell size. Therefore, Flash memory has been rapidly growing in demand for high-density NAND flash memory devices such as smart phones, tablet PCs, and solid-state drives (SSD) due to its rapid speed, small size, and low power consumption over the past 20 years [1].

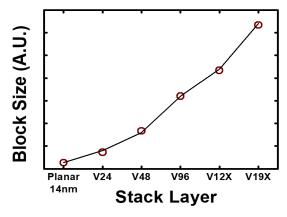

Fig. 1. Block size increase rate with increasing number of 3D NAND flash layers.

In case of 3D NAND flash memory, it is possible to save a lot of data and to increase the integration density as the number of vertical layers increases. However, as shown in Fig. 1 the block size of 3D NAND flash memory is increased, as the number of layers is increased [2-8]. For example, when the 64 layers 3D NAND flash memory is split into two blocks, the string select line (SSL) - 32string - ground select line (GSL) - SSL - 32string - GSL structure is used. Due to the

added size of SSL and GSL, the area overhead increases by more than 10%. Also, as the erase block (EB) size increases, large size blocks are erased all at once, resulting in an increase in P / E cycling. Therefore, there is a need for a technology to realize a small block size that can reduce P / E cycling without increasing the area overhead. Therefore, we propose the optimal voltage for sub-block erase operation using DWL using technology computer-aided design (TCAD) simulation (AT-LAS Silvaco<sup>TM</sup>) in 3D NAND flash memory [9].

### 2. Experimental methods

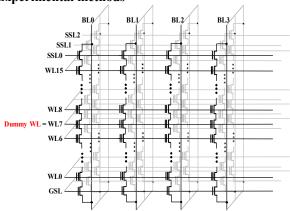

Fig. 2. 3D NAND flash memory string with 16 WL, 3 SSL and 4 BL

Fig. 2 shows the structure of 16 layers 3D NAND flash memory and consists of SSL, WL0  $\sim$  15 and GSL. SSL and bit line (BL) are shared in 3D NAND flash memory, so the block size can be increased as the number of WL increase. For the experiment, WL7 is used as DWL for sub-block erase operation.

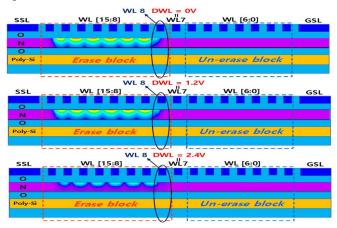

Fig. 3. Simplified vertical diagram of trap hole charge density in 3D NAND flash memory using DWL.

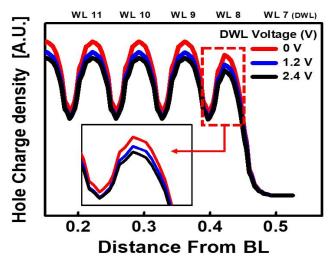

Fig. 4. Trap hole charge density according to DWL voltage.

The experiment of sub-block erase operation using DWL was designated as un-erase block (UB), WL0 ~ 6 and EB, WL8 ~ 15 as shown in Fig. 3. Also, WL7 is used as DWL for sub-block erase operation. Fig. 3 is a vertical diagram of the hole concentration trapped in the nitride according to DWL voltage = 0V, 1.2V, and 2.4V, respectively. As the voltage of DWL increased, the hole concentration trapped in nitride decreased. Fig 4. shows trap hole capture density according to DWL voltage. The hole concentration of WL8 (WL adjacent to DWL) is lower than that of WL9  $\sim$  15. In this case, a cell affected by neighboring cells is called a victim cell, and a cell to cell interference (CCI) [10-12]. However, when DWL voltage = 0V, the hole concentration of WL8 is not only the highest but also the hole concentration of WL9  $\sim$  15 is the highest. It was found that erase was performed most properly when DWL = 0V in 3D NAND flash memory.

|                                | Program                                 | Read                       | Erase            | Erase<br>Verify            |

|--------------------------------|-----------------------------------------|----------------------------|------------------|----------------------------|

| SSL                            | V <sub>CC</sub>                         | $V_{READ}$                 | Floating         | V <sub>READ</sub>          |

| GSL                            | 0V                                      | $\mathbf{V}_{\text{READ}}$ | Floating         | $\mathbf{V}_{\text{READ}}$ |

| Select WL<br>/ Un-Select<br>WL | V <sub>PGM</sub><br>/ V <sub>PASS</sub> | Vr<br>/ V <sub>READ</sub>  | 0V<br>/ Floating | 0V<br>/ V <sub>READ</sub>  |

| Select BL<br>/ Un-Select<br>BL | 0V<br>/ V <sub>CC</sub>                 | $V_{BL}$ / $0V$            | Floating         | $V_{\rm BL}$ / $0  m V$    |

| Dummy WL                       | V <sub>PASS</sub>                       | V                          | <b>0V</b>        | $V_{READ}$                 |

| CSL                            | 0V                                      | <b>0V</b>                  | Floating         | 0V                         |

Table. 1. The bias condition of sub-block erase operation in 3D NAND flash memory.

Table 1 shows the bias condition for performing the subblock erase operation. It is similar to the basic operating voltage of planar NAND Flash memory [13]. However, 0V is applied to the DWL in erase operation.

### 3. Conclusions

In this paper, WL7 is designated as DWL for erase operation in block unit, and a structure in which one block is divided into two blocks based on DWL is confirmed. However, because of the CCI phenomenon, the erase operation was not properly performed. In order to solve this problem, we experimented the optimal bias for sub block erase operation using DWL in 3D NAND flash memory. As a result, erase was performed most properly when DWL = 0V. Sub-block erase technology can reduce the area overhead increase by using only WL without adding GSL and SSL. Also, P / E cycling can be significantly reduced in 3D NAND flash memory.

#### Acknowledgements

This research was supported by the MOTIE (Ministry of Trade, Industry & Energy (10085645) and KSRC (Korea Semiconductor Research Consortium) support program for the development of the future semiconductor device and in part by National Research Foundation of Korea(NRF) funded by the Ministry of Education(2018R1A6A1A03023788) and Korea Institute for Advancement of Technology (KIAT) grant funded by the Korea Government (MOTIE) (N000P00008500, The Competency Development Program for Industry Specialist).

## References

- Gregory Wong, "Market and applications for NAND Flash memories," in inside Flash Memories, Rino Micheloni, Luca Crippa and Alessia Marelli, NY:Springer, 2010, ch. 1, pp. 1

- [2] Y. Kim, J.-G. Yun, S. H. Park, W. Kim, J. Y. Seo, M. Kang, K.-C. Ryoo, J.-H. oh, J.-H. Lee, H. Shin, and B.-G. Park, "Three-Dimensional NAND Flash Architecture Design Based on Single-Crystalline STacked ARray," IEEE Trans. Electron Devices, vol. 59, no. 1, pp. 35-45, Jan. 2012.

- [3] J. Jang, H. S. Kim, W. Cho, H. Cho, J. Kim, S. I. Shim, Y. Jang, J. H.Jeong, B. K. Son, D. W. Kim, K. Kim, J. J. Shim, J. S. Lim, K. H. Kim, S.Y. Yi, J. Y. Lim, D. Chung, H. C. Moon, S. Hwang, J.W. Lee, Y. H. Son, U. I. Chung, and W. S. Lee, "Vertical cell array using TCAT (Terabit Cell Array Transistor) technology forultra high density NAND flash memory," in VLSI Symp. Tech. Dig., pp. 192-193, month 2008.

- [4] Y. Kim, M. Kang, S. H. Park, and B. -G. Park, "Three-Dimensional NAND Flash Memory Based on Single-Crystalline Channel Stacked Array," IEEE Electron Device Lett., vol. 34, no. 8, pp. 990-992, July. 2013.

- [5] Y. Kim and M. Kang, "Down-coupling phenomenon of floating channel in 3D NAND flash memory", IEEE Electron Device Lett., vol. 37, no. 12, pp. 1566–1569, Dec. 2016.

- [6] M. Kang and Y. Kim, "Natural Local Self-Boosting Effect in 3D NAND Flash Memory", IEEE Electron Device Lett., vol. 38, no. 9, pp. 1236– 1239, Sept. 2017.

- [7] Y. k. Lee et al. Erasing method in non-volatile memory device@ONLINE, https://www.google.com/patents/US6724661, 05 2002.

- [8] Samsung. Samsung v-nand@ONLINE, http://w ww.samsung.com/semiconductor/products/flash-storage/v-nand/, 2015.

- [9] Atlas User's Manual, Silvaco Version. 5.19.20. [Online]. Available: http://www.silvaco.com/products/tcad/device\_simulation/atlas/atlas.html

- [10] Y. Kim and M. Kang, "Predictive modeling of channel potential in 3-D NAND flash memory", IEEE Trans. Electron Devices, vol. 61, no. 11, pp. 3901-3904, Nov. 2014.

- [11] M. Kang, I. Park, I. Chang, K. Lee, S. Seo, B. -G. Park, and H. Shin, "An accurate compact model considering direct-channel interference of adjacent cells in sub-30-nm NAND flash technologies", IEEE Electron Device Lett., vol. 33, no. 8, pp.1114-1116, Aug. 2012.

- [12] M. Kang, W. Hahn, I. -H. Park, Y. Song, H. Lee, K. Choi, Y. Lim, S.-M. Joe, D. -H. Chae and H. Shin, "A compact model for channel coupling in sub-30 nm NAND flash memory device," Japanese Journal of Applied Physics, vol. 50, no. 10, pp.0204, 2011.

- [13] K.-D. Suh, B.-H. Sug, Y.-H. Lim, J.-K. Kim, Y.-J. Choi, Y.-N. Koh, S.-S. Lee, S.-C. Kwon, B.-S. Choi, J.-S. Yum, J.-H. Choi, J.-R. Kim, and H.-K. Lim, "A 3.3 V 32 Mb NAND flash memory with incremental step pulse programming scheme", IEEE J. Solid-State Circuits, vol. 30, no.11, pp 1149-1156, Nov. 1995.