# Physics in HRS-LRS Switching in Vacancy Modulated Conductive Oxide (VMCO) Memories

Toru Nakanishi<sup>1</sup>, Kenta Chokawa<sup>2</sup>, Masaaki Araida<sup>2,1</sup>, Takashi Nakayama<sup>3</sup> and Kenji Shiraishi<sup>2,1</sup>

<sup>1</sup>Graduate School of Engineering, Nagoya University, Nagoya 464-8603, Japan, <sup>2</sup>Institute of Materials and System for Sustainability, Nagoya University, Nagoya 464-8601, Japan, <sup>3</sup>Graduate School of Science, Chiba University, Chiba 263-8522, Japan,

E-mail: nakanishi.toru@e.mbox.nagoya-u.ac.jp

#### **Abstract**

Vacancy modulated conductive oxide (VMCO) memory is greatly expected as a next generation non-volatile memory. However, the switching mechanism of VMCO memory is still unclear. In this work, we propose a new switching mechanism which can comprehensively reproduce experiments related to VMCO memories. Moreover, we discuss the origin of high on-off switching ratio.

### 1. Introduction

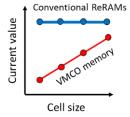

In recent years, resistive switching memories (ReRAMs) has been attracting considerable attention because of the low power consumption and high speed operation. However, conventional ReRAMs form conductive filaments which function as current paths in the oxide film [Fig. 1]. Therefore, they do not have area dependence in current value, and are not suitable for next generation high density memories. However, vacancy modulated conductive oxide (VMCO) memories, in which the current value depends on the area of the device, have been reported and are now attracting a lot of attention for future high density memories [1].

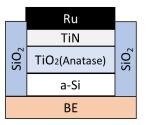

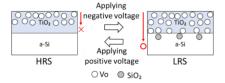

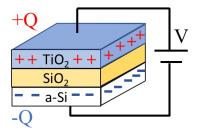

VMCO memories are ReRAMs in which the insulator is anatase type TiO<sub>2</sub>, and the electrodes are TiN and a-Si [Fig. 2]. The most significant features of VMCO memories are the area dependency of the current value as shown in Fig. 3. Therefore, since VMCO memories are suitable for scaling, they are greatly expected as next generation high density nonvolatile memories. Regarding its switching mechanism, it is already considered that oxygen vacancies (Vo) are widely distributed in oxide film as current paths, and when we use rutile type TiO<sub>2</sub> as an insulator, VMCO memories do not work properly. However, the conventional Vo drift model shown in Fig. 4 in which Vo drift by applying voltage is the origin of HRS-LRS switching [1], cannot explain why VMCO behavior appears only in anatase type TiO<sub>2</sub>.

In our previous work, we proposed a new switching model in which interface reaction governs the HRS-LRS switching in VMCO memories [3] [Fig.5, Fig.6]. In this work, we explain why rutile type TiO<sub>2</sub> does not reveal VMCO characteristics. Moreover, we also discuss high on-off switching ratio of VMCO memories.

## 2. Our proposed switching model

First, we explain our switching model for VMCO model in our previous work [3]. We focused on the Vo formation reaction as shown in eq. (1) near  $\text{TiO}_2/\text{a-Si}$  interface.

$$TiO_2 + Si \rightleftarrows TiO_2(2V_0) + SiO_2 \tag{1}$$

In short, if there are Vos near the interface, a low resistance state (LRS) would occur, and if there are no Vos near the interface, a high resistance state (HRS) occur [Fig 5].

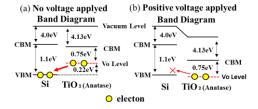

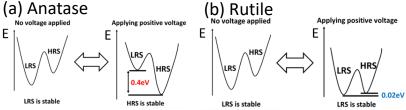

Our first principles results show that formation energies of Vo in anatase type TiO<sub>2</sub> and SiO<sub>2</sub> are 4.41eV and -8.42eV, respectively. It means that the reaction in eq. (1) gives 0.4eV energy loss. According to the band diagrams of anatase type TiO<sub>2</sub> with Vo and Si in Fig. 6(a), however, the electrons which occupy the Vo level transfer to Si, resulting in energy gain. This energy gain exceeds the energy loss in Vo formation reactions. Hence, the Vo formation reaction occur and LRS is more stable. Moreover, when positive voltage is applied, energy gain in electron transfer decrease and HRS is more stable [Fig. 6(b)]. According to the above discussion, it is possible to control the formation and disappearance of Vo by applying a voltage near the TiO<sub>2</sub>/a-Si interface, and HRS and LRS can be switched in VMCO memories. This can naturally explain the experimental behavior of VMCO memories.,

### 3. Discussion

First, we discuss the reason why VMCO memories do not work properly when rutile type TiO<sub>2</sub> is used as oxide film. As the calculation results, we found that 0.22eV energy gain occurs in the Vo formation reaction. Therefore, the Vo formation reaction is spontaneous without considering electron transfer. In other words, the Vo formation reaction proceeds regardless of voltage application and LRS is always more stable [Fig.7(b)]. Hence, LRS and HRS cannot be switched in the case of rutile type TiO<sub>2</sub> and it is considered that VMCO memories does not work properly. As discussed above, our proposed model can naturally explain why VMCO memories with rutile TiO<sub>2</sub> do not work, although conventional Vo drift model cannot explain it [Fig.8].

Next, we discuss the on-off switching ratio of VMCO memories. In our proposed model, LRS and HRS are switched by controlling the formation and disappearance of Vo in TiO<sub>2</sub> near TiO<sub>2</sub>/a-Si interface. However, if the thickness of the layer that Vo is controlled is too thin, electrons tunnel even if there is no Vo. Therefore, the thickness of this layer is critically important for on-off switching ratio. This thickness can be estimated by considering interface dipole as shown in Fig. 9, and it is estimated as 2.65nm when Vo density near interface is  $6.0 \times 10^{20} \text{cm}^{-3}$  by using the equation given in Fig.10. From these results, electrons do not tunnel easily in HRS. Therefore, in our proposed switching model of VMCO memories, high on-off switching ratio is ensured.

## 4. Conclusion

In this work, we proposed the switching model of VMCO memories by considering the reaction near TiO<sub>2</sub>/a-Si interface. In the same way, we also clarified the reason why VMCO memories do not work in the case of rutile type TiO<sub>2</sub> insulator. Moreover, we also confirmed that the high on-off ratio is ensured in VMCO memories described by our model.

### References

[1] B. Govoreanu et al., VLSI Symp. Tech. Digest, p. T132 (2015).

[2] J. Ma et al., IEDM Tech. Digest, p.564, (2016).

[3] Nakanishi et al. Extended Abstract of INFOS (2019).

[4] I. Nakamura et al., Journal of Molecular Catalysis A: Chemical **161**, 205 (2000).

Fig. 1. The switching mechanism of a conventional ReRAM. The ReRAM exhibits LRS when a conductive filament is formed and exhibits HRS when the conductive filament is broken.

Fig. 2. Schematic illustration of VMCO memory [3].

Fig. 3. The area dependency of current value. The current value of VMCO memory decreases when its cell size decreases [3].

Fig. 4. The drift model for VMCO memories. Vos drift by applying a voltage. The red arrows signify current. This model cannot explain the reason why VMCO memories do not work when rutile type  $\text{TiO}_2$  is used.

Fig. 5. Our switching model for VMCO memories. The Vo formation reaction near the interface is controlled by applying a voltage. The red arrows signify current [3].

Fig. 6. (a) Band diagrams of Si and anatase type  $TiO_2$  with Vos [4]. (b) Band diagrams of Si and anatase type  $TiO_2$  with Vos under positive voltage. The energy gain in electron transfer decreases by applying a voltage [3].

Fig. 7. (a) The behavior of VMCO memories by voltage application in the case of using anatase type  $\mathrm{TiO}_2$ . (b) The behavior of VMCO memories by voltage application in the case of using rutile type  $\mathrm{TiO}_2$ . While the stable state can be switched when anatase type  $\mathrm{TiO}_2$  is used, the stable state can not be switched when rutile type  $\mathrm{TiO}_2$  is used.

| Switching<br>model | Anatase type | Rutile type |

|--------------------|--------------|-------------|

| Vo drift<br>model  | 0            | ×           |

| Present<br>model   | 0            | 0           |

Fig. 8. Comparison of Vo drift model and present model. Present model can also explain why VMCO memories do not work when Rutile type TiO<sub>2</sub> is used.

Fig. 9. A state of interface dipole. Near TiO<sub>2</sub>/a-Si interface, TiO<sub>2</sub> is positively charged and a-Si is negatively charged. It is regarded as a parallel plate capacitor.

| $\left[\sigma^2 - \frac{2W\varepsilon\rho}{e^2l} = 0\right]\sigma(/\text{cm}^2) : \text{density}$ |                                                      |  |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------|--|

| Parameter                                                                                         | Parameter                                            |  |

| W: energy stored in capaci                                                                        | W: energy stored in capacitor                        |  |

| ε: dielectric constant of Si                                                                      | $\epsilon$ : dielectric constant of SiO <sub>2</sub> |  |

| ρ: (100) surface density of                                                                       | ρ: (100) surface density of Si                       |  |

| e : elementary charge                                                                             | e : elementary charge                                |  |

| 1: 1ML thickness of (100) Si                                                                      | 1: 1ML thickness of (100) Si layer                   |  |

Fig. 10. The equation for finding number of Vo and value of each parameter.