# Evaluation of Carrier Recombination Lifetime in Silicon Epitaxial Layer by Open Circuit Voltage Decay Method

Shun Sasaki<sup>1</sup>, Noritomo Mitsugi<sup>1</sup>, Shuichi Samata<sup>1</sup>, Wataru Manabe<sup>2</sup>, Masanori Tsukuda<sup>2</sup>, Hiroshi Yamada-Kaneta<sup>2</sup>, and Ichiro Omura<sup>2</sup>

<sup>1</sup>SUMCO Corporation

1-2-1 Shibaura, Minato-ku, Tokyo 105-8634

Phone:+81-3-5444-0808 E-mail: sysasaki@sumcosi.com

<sup>2</sup> Kyushu Institute of Technology

2-4 Hibikino, Wakamatsu-ku, Kitakyushu-shi, 808-0196, Japan

Phone: +81-93-695-6037

### **Abstract**

A new technique of evaluation for the carrier recombination lifetime in silicon epitaxial layer was invented based on the principle of Open Circuit Voltage Decay. PIN diodes that have different junction areas were fabricated on silicon epitaxial wafer and true recombination lifetime in epitaxial layer and surface recombination velocity on sidewall of mesa structure were evaluated.

#### 1. Introduction

The carrier recombination lifetime is an effective parameter to characterize the purity of semiconductor materials and devices. Microwave-Photoconductive (μ-PCD) method is often employed to evaluate difference in recombination lifetime in a wafer or between wafers, by creating two dimensional lifetime map. [1][2]. However the μ-PCD has a difficulty to measure the recombination lifetime of silicon epitaxial layer which adopts the highly-doped substrate. The sheet conductance of epitaxial layer after carrier injection is relatively small as compared to that of highly-doped substrate. Therefore the total decay of sheet conductance from the epitaxial wafer mostly does not change [3]. Differential µ-PCD was also proposed to evaluate the recombination lifetime of thin films [4]. However this method can not completely exclude effect of surface recombination. The Open Circuit Voltage Decay (OCVD) method measures recombination lifetime in the base region in PIN diodes. Accordingly, the carrier recombination lifetime of epitaxial layer can be evaluated by employing the epitaxial layer as the base region of PIN diode [5]. However this method typically uses discrete PIN diode structure. Thus, the structure can never remove the effect of surface recombination on the side wall of PIN diodes. To resolve these problems and difficulties in the conventional techniques, here we try to evaluate true recombination lifetime of the silicon epitaxial layer by taking advantage of the OCVD method.

#### 2. PIN diode structure & Measurement

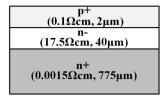

Two silicon epitaxial wafers that have high and low recombination lifetime (Wafer A and Wafer B) were prepared. These wafers are phosphorus-doped 200mm n/n+ silicon epitaxial wafer. Resistivity and thickness are  $17.5\Omega cm$  and

40μm for epitaxial layer, and 0.0015  $\Omega$ cm and 77.5μm for substrate, respectively. Figure.1 shows schematic cross section of the epitaxial layer structure. To fabricate PIN diodes on the silicon wafers, p+ epitaxial layer was grown by Chemical Vapor Deposition (CVD) process, on these epitaxial wafers. Resistivity and thickness of p+ layer are 0.1 $\Omega$ cm and  $\Omega$ μm.

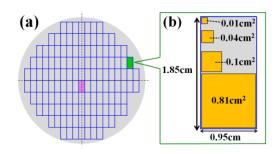

PIN diode mesa structures were fabricated by photolithography and chemical dry etching. Figure.2 (a) shows schematic illustration of patterning on the silicon wafers. Totally, 138 cells were regularly patterned on the epitaxial wafers. Figure.2 (b) shows PIN diodes within a unit cell. One unit cell possesses 4 PIN diodes that have different junction areas: 0.01, 0.04, 0.10, and 0.81 cm<sup>2</sup>. These diodes within a unit cell were employed to remove surface recombination effect on side wall of the mesa structures, which refers at later section.

The OCVD measurement system was connected with manual prober and wafer center (pink filled color area in Fig.2(a)) was measured to compare recombination lifetime between Wafer A and B.

Figure.1 Schematic illustration of the epitaxial layer structure for the OCVD measurement.

Figure.2 Schematic illustrations of (a) pattern on the silicon epitaxial wafers and (b) mesa structures within a unit cell.

# 3. Results

In the OCVD measurement, recombination lifetime in high level injection condition ( $\tau_{hl}$ ) and low level injection condition ( $\tau_{ll}$ ) can be calculated by following equations:.

$$\tau_{hl} = -\frac{2kT/q}{dV/dt}.\tag{1}$$

$$\tau_{ll} = -\frac{kT/q}{dV/dt}.$$

(2)

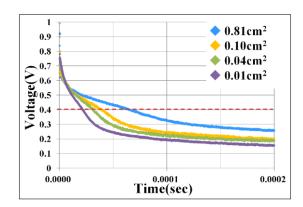

where, k, T, q, V, and t are Boltzmann constant, temperature, elementary charge, measurement voltage, and time. Figure.3 shows measurement results of voltage decay curves in each diode of Wafer B. Inflection point of voltage decay curves was recognized at 0.4V (red dashed line). Therefore,  $\tau_{hl}$  and  $\tau_{ll}$  were estimated from 0.5-0.4V and 0.4-0.3V, by employing slopes of linear approximation lines that are equivalent to the dV/dt. To compare recombination lifetimes of the epitaxial layer in Wafer A and B, the surface recombination effect should be removed. In this experiment, bare silicon which acts as strong surface carrier recombination center exposes on the side wall of mesa structures. True recombination lifetime of the epitaxial layer in high ( $\tau_{bulk,hl}$ ) and low level injection condition ( $\tau_{bulk,ll}$ ) can be calculated from below equations:

$$\frac{1}{\tau_{hl}} = \frac{1}{\tau_{bulk,hl}} + \frac{Sv_s D_a}{V(D_a - Lv_s)}.$$

(3)

$$\frac{1}{\tau_{ll}} = \frac{1}{\tau_{bulk,ll}} + \frac{Sv_s D_p}{V(D_p - Lv_s)} \tag{4}$$

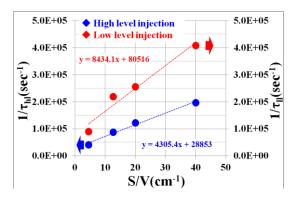

where S, V,  $v_s$ ,  $D_p$ ,  $D_a$ , and L are area of side wall, volume of mesa structure, surface recombination velocity, diffusion coefficient of hole, ambipolar diffusion coefficient, and carrier diffusion length. The true recombination lifetime of epitaxial layer and the surface recombination velocity were obtained from interception and slope of approximation line which is drawn by plotting reciprocal values of lifetime and ratio of S and V, in each mesa structure. Figure. 4 shows  $I/\tau_{hl}$  and  $I/\tau_{ll}$  vs S/V plots (filled circles) and linear approximation lines (dot lines).

The calculation results were summarized in Table I. The true recombination lifetime values of Wafer A are higher than the value of Wafer B. This relationship of the true recombination lifetime values is consistent with before fabrication of PIN diodes for the OCVD. The surface recombination velocity in low level injection is higher than the values in high level injection, in each wafer. This implies carrier injection level dependence of surface recombination velocity [6].

# 4. Conclusion

Evaluation of the carrier recombination lifetime in silicon epitaxial layer was carried out by employing the OCVD method. Unit cells that possess different junction areas of PIN diode mesa structures were regularly fabricated on the silicon epitaxial wafers and were employed to evaluate the true recombination lifetime values in the epitaxial layer, by removing the effect of surface recombination on the side wall of mesa structures. Relationship of the true recombination lifetime values between two wafers showed consistency with before mesa fabrication. As to the surface recombination velocity, dependence of carrier injection level was confirmed.

# 5. Reference

- [1] T. Pavelka et al., ECS Transactions. 25 (2009) 129.

- [2]M. Yli-Koski et al., Solid State Phenom. 108-109 (2005) 643.

- [3] K. Manabe et al., Conference Paper of IEE-SPC. (2017) 7.

- [4] S. Sumie et al., J. Electrochem. Soc. 152 (2005) G99.

- [5] M. Tapajna et al., Serb. J. Electr. 1 Eng. 55 (2004) 239.

- [6] S. J. Robinson et al., J. Appl. Phys. 78 (1995) 4740.

Figure.3 The OCVD measurement results of PIN diodes, within the unit cell of Wafer B.

Figure 4  $1/\tau_{hl}$  and  $1/\tau_{ll}$  vs S/V plots (filled circles) and approximation lines (dot lines) of Wafer A.

Table I Calculation results of  $\tau_{bulk,hl}$ ,  $\tau_{bulk,ll}$ , and  $v_s$ .

|         | -                              | _                              | $v_s$ (cm/sec) |              |

|---------|--------------------------------|--------------------------------|----------------|--------------|

| Wafer   | τ <sub>bulk,hl</sub><br>(μsec) | τ <sub>bulk,ll</sub><br>(μsec) | High<br>level  | Low<br>level |

| Wafer A | 49.27                          | 24.14                          | 535.8          | 665.6        |

| Wafer B | 34.65                          | 12.42                          | 610.0          | 880.4        |