# Switching Characteristic Enhancement of p-type Cu<sub>2</sub>O TFTs

## Dongwoo Kim, I Sak Lee, Sujin Jung, Sung Min Rho, and Hyun Jae Kim

School of Electrical and Electronic Engineering, Yonsei University, 50 Yonsei-ro, Seodaemun-gu, Seoul 03722, Korea

Keywords: oxide TFT, p-type semiconductor, copper oxide

## ABSTRACT

We propose three methods to enhance switching characteristics of p-type  $Cu_2O$  thin film transistors (TFTs) by passivating the copper oxide TFTs with silicon dioxide (SiO<sub>2</sub>) using sputtering, oxidizing the back channel of copper oxide with hypochlorous acid (HCIO), and doping gallium into the  $Cu_2O$  film.

## **1. INTRODUCTION**

Amorphous oxide semiconductor (AOS)-based thin-film transistors (TFTs) have been a target of a considerable attention after the indium-gallium-zinc oxide-based TFTs were developed and announced worldwide by a research group led by Hosono et al [1]. According to that report, the AOS-based TFTs boast remarkable properties compared with widely used amorphous silicon (a-Si)-based TFTs including higher field-effect mobility ( $\mu_{FE}$ ), low off-current, and high transparency. As of today, the AOS-based TFTs are found in commercialized products such as organic light-emitting diode (OLED) displays. However, these extensive researches are limited only to n-type because most oxide semiconducting materials show intrinsically ntype characteristics. Furthermore, p-type oxide semiconductors have holes as carriers that move through the valence band maximum (VBM) which is formed by 2p orbitals of oxygen molecules. This forms many localized states that create heavy effective mass of holes, which cause low hole mobility in p-type oxide semiconductors. Also, oxygen vacancies that naturally form within oxide semiconductors generate electrons that work as trap sites for holes. Thus, only a few researchers have challenged to work on p-type oxide TFTs [2]. Nevertheless, these researchers are essential in developing high performing fully oxide-based complementary metal oxide semiconductor (CMOS) logic circuits to realize low power consuming and rapidly responding devices.

As one of the few representative p-type oxide semiconductors, copper oxides exist in two phases, cuprous oxide ( $Cu_2O$ ) and cupric oxide (CuO), which have different electrical characteristics. Accordingly, there have been various researches to sought out appropriate copper oxide phase for p-type oxide TFTs. Yet, proper switching characteristics for p-type copper oxide TFTs have not been achieved compared with those of n-type AOS-based TFTs.

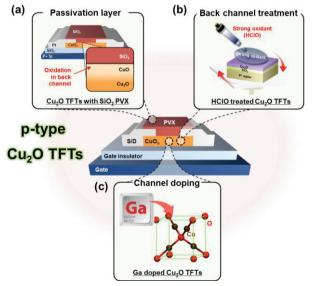

As following Fig. 1., in this study, we present three methods to enhance switching characteristics of p-type

$Cu_2O$  TFTs, which are passivating with silicon dioxide  $(SiO_2)$  to cause oxidation of CuO in back channel during annealing process, using hypochlorous acid (HCIO) to oxidize the back channel [3], and doping gallium in channel to control oxygen vacancy. By adopting these techniques, we could successfully fabricate p-type oxide TFTs with improved electrical performances such as mobility and on/off ratio.

Fig. 1. Schematics of various techniques to enhance switching characteristics for p-type  $Cu_2O$  TFTs; (a)  $Cu_2O$  TFTs w/ silicon dioxide (SiO<sub>2</sub>) passivation, (b) HCIO treated  $Cu_2O$  TFTs, and (c) Ga doped  $Cu_2O$  TFTs.

## 2. EXPERIMENTAL

#### 2.1 Fabrication method of SiO<sub>2</sub> passivated Cu<sub>2</sub>O TFT

To fabricate Cu<sub>2</sub>O TFTs, Cu<sub>2</sub>O was deposited on a p<sup>+</sup>-Si wafer with 120 nm thick SiO<sub>2</sub> using radiofrequency (RF) sputtering with 100 W RF power. After Cu<sub>2</sub>O deposition, we annealed the device at 800°C for 1 min in vacuum followed by Pt source and drain electrodes deposition by sputtering. Then, SiO<sub>2</sub> passivation layer was sputtered with 150 W RF power. Lastly, the device was annealed in air at 200°C for 30 min.

## 2.2 Fabrication method of HCIO treated Cu<sub>2</sub>O TFT

First, we prepared Cu<sub>2</sub>O (0.2 M) solution by dissolving copper (II) nitrate hydrate  $[Cu(NO_3)_2 \cdot xH_2O]$  in 2-

methoxyethanol (2ME). Then, the Cu<sub>2</sub>O thin films were spin-coated on a p<sup>+</sup>-Si wafer with 120 nm thick SiO<sub>2</sub> followed by pre-annealing at 120°C for 5 min. Then, the device was post-annealed at 500°C for 1 h. Next, HCIO solution was spin-coated onto the Cu<sub>2</sub>O layer followed by annealing in air at 300°C for 1 h. After repeating HCIO coating/annealing 4 times, the films were rinsed with deionized water. Finally, Pt source and drain electrodes were deposited by sputtering.

## 2.3 Fabrication method of Ga doped Cu<sub>2</sub>O TFT

For the fabrication of Ga-doped Cu<sub>2</sub>O TFTs, we cosputtered Cu<sub>2</sub>O and Ga<sub>2</sub>O<sub>3</sub> targets simultaneously on a p<sup>+</sup>-Si wafer with 120 nm thick SiO<sub>2</sub> using RF sputtering. RF powers for Cu<sub>2</sub>O and Ga<sub>2</sub>O<sub>3</sub> targets were 100 W and 10 W, respectively. Then, post annealing at 800°C for 1 min in vacuum was done to develop an active layer. Finally, Pt source and drain electrodes were deposited by sputtering.

## 3. RESULTS AND DISCUSSION

#### 3.1 Results of SiO<sub>2</sub> passivated Cu<sub>2</sub>O TFTs

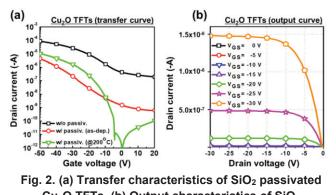

First, the transfer characteristics of SiO<sub>2</sub> passivated Cu<sub>2</sub>O TFTs are shown in Fig. 2 (a). It shows that the Cu<sub>2</sub>O TFT without the passivation shows higher current values for both the on and off currents. However, when SiO<sub>2</sub> passivation was deposited by sputtering, the current level decreased significantly without any annealing. After the annealing at 200°C for 30 min, the switching property improved largely by decreasing the off current by the magnitude of  $10^3$  A. Therefore, the on-off current ratio improved from ~ $10^3$  to ~ $10^8$ . As for Fig. 2 (b), it shows the output characteristics of SiO<sub>2</sub> passivated Cu<sub>2</sub>O TFT that is annealed at 200°C for 30 min. As the data shows, the drain current is saturated for all applied gate voltages.

Cu<sub>2</sub>O TFTs. (b) Output characteristics of SiO<sub>2</sub> passivated Cu<sub>2</sub>O TFT annealed at 200°C for 30 min.

Fig. 3 shows the reason behind this switching property improvement. Firstly, when  $SiO_2$  was deposited on top of the TFT, damage occurs due to sputtering. This damage breaks the bonds between Cu and O [4]. Thus, this induces formation of many defects such as weak Cu-O

bonds, oxygen vacancies, etc. in the back channel, which is the top of the  $Cu_2O$  film. These defects act as hole traps that impede hole transport within the channel [5]. Thus, the overall current level is decreased.

Secondly, after the passivation, as the TFTs are annealed in the air at 200°C, CuO layer is formed at the back channel. This formation of CuO layer causes off current to drop significantly. Furthermore, as the damage is cured by the thermal annealing, the overall switching property is improved by also increasing the on current slightly.

Fig. 3. The schematic illustration of the passivation effect on Cu<sub>2</sub>O TFTs.

## 3.2 Results of HCIO treated Cu<sub>2</sub>O TFT

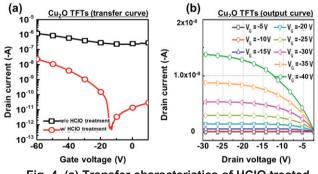

Next, we explore the effect of hypochlorous acid (HCIO) oxidation on Cu<sub>2</sub>O TFTs. Fig. 4 (a) shows the transfer characteristics of the HCIO treated solution-processed Cu<sub>2</sub>O TFTs. The Cu<sub>2</sub>O TFT without HCIO treatment that was annealed at  $500^{\circ}$ C showed poor switching property. However, for the HCIO treated Cu<sub>2</sub>O TFT, both the on and off currents decreased, where the off current dropped more significantly than the on current, thus improving the on-off current ratio from ~10<sup>1</sup> to ~10<sup>4</sup>. As for the output characteristics of HCIO treated Cu<sub>2</sub>O TFTs that is shown in Fig. 4 (b), the drain current is shown to saturate at all applied gate voltages.

Fig. 4. (a) Transfer characteristics of HCIO treated Cu<sub>2</sub>O TFTs. (b) Output characteristics of HCIO treated Cu<sub>2</sub>O TFT [3].

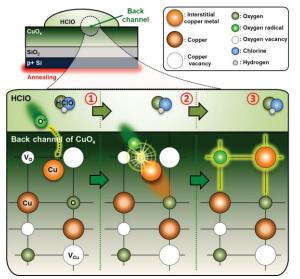

Fig. 5 illustrates the reaction between HCIO and Cu<sub>2</sub>O film. Within the Cu<sub>2</sub>O film, there are Cu vacancies that form when Cu enters the interstitial sites [6]. Therefore, when a strong oxidant such as HCIO is applied on Cu<sub>2</sub>O film, oxygen radicals that exist within HCIO are highly likely to react with the Cu that exist at interstitial sites. This reaction between Cu and O form metal-oxygen bond that fill in the vacancies that are point defects of Cu<sub>2</sub>O. Thus, both Cu vacancies and O vacancies decrease, and in turn, the switching property improves.

Fig. 5. Schematic for metal oxide formation and reduction of vacancies within Cu<sub>2</sub>O film during HCIO treatment [3].

## 3.3 Results of Ga doped Cu<sub>2</sub>O TFTs

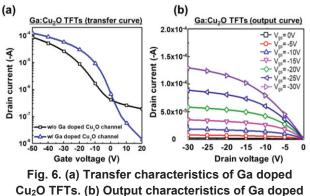

Finally, we engineered the channel layer by doping Ga inside Cu<sub>2</sub>O TFTs. Fig. 6 (a) shows the transfer characteristics of Ga doped Cu<sub>2</sub>O TFTs. As the graph shows, the non-doped Cu<sub>2</sub>O TFT shows its on-off current ratio to be  $\sim 10^2$ . However, when Ga was doped, the on-off current ratio improved to  $\sim 10^4$ . For the output characteristics of Ga doped Cu<sub>2</sub>O TFT shown in Fig. 6 (b), the drain current is saturated for all applied gate voltages.

Cu<sub>2</sub>O TFT.

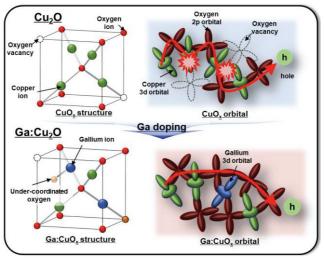

Fig. 7 shows illustration of carrier conduction property before and after Ga is doped in  $Cu_2O$  film. Before Ga is doped, the existing oxygen vacancies impede the flow of holes as they act as hole traps. Therefore, the electrical performance is poor. However, when Ga is doped, oxygen vacancies are filled as Ga bonds well with oxygen. Thus, the holes flow smoothly within the film. Hence, this improves the switching property of the  $Cu_2O$  TFTs by increasing the on-current.

Fig. 7. Schematic illustration for conduction of Cu<sub>2</sub>O before and after Ga doping.

## 4. CONCLUSION

In this paper, we investigated three method to improving switching characteristics of  $Cu_2O$  TFTs. From these researches,  $Cu_2O$  TFTs showed improved electrical characteristics compared with conventional  $Cu_2O$  TFTs. These approaches will allow p-type oxide TFTs to be adapted for CMOS application.

#### 5. ACKNOWLEDGEMENTS

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIT) (No. 2017R1A2B3008719).

## REFERENCES

- K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors", *Nature*, 432, 488, 2004.

- [2] H. A. Al-Jawhari, "A review of recent advances in transparent p-type Cu<sub>2</sub>O-based thin film transistors", *Materials Science in Semiconductor Processing*, 40, 241, 2015.

- [3] T. S. Jung, H. Lee, S. P. Park, H. J. Kim, J. H. Lee, D. Kim, and H. J. Kim, "Enhancement of Switching Characteristic for p-Type Oxide Semiconductors Using Hypochlorous Acid", ACS Applied Materials & Interfaces, 10, 32337, 2018.

- [4] W. Jie, S. Junfei, D. Chengyuan, Z. Zhongfei, C. Yuting, Z. Daxiang, H. Zhe, and Z. Runze, "Effect of active layer deposition temperature on the performance of sputtered amorphous In—Ga—Zn— O thin film transistors", *Journal of Semiconductors*, 35, 14003, 2014.

- [5] K. Matsuzaki, K. Nomura, H. Yanagi, T. Kamiya, M. Hirano, and H. Hosono, "Effects of post-annealing on (110) Cu<sub>2</sub>O epitaxial films and origin of low mobility in Cu<sub>2</sub>O thin-film transistor", *Pysica Status Solidi A-Application and Materials Science*, 206, 2192, 2009.