# Low-Temperature, Solution-Processed Inorganic p-Channel Cu-based Thin-Film Transistors and Circuits

# Ao Liu, Huihui Zhu, Yong-Young Noh

Department of Chemical Engineering, Pohang University of Science and Technology (POSTECH), Pohang, Gyeongbuk, 37673, Republic of Korea

Keywords: solution process, p-type semiconductors, low temperature, transistors

## ABSTRACT

Developing p-type transparent semiconductors has attracted great interest over the past decades to realize complementary p-n junction devices and circuits by cost effective graphic art processes. Here we report two kinds of transparent p-type Cu-based transistors (Cul and Cu<sub>x</sub>O), which can be synthesized using solution process at plastic-compatible temperatures.

#### **1** INTRODUCTION

Solution-processed p-type oxide semiconductors have recently attracted increasing interests for the applications in low-cost optoelectronic devices and circuits.[1] To date, only a few compounds, e.g., SnO, Cu<sub>x</sub>O, and NiO<sub>x</sub>, have been demonstrated and incorporated into transistors as the p-type channels. Among these, Cu<sub>x</sub>O is a promising candidate for p-type semiconductors due to its high Hall mobility, suitable optical properties, nontoxicity, and low costs. In initial studies, the deposition of Cu<sub>x</sub>O semiconducting layers relied on vacuum-based deposition techniques. Recently, alternative solution-based film deposition approaches, including spin/spray coating and inkjet printing, have been actively studied due to their simplicity, low cost, air processability, and scalability for large-area fabrication. Unfortunately, most of these studies employed high annealing temperatures (≥400 °C) or complex multi-step fabrication procedures, which typically lead to low repeatability and large lab-to-lab fluctuations in device performance. In the first part, a simple solution-phase polyol reduction method was used to fabricate Cu<sub>x</sub>O films as the active layer of transparent p-channel TFTs. The optimized Cu<sub>x</sub>O TFTs derived from propylene glycol at 220 °C exhibited stable operation with an average filed-effect hole mobility ( $\mu_{FE}$ ) of 0.15 cm<sup>2</sup> V<sup>-1</sup>  $s^{-1}$  and on/off current ratio ( $I_{on}/I_{off}$ ) of ~10<sup>4</sup>. The dry air and operational stability tests also showed reliable electrical characteristics.[2]

Recent theoretical studies have shown that anions with smaller electronegativity and larger p-orbitals than  $O^{2-}$  are more effective at realizing delocalized VBM than oxides. One promising inorganic p-type candidate is copper(I) iodide (CuI), which has high conductivity (238 S cm<sup>-1</sup>) as well as large  $E_g = 3.1$  eV. The naturally abundant and environment friendly constitutional elements of CuI make it more appropriate for large scale printed transparent

electronics. More importantly, CuI has much higher hole mobility (43.9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in bulk material compared with CuSCN and other p-type oxide semiconductors due to fairly small effective hole mass. In the second part, we report solution-processed p-type CuI TFTs processed at room temperature by controlling precursor concentration and CuI thickness. The optimized CuI TFTs with SiO<sub>2</sub> dielectric exhibited high hole mobility  $\mu_{FE} = 0.44 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  with  $I_{on}/I_{off} \approx 5 \times 10^2$ . Combining a high permittivity ZrO<sub>2</sub> dielectric layer increases  $\mu_{FE}$  to 1.93 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> with very low operating voltage (< 5 V). We demonstrate a complementary inverter with solution processed p-type CuI TFTs and n-type indium gallium zinc oxide (IGZO) TFTs.[3]

### 2 EXPERIMENT

Cu<sub>x</sub>O solution (0.1 M) was prepared in deionized water and propylene glycol mixtures (1:5 vol/vol). The precursor solution was spin-coated on SiO<sub>2</sub>/p<sup>+</sup>-Si substrates at 7000 rpm for 30 s. The gel films were first baked at 150 °C for 30 min and subsequently annealed at different temperatures in air for 30 min (ambient humidity < 20 %).

Cul precursor solutions were prepared by dissolving Cul powder into acetonitrile at concentrations 3, 5, 7, 10, and 25 mg ml<sup>-1</sup>. Precursor solution was filtered through a 0.2  $\mu$ m syringe filter and then spun on SiO<sub>2</sub>/Si substrates at 5000 rpm for 30 s in air. The 40-nm Au source and drain electrodes were deposited by thermal evaporation using a shadow mask.

#### 3 RESULTS and DISCUSSION

#### 3.1. Solution-processed Cu<sub>x</sub>O TFTs

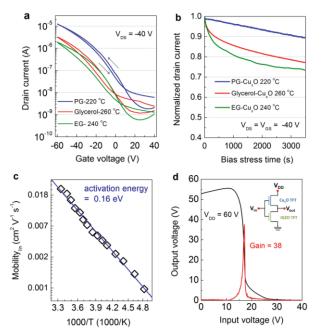

To investigate the electrical properties of the prepared  $Cu_xO$  thin films as channel layers in TFTs, bottom-gate top-contact (BG-TC) devices were fabricated on  $SiO_2/p^+$ -Si substrates and representative transfer curves are shown in Fig. 1a. 150 °C baking process enabled the formation of metallic Cu-dominated components. Gradually increasing the annealing temperature resulted in the phase transformation:  $Cu + Cu_2O + CuO \rightarrow Cu_2O + CuO \rightarrow CuO$ . The 150 °C-baked TFTs showed insulating behavior while typical p-channel characteristic were observed and enhanced upon increasing the temperature to 220 °C. The improved hole transport was

attributed to the decomposition of residual compounds and thermally-driven grain size augmentation. The latter is expected to reduce the number of grain boundaries, associated scattering, and possible deep traps. The optimized PG-derived devices were achieved at 220 °C with an improved  $\mu_{FE}$  of 0.15±0.02 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>,  $I_{on}/I_{off}$  of ~10<sup>4</sup>, and bias-stress stability, showing excellent reproducibility (Fig. 1b).

We further investigated their hole transport properties by analyzing temperature-dependent characteristics (Fig. 1c). The device mobility decreases linearly at lower temperatures, indicating that hole transport is thermally activated. This conduction mechanism likely occurred via defects and traps within grain boundaries or between the Cu<sub>x</sub>O/SiO<sub>2</sub> interface. The corresponding activation energy (E<sub>a</sub>), *i.e.*, the energy difference between the Fermi level and VB edge, was calculated to be 0.16 eV by fitting the plots using the equation,  $\mu_{FE} = \mu_0 \exp(-E_a/k_BT)$ , where  $k_B$  is the Boltzmann constant. The Ea was lower than the devices prepared using sputtering ( $E_a \approx 0.4 \text{ eV}$ ), which confirmed the superiority of PG-derived polyol reduction method for the fabrication of Cu<sub>x</sub>O TFTs. A key motivation for developing high-performance p-type oxide TFTs is to implement transparent CMOS circuits via integration with n-type oxide TFTs. The transparent CMOS inverters were then constructed by assembling CuxO and n-type InGaZnO TFTs. The inverter exhibited a sharp and clear signal inversion between the high and low states with negligible hysteresis (Fig. 1d). The voltage gain  $(dV_{out}/dV_{in})$  reaches 37 at supply voltage  $(V_{DD}) = 60$  V. To the best of our knowledge, this gain value is the highest reported to date for a solution-processed oxide TFT-based CMOS inverter.

Fig. 1 (a) Transfer characteristics of the optimized

$Cu_xO$  TFTs fabricated using different polyols at the indicated temperature. (b) Negative bias stress results of the optimized  $Cu_xO$  TFTs derived from different polyols. (c) Mobility variation for the PG  $Cu_xO$ -220 TFTs measured at different temperatures. (d) Voltage transfer characteristics and gain voltage of the CMOS inverter.

#### 3.2. RT Solution-processed Cul TFTs

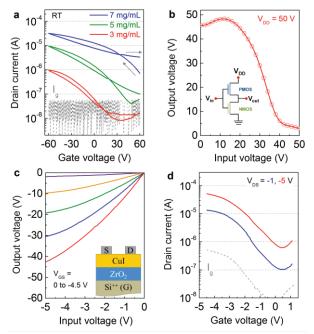

Figure 2a shows transfer curves for TFTs processed from different precursor concentrations (i.e., 7, 5, and 3 mg ml<sup>-1</sup>). When the Cul channel thickness reduces to  $\sim 8$ nm, apparent field effect modulation of channel currents  $(I_{\rm DS})$  under  $V_{\rm GS}$  was observed with  $I_{\rm on}/I_{\rm off} > 10^2$ . TFTs with 5 nm Cul channel layers exhibited the best electrical performance with average  $\mu_{FE} = 0.42 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ,  $I_{on}/I_{off} \approx$  $5 \times 10^2$ ,  $V_{\text{TH}} = 35$  V, and excellent reproducibility. Importantly, these promising electrical parameters were obtained at room temperature (RT) without requiring post-treatment processing. For solution processed p-type oxides, such as CuxO and NiO, relatively high annealing temperatures (≥ 250°C) are required to decompose residual impurities and achieve crystalline texture, which limits their applications on plastic substrates for flexible devices. For Cul, successful achievement of solution processed Cul TFTs at RT is very beneficial from the crystallization tendency of Cul and highly volatile acetonitrile solvent, leading to negligible impurity residues in the as-coated Cul channel layer.

To emphasize the developed Cul semiconductor superiority, we demonstrated a CMOS inverter by assembling p-type Cul and n-type InGaZnO TFTs. Figure 2b shows the voltage transfer characteristics of the complementary inverter at different  $V_{DD}$ . The CMOS inverter exhibited complete rail-to-rail voltage inversion between high and low states with voltage gain >4, which would be sufficient to drive next-stage components in a logic circuit. For the further performance improvement of RT Cul TFTs, we employed oxide dielectric with high permittivity (high  $\kappa$ ). We selected a promising high  $\kappa$ candidate, ZrO<sub>2</sub>, with  $\kappa$  = 25 and large bandgap  $\approx$  5.8 eV.[4] Gel films containing Zr were spin-coated onto heavily doped Si substrates, followed by UV irradiation under ambient conditions. UV induced photolysis and oxidation formed dense ZrO2 thin films at RT. The first solution processed TFTs with truly RT and Au/Cul/ZrO<sub>2</sub>/Si structure were fabricated and output and transfer plots are shown in Fig.2c and 2d. Benefiting from the large gate capacitance of ZrO<sub>2</sub> dielectric, the as-prepared transistors can be operated as low as 5 V, which is quite essential for applications in mobile and low power consumption devices. Cul/ZrO<sub>2</sub> TFT  $\mu_{FE}$  = 1.93 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. In addition, replacing SiO<sub>2</sub> with ZrO<sub>2</sub> caused negative threshold voltage ( $V_{TH}$ ) shift from 35 to -0.45 V,

indicating that device operation mode changed from depletion to enhancement. For logic circuit applications, enhancement mode transistors are preferable to depletion mode because no  $V_{GS}$  is required to switch the devices off, hence circuit design is simpler and lower power consumption. The negative  $V_{TH}$  shift implies that the ZrO<sub>2</sub> layer contains positive fixed charges, which can achieve negative threshold or turn-on voltage for p-channel TFTs.

Fig. 2 (a) Transfer characteristics for the RT-deposited Cul TFTs as a function of channel thickness. (b) Voltage transfer characteristics of complementary inverter based on p-type Cul and n-type InGaZnO TFTs (c, d) Output and transfer curves of solution-processed Cul/ZrO<sub>2</sub> TFTs.

#### 4 CONCLUSIONS

Herein, two kinds of solution-processed inorganic p-type Cu-based TFTs were reported. Firstly, the fabrication of low-temperature solution-processed CuxO TFTs using eco-friendly polyol reduction method was reported. The selection of appropriate polyalcohol, optimal channel thickness, and annealing temperature were critical for achieving good transistor performance with high operational stability. The optimized Cu<sub>x</sub>O TFTs derived from propylene glycol at 220 °C exhibited stable operation with an average  $\mu_{FE}$  of 0.15 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>,  $I_{on}/I_{off}$  of ~10<sup>4</sup>, and excellent reproducibility. This work aims to provide a comprehensive investigation on the electrical properties of solution-deposited Cu<sub>x</sub>O TFTs. The optimized polyol reduction method proposed here is simple and reliable, enabling fabrication at plastic-compatible device temperatures.

In the second part, we successfully demonstrated RT solution processed p-type Cul TFTs with electrical

performances strongly related to channel thickness and annealing conditions. Optimizing the precursor formulation, and CuI and gate dielectric thicknesses, produced p-type CuI/ZrO<sub>2</sub> TFTs with a  $\mu_{FE}$  = 1.93 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at low operating voltage = 5 V. We believe that this work opens the floodgate for room temperature, low cost, high performance inorganic p-type transistors for diverse opto/electronic devices.

#### 5 ACKNOWLEDGEMENTS

This study was supported by the Center for Advanced Soft-Electronics (Grant 2013M3A6A5073183), Ministry of Science & ICT through the NRF grant funded by the Korea government (2017R1E1A1A01075360), and the 2018 Government-funded Research Program of the Korea Institute of Machinery and Materials (Grant NK210D).

#### REFERENCES

- Ao Liu, Huihui Zhu, Yong-Young Noh, "Solution-Processed Inorganic P-Channel Transistors: Recent Advances and Perspectives" *Mat. Sci. Eng. R,* Vol. 135, pp. 85-100 (2019).

- Ao Liu, Huihui Zhu, Yong-Young Noh, "Polyol [2] Reduction: A Low-Temperature Eco-Friendly Solution Process Copper for p-Channel Oxide-Based Transistors and Inverter Circuits" ACS DOI: Appl. Mater. Interfaces, 10.1021/acsami.9b11161 (2019).

- [3] Ao Liu, Huihui Zhu, Won-Tae Park, Seok-Ju Kang, Yong Xu, Myung-Gil Kim, Yong-Young Noh, "Room-Temperature Solution-Synthesized p-Type Copper(I) lodide Semiconductors for Transparent Thin-Film Transistors and Complementary Electronics" *Adv. Mater.*, Vol. 30, pp. 1802379 (2018).

- [4] Ao Liu, Huihui Zhu, Huabin Sun, Yong Xu, Yong-Young Noh, "Solution Processed Metal Oxide High-k Dielectrics for Emerging Transistors and Circuits" Adv. Mater., Vol. 30, pp. 1706364 (2018).