## β-Ga<sub>2</sub>O<sub>3</sub> 電子構造の UPS 評価に基づく MOS 界面固定電荷密度の正確な抽出 Accurate estimation of MOS interface fixed charge density based on UPS analysis of electric structure of β-Ga<sub>2</sub>O<sub>3</sub>

## 東京大学工学部マテリアル工学科 ○武田大樹, 喜多 浩之

Dept. of Materials Engineering, The Univ. of Tokyo, °Daiki Takeda and Koji Kita E-mail: takeda@scio.t.u-tokyo.ac.jp

【はじめに】我々は既に  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (001)エピタキシャル基板上で SiO<sub>2</sub> をゲート絶縁膜として  $D_{it}$  が <10<sup>11</sup> cm<sup>-2</sup> となる MOS 界面の形成を報告しているが[1],  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> の電子構造についての知見が不足により正確なフェルミレベルが分からないために,より深い準位への電荷捕獲の有無の重要な目安となる界面固定電荷密度については正しい推定ができていなかった。フェルミレベルは,電子親和力やイオン化エネルギーの大きさが定まらないままでは正確に知ることができない。そこで本研究では,MOS 構造の形成に使用する  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (001)エピタキシャル基板上で UPS 測定を行ってイオン化エネルギーを正確に求めることによりフェルミレベルを精度よく推定した上で,これに基づいて MOS キャパシタのフラットバンド電圧( $V_{fb}$ )の理想値を定めることにより,界面固定電荷密度を抽出することを試みた。

【実験方法】n 型エピタキシャル膜を有する  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (001)ウェハを希釈 HF 中で洗浄し、UPS 測定を行った。線源には He I線(hv=21.22eV)を用いた。SiO<sub>2</sub> ゲート絶縁膜を $\sim$ 10<sup>-2</sup> Pa の O<sub>2</sub> 雰囲気中での Si の電子線蒸着によって 35nm の膜厚で形成後,O<sub>2</sub> 雰囲気中 1000°Cのアニールを行い,最後に Au 電極を蒸着して MOS キャパシタを作製し、C-V 測定を行った。

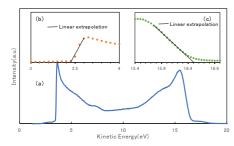

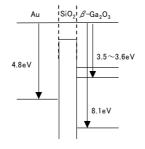

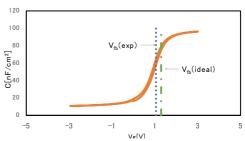

【結果および考察】 Fig. 1(a)に測定された UPS を示す。スペクトルの価電子帯端(Fig. 1(c))とカットオフエネルギー(Fig. 1(b))の差分を線源のエネルギーから引く(hv –( $E_{valence}$  –  $E_{cutoff}$ ))ことによってイオン化エネルギーは 8.2 eV と推定された。そこで  $\beta$ -Ga $_2$ O $_3$  のバンドギャップ  $E_g$  を 4.7~4.8eV[2]とし,さらに伝導帯端の有効状態密度を,電子の有効質量を 0.28  $m_0$ [3]として概算すればフェルミレベルは伝導帯から約 0.1 eV 深い位置にあるので,これらのことを考慮すると  $\beta$ -Ga $_2$ O $_3$ (001)のフェルミレベルは真空準位から 3.5~3.6 eV にあると推定された。これは同じく光電子測定を用いた  $\beta$ -Ga $_2$ O $_3$ (100)に対する既報[4]よりも 0.4~0.5eV も小さい値であることに注意されたい。この結果をもとに,MOS キャパシタの理想的なバンドアライメントを Fig. 2 に示す。作製した MOS キャパシタの C-V 特性は,周波数分散やヒステリシスが小さいものであった。Fig. 3 に 1MHz での C-V 曲線と共に,そこから得られた  $V_{fb}$ (exp)と,UPS で推定されたフェルミレベルから求めた理想的な  $V_{fb}$  ( $V_{fb}$ (ideal))を示す。尚, $V_{fb}$ (ideal)の推定において Au 電極の仕事関数は同じく UPS にて決定した 4.8 eV を用い,キャリア濃度は C-V 曲線における最大空乏状態での静電容量から推定される値(6×10<sup>15</sup>cm $^3$ )を用いた。観察された  $V_{fb}$ シフトはおよそ 0.3 eV 程度であり,SiO $_2$  膜厚を考慮して,界面の正の固定電荷密度は<1.5×10<sup>11</sup> cm $^2$  に抑制されていることが分かった

以上のように、本研究では UPS 測定によって  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (001)表面の電子構造を評価することで正確に推定したフェルミレベルを用いることにより、SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (001) MOS キャパシタの界面固定電荷が正しく推定された。その結果、本研究のプロセスで形成した MOS 界面は  $D_{it}$  が抑制されているだけなく、深い準位も抑制されて固定電荷密度が低いことを示すことができた。尚、本研究の一部は、JST 低炭素社会戦略センター(LCS)との共同研究により実施された。

参考文献 [1]Q.Mao ら第 67 回春季応物学会.14p-B401-14 (2020). [2] S.J.Pearton et al., Appl.Phys.Reviwes 5,011301(2018). [3] K. Irmscher et al., J.Appl.Phys. 110, 063720(2011). [4] M. Mohamed et al., Appl.Phys.Lett.101,132106(2012).

Fig.1 (a) UPS spectrum of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> using He I line (2.122eV) as UV light source. Magnified spectrum is shown for (b) near cut-off energy, and (c) near valence band edge.

Fig.2 Estimated band alignment of Au/SiO<sub>2</sub>/β-Ga<sub>2</sub>O<sub>3</sub> MOS capacitor estimated from the results of UPS.

Fig.3 1MHz bidirectional C-V characteristics of Au/SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOS capacitor. The observed V<sub>fb</sub> (V<sub>fb</sub>(exp)) and the calculated ideal V<sub>fb</sub> (V<sub>fb</sub>(ideal)) are indicated by dotted lines.