## p-ドリフト層を持つ縦型 2DHG ダイヤモンド MOSFET の高絶縁破壊電圧(>580 V)の達成

Achievement of High Breakdown Voltage (>580 V) in Vertical-Type 2DHG Diamond MOSFET by p-drift layer

早大理工1,早大材研2

°(B)太田 康介¹, 角田 隼¹, 新倉 直弥¹, 森下 葵¹, 平岩 篤¹, 川原田 洋¹,² Waseda Univ.<sup>1</sup>, Kagami Memorial Research Institute for Materials Science and Technology.<sup>2</sup> °(B)Kosuke Ota<sup>1</sup>, Jun Tsunoda<sup>1</sup>, Naoya Niikura<sup>1</sup>, Aoi Morishita<sup>1</sup>, Atsushi Hiraiwa<sup>1</sup>, Hiroshi Kawarada<sup>1,2</sup>

E-mail: ok0723@suou.waseda.jp

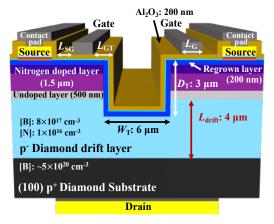

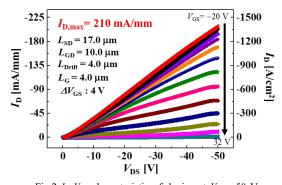

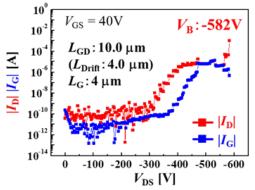

高出力·高速スイッチング相補型インバータの実現 に向けてn型に対応する集積化に適した縦型pチャ ネルパワーFET の開発が急務である。我々は C-H 終 端構造及び高温 ALD-Al<sub>2</sub>O<sub>3</sub><sup>[1]</sup>により面方位に依存せ ず誘起される 2 次元正孔ガス(2DHG)を用いた縦型 2DHG ダイヤモンド MOSFET を報告<sup>[1]-[3]</sup>し、高い ドレイン電流密度(> 20 kA/cm<sup>2 [4]</sup>, 710 mA/mm<sup>[3]</sup>)と 縦型 n-FETs の SiC や GaN に匹敵するオン抵抗(2.5  $m\Omega \cdot cm^2)^{[4]}$ を実現してきた。本研究では、p-ドリフト 層を備えた(100)縦型 2DHG ダイヤモンド MOSFET を初めて作製し、現在報告されている縦型ダイヤモ ンド MOSFET の中で最大の絶縁破壊電圧( $V_{\rm B}$ : -582 V)を達成したため報告する。Fig.1 に作製した縦型 デバイスの断面図を示す。p-ドリフト層([B]: ~8× $10^{17}$  cm<sup>-3</sup>, [N]: ~1× $10^{16}$  cm<sup>-3</sup>)は、MPCVD 法を用 いて計 4 μm 成膜した。本デバイス寸法として、ソ ース・ゲート間( $L_{SG}$ )は 3  $\mu$ m、ゲート・トレンチ間( $L_{GT}$ ) は  $4 \mu m$ 、ゲート・ドレイン間距離( $L_{GD}$ )は  $10 \mu m$ 、ソ ース・ドレイン間( $L_{SD}$ )は  $17 \mu m$ 、ゲート長( $L_G$ )は  $4 \mu m$ となった。またデバイスアクティブ領域はソース・ ソース間距離( $L_{SS}$ : 30  $\mu$ m)とゲート幅( $W_G$ : 25  $\mu$ m)の 積で定義し、 $7.5 \times 10^{-6}$  cm<sup>-2</sup> となった。Fig. 2 の  $I_D$ - $V_{DS}$ 特性より  $V_{DS}$ : -50 V、 $V_{GS}$ : -20 V にてゲート幅で規格 化した最大ドレイン電流密度(I<sub>D,max</sub>)は 210 mA/mm となり、アクティブ領域規格では  $I_{D,max}$ : 1400 A/cm<sup>2</sup> 及びオン抵抗は  $R_{\text{on}}$ : 23 m $\Omega$ ·cm<sup>2</sup> となった。本研究で 得られたドレイン電流密度は p-ドリフト層を持た ないドリフト層のない平面で同寸法の縦型デバイ スと同等の値である<sup>[1]</sup>。また、Fig.3 に示す通り、高 い絶縁破壊電圧(VB: -582 V)を達成し、平均電界強度 は 0.6 MV/cm を確認した。この値は p-ドリフト層を 持たない同寸法デバイスの絶縁破壊電圧(VB: -359 V)<sup>[1]</sup>よりも遥かに高く、現在報告されている縦型ダ イヤモンド FET で最大の値となる。今後、p<sup>-</sup>ドリフ ト層の窒素濃度及びボロン濃度を最適化し、ドリフ ト層を 10 μm 程度増やすことで、更なる絶縁破壊特 性の向上が可能である。また、本デバイス構造にト レンチゲート構造[4]を導入し、低オン抵抗化を実現 させることで、高耐圧かつ低オン抵抗なp型パワー トレンチダイヤモンド MOSFET が実現可能となる。

[謝辞]本研究は、文部科学省ナノテクノロジープラッ トフォーム事業(NIMS 微細加工プラットフォーム)の 支援を得た。

[1] N. Oi, H Kawarada et al., *Sci. Rep.*, vol. 8, Art. No. 10660. (2018) [2] M. Iwataki, H. Kawarada et al., *IEEE.EDL*, 41, p111-114. (2019) [3] J. Tsunoda, H. Kawarada et al., *Carbon*, in press. (2021) [4] J. Tsunoda, H. Kawarada et al., *IEEE EDL*, submitted. (2020)

Fig.1 Schematic cross-sectional view of a (100) verticaltype 2DHG diamond MOSFET with p-diamond drift layer.

Fig.2  $I_D$ - $V_{DS}$  characteristic of device at  $V_{DS}$ : -50 V and  $V_{\rm GS}$  is varied from -20 V 32 V in steps of 4V.

Fig.3 Breakdown characteristics of device.