## Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> 界面ダイポール層形成による 4H-SiC MOS キャパシタの正方向 V<sub>FB</sub> シフト Positive V<sub>FB</sub> shift of 4H-SiC MOS capacitors induced by Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> interface dipole layer formation

## <sup>1</sup>Dept. of Materials Engineering, The Univ. of Tokyo, <sup>2</sup> Advanced Technology R&D Center, Mitsubishi Electric Corporation <sup>o</sup>Tae-Hyeon Kil<sup>1</sup>, Munetaka Noguchi<sup>2</sup>, Hiroshi Watanabe<sup>2</sup>, and Koji Kita<sup>1</sup> E-mail: thkil@scio.t.u-tokyo.ac.jp

**[Introduction]** Generally, threshold voltage (V<sub>th</sub>) of SiC-MOSFET is tuned by the channel doping concentration, however, an intentional increase in the doping concentration to achieve a sufficiently large V<sub>th</sub> can cause a significant deterioration of channel conductance [1]. Introduction of negative fixed charges at SiO<sub>2</sub>/4H–SiC interface may also contribute to the positive shift of V<sub>th</sub>, but this might have some influence on its reliability. Therefore, additional novel processes are demanded for the increase of V<sub>th</sub> while maintaining the oxide-semiconductor interface quality or channel mobility of MOSFETs. In this work, we demonstrated the formation of an additional dipole layer on top of SiO<sub>2</sub> for the control of flat-band voltage (V<sub>FB</sub>) of SiO<sub>2</sub>/4H-SiC MOS capacitors. We have already clarified the dipole layer formation at SiO<sub>2</sub>/SiC interface by interface nitridation [2], but in this work we are going to manipulate the dipoles formed in the gate dielectric layer by using Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> interface [3].

**[Experiments]** N-type 4H-SiC 4°-off (0001) Si-face wafers with epitaxial layers (N<sub>D</sub> ~  $1.0 \times 10^{16}$  cm<sup>-3</sup>) were used as the substrates. After cleaning and HF etching, samples were thermally oxidized at 1300°C to grow SiO<sub>2</sub> layers in oxygen ambient. After oxidation, NO-POA processes at 1150°C in the ambient of NO:N<sub>2</sub>=1:2 were performed. After a slight sacrificial etching of the surface of SiO<sub>2</sub> with 0.1% HF (<1 nm), Al<sub>2</sub>O<sub>3</sub> thin film was sputtered on top of SiO<sub>2</sub> using Al<sub>2</sub>O<sub>3</sub> ceramic target. After Al<sub>2</sub>O<sub>3</sub> deposition, post-deposition annealing (PDA) was conducted at 800°C in 0.1% O<sub>2</sub> + N<sub>2</sub> ambient. Au and Al were used as top and bottom electrodes, respectively. From C-V measurements, the V<sub>FB</sub> of each MOS capacitor was estimated. After C-V measurements, D<sub>it</sub> was estimated by using the conductance method. Al<sub>2</sub>O<sub>3</sub> thickness was determined by X-ray reflectivity.

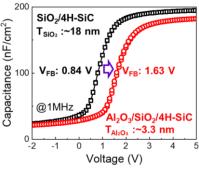

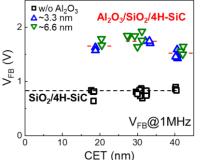

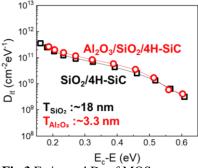

**[Results & Discussions] Figure 1** shows the bidirectional C-V curves measured at 1 MHz before and after ~3.3 nm-thick Al<sub>2</sub>O<sub>3</sub> sputtering. V<sub>FB</sub> for all the samples were reasonably extracted since they show nearly ideal curves with small frequency dispersions. **Figure 2** shows the comparison of the V<sub>FB</sub> as a function of capacitance equivalent thickness (CET) between SiO<sub>2</sub>/SiC (black) and Al<sub>2</sub>O<sub>3</sub>(~3.3 or ~6.6 nm)/SiO<sub>2</sub>/SiC (colored) systems. The thickness of SiO<sub>2</sub> was around ~17 or ~32, or ~40 nm, respectively. Due to the small variation of SiO<sub>2</sub> thickness after thermal oxidation even though the samples oxidized at the same condition, there was some total thickness variation. First, for SiO<sub>2</sub>/SiC (black points and line), the line was almost flat, which indicates low fixed charges at the SiO<sub>2</sub>/SiC interface after nitridation. Next, for Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/SiC (colored) samples, we can observe the increased V<sub>FB</sub> (0.6~0.8 V), induced by the dipole layer at the Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> interface [3]. With the increase of Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> interface. In order to clarify that Al<sub>2</sub>O<sub>3</sub> fabrication processes had no impact on the SiO<sub>2</sub>/4H-SiC interface, we estimated the interface state density (D<sub>it</sub>) before and after Al<sub>2</sub>O<sub>3</sub> deposition. **Figure 3** shows the D<sub>it</sub> for the MOS capacitors with and without the Al<sub>2</sub>O<sub>3</sub> fabrication processes. From these results, positive V<sub>FB</sub> shift can be achieved only by the introduction of a few nanometer Al<sub>2</sub>O<sub>3</sub> on top, while maintaining the MOS interface quality.

**[Conclusions]** To achieve higher  $V_{FB}$ , we deposited very thin Al<sub>2</sub>O<sub>3</sub> layers on top of thermally oxidized SiO<sub>2</sub>. Thanks to the interface dipole layer effects at Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>, we successfully fabricated Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/4H-SiC MOS capacitors with higher V<sub>FB</sub> than SiO<sub>2</sub>/4H-SiC MOS capacitors (~0.8 V), while maintaining the SiO<sub>2</sub>/SiC interface quality. Considering that multilayer stack (Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>...) is expected to increase V<sub>FB</sub> further, which has been already demonstrated on Si MOS capacitor [3], this technique can be a great option for the nitrided SiC devices against the unwanted negative shift of V<sub>FB</sub> which is often introduced by typical nitridation processes [4].

**References** [1] M. Noguchi et al., IEDM Tech. Digest p.185 (2018). [2] T. H. Kil and K. Kita, Appl. Phys. Lett. 116, 122103 (2020). [3] H. Kamata and K. Kita, Appl. Phys. Lett. 110, 102106 (2017). [4] G. Chung et al., Appl. Surf. Sci. 184, 399 (2001).

**Fig.1** 1MHz Bidirectional C-V curves of SiO<sub>2</sub>/SiC MOS capacitors with and without Al<sub>2</sub>O<sub>3</sub> thin film.

**Fig.2** V<sub>FB</sub>-CET plots of SiO<sub>2</sub>/SiC MOS capacitors with and without Al<sub>2</sub>O<sub>3</sub> thin film.

**Fig.3** Estimated D<sub>it</sub> of MOS capacitors with and without Al<sub>2</sub>O<sub>3</sub> thin film by conductance method.