## パルス駆動型超伝導マトリクスメモリにおけるセル選択に関する研究

Study on cell selection in a pulse-driven superconductor matrix memory

名大院工,<sup>○</sup>加藤 健人, 竹下 雄登, 東 正志, 長谷川 大輝, 藤澤 日向 李峰, 田中 雅光, 山下 太郎, 藤巻 朗

Nagoya Univ., °Kento Kato, Yuto Takeshita, Masayuki Higashi, Daiki Hasegawa, Hinata Fujisawa Feng Li, Masamitsu Tanaka, Taro Yamashita, and Akira Fujimaki

E-mail: k.kato@super.nuee.nagoya-u.ac.jp

単一磁束量子回路(SFQ)回路は、数十 GHz という高速性を特徴としており、高性能計算機などへの応用が期待されている。実用化への課題の一つが、メモリ階層上、レジスタと大容量メモリの中間に位置する高速中容量メモリの不在である。これまでに提案されてきたメモリは、充放電の時定数による動作速度の制限から、目標とする動作速度の実現は困難であった。その解決策として我々は、 $\pi$ 位相シフト磁性ジョセフソン接合(磁性  $\pi$  接合[1])を導入した、長距離配線の充放電を必要としないパルス駆動型の超伝導マトリクスメモリを提案している[2]。

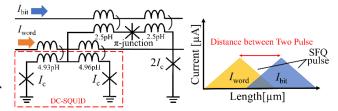

提案しているパルス駆動型メモリは、図 1 の 構成をとる。まずパルス電流 Iword をワード線に 流し DC-SQUID に磁場を印加、その臨界電流値 を下げる。これにより、π接合を含むループ(記 憶セル)に半磁束量子が入りエネルギー障壁を下 げる。この状況でパルス電流 Ibit をビット線に流 すことで、記憶セルの内部状態の書き換えが出来 る。このメモリでは、ワード線とビット線の電流 の交点の記憶セルが選択され、そこで書き込みが 行われる。しかしながら、選択には SFQ パルス が用いられるため、完全にタイミングが一致する 条件に対して、どの程度の時間差が許されるか、 言い換えれば、コインシデンスを確保できる長さ について考える必要がある。この長さは、リピー タを用いずに駆動できるメモリアレイの一辺の 長さに相当し、最低でも8セル分の確保が当面の 目標となる。

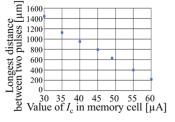

そこで本研究では、コインシデンスを確保できる長さが、メモリセルのパラメータを変化させることでどのように変化するかをシミュレーションにより調べた。今回のシミュレーション上では、意図的に片方の SFQ パルスを遅延させ、どの程度のパルス間の距離までメモリセルが正常に動作するかを調査し、SFQ パルスの伝搬速度に基づきコインシデンスを確保できる長さを調査した(図 2)。

図 3 にシミュレーション結果を示す。メモリセルの 0 接合の臨界電流値  $I_c$ を小さくするほど、より長い距離でコインシデンスを確保できていることがわかる。

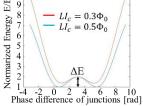

この結果を考察するにあたり、0 接合と $\pi$  接合を含んだ超伝導ループである  $0-\pi$  SQUID のポテンシャルエネルギーを考える。

0-π SQUID のポテンシャルエネルギーは

$$\frac{E}{EJ} = (1-\cos\theta_0) + (1+\cos\theta_\pi) + \frac{\Phi_0}{4\pi L I_c} (\theta_0-\theta_\pi)^2$$

と表され、図4のようなグラフを示す。ここで

$$E_J = \frac{\Phi_0 I_c}{2\pi}$$

,  $\theta_0$ : 0 接合の位相差,  $\theta_\pi$ :  $\pi$  接合の位相差

である。図4からわかるように、二状態間の遷移に必要なエネルギー $\Delta E$ は、メモリセルを構成する超伝導ループ全体のインダクタンス L と、0 接合の臨界電流値  $I_c$  の積である  $LI_c$  積の大きさに依存することが分かる。従って、今回のシミュレーションでは、 $I_c$  が小さくなることで、 $\Delta E$  が小さくなり、より長い距離でコインシデンスを確保は、十分に S セル相当より長く、大容量化の可能性を示した。ただし、ここでは、パルスのジッタ等の考慮を含めておらず、実際のメモリの設計に向け、さらに検討を進める。

講演では、各種シミュレーションの結果について議論する。

<u>謝辞</u> 本研究は、特別推進研究(18H05211)及び 基盤研究(S)(JP19H05615)の支援を受けて実施し たものである。

## 参考文献

[1] V. V. Ryazanov *et al.*, Phys. Rev. Lett., vol. 86, pp. 2427-2430, 2001.

[2] Y.takeshita *et al.*, "Study on pulse-driven, high-speed memory based on  $0-\pi$  SQUIDs with passive transmission lines", Wk1EOr2B-02, ASC2020.

Fig. 1. Schematic diagram of the memory cell

Fig. 2. Definition of the distance ensuring coincidence

Fig. 3. Simulation result of the distance for different critical currents for 0-junctions

Fig. 4. Potential Energy of 0-π SQUID