## 塗布型有機単結晶膜の転写パターニングによる高性能 CMOS 論理回路開発

Transfer Patterning of Solution-processed Organic Single Crystals and High-performance CMOS Logic Circuits

東大院新領域 <sup>1</sup>, OPERANDO-OIL<sup>2</sup>, 物材機構 <sup>3</sup>, JST さきがけ <sup>4</sup> <sup>○</sup>牧田 龍幸 <sup>1,2</sup>, 臼井 大登 <sup>1</sup>, 二宮 陽真 <sup>1</sup>, 熊谷 翔平 <sup>1</sup>, 辻村 秀太 <sup>1</sup>, 山下 侑 <sup>1,3</sup>, 岡本 敏宏 <sup>1,2,4</sup>, 佐々木 真理 <sup>1</sup>, 渡邉 峻一郎 <sup>1,2</sup>, 竹谷 純一 <sup>1,2,3</sup>

Univ. of Tokyo<sup>1</sup>, OPERANDO-OIL<sup>2</sup>, NIMS<sup>3</sup>, JST-PRESTO<sup>4</sup>, °Tatsuyuki Makita<sup>1,2</sup>, Hiroto Usui<sup>1</sup>, Yoma Ninomiya<sup>1</sup>, Shohei Kumagai<sup>1</sup>, Shuta Tsujimura<sup>1</sup>, Yu Yamashita<sup>1,3</sup>, Toshihiro Okamoto<sup>1,2,4</sup>, Mari Sasaki<sup>1</sup>, Shun Watanabe<sup>1,2</sup>, Jun Takeya<sup>1,2,3</sup>

E-mail: 7071193578@edu.k.u-tokyo.ac.jp

有機半導体は塗布法による低コストでの薄膜作製が可能であることから、次世代電子デバイスの基盤材料として期待され、盛んに研究されている。近年では、材料開発と製膜技術の向上によって、 $10~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$ を超える高移動度を示す半導体単結晶薄膜を約  $10~{\rm cm}$  角の大きさで得られるようになっている[1]。このような半導体膜を論理回路に応用する際には、各素子を電気的に孤立させるためのパターニングが必須である。本研究では、近年当研究室で開発された塗布型半導体薄膜の転写法を応用し[2]、Polydimethylsiloxane(PDMS)で作製した凹凸形状のあるスタンプを用いた簡便なパターニングプロセスを開発して CMOS 論理回路の作製を行った。

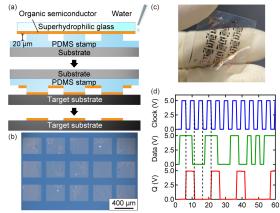

転写パターニング法の模式図を Fig. 1(a)に示す。超親水性基板上に塗布した半導体単結晶膜を、 20  $\mu$ m 程度の段差がある PDMS スタンプ上に設置して水を滴下することで半導体膜を転写した。 これをターゲット基板上に押し付けることで、Fig. 1(b)のようにスタンプ凸部上の半導体膜のみが 転写され、パターニングが完了した。 p 型半導体として  $C_9$ –DNBDT–NW、n 型半導体として  $PhC_2$ –PONBDT–PNW0 に  $PhC_2$ –PNW0 に PNDT0 に PNDT0

作製を行った(Fig. 1(c))。Fig. 1(d)の入出力特性から、ネガティブエッジトリガ型の D-flip-flop (DFF) の駆動が確認できた。以上により、本手法は高性能な塗布型単結晶膜を用いた CMOS 論理回路作製に有用であることが明らかとなった。

- [1] S. Kumagai et al., Sci. Rep. 9, 15897 (2019).

- [2] T. Makita et al., PNAS 117, 80 (2020).

- [3] T. Okamoto *et al.*, *Sci. Adv.* **6**, eaaz0632 (2020). 【謝辞】

この成果の一部は、国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)の委託業務の結果得られたものです。

Fig. 1 (a) Schematic illustration of the transfer patterning process. (b) Cross-polarized optical microscopy image of the patterned C<sub>9</sub>–DNBDT–NW thin films. (c) Device picture. (d) Input (Clock and Data) and output (Q) signals of the fabricated DFF.