# Top-gate monolayer MoS<sub>2</sub> MOSFETs with ZrO<sub>2</sub> gate dielectrics formed by low temperature ALD

AIST<sup>1</sup>, TMU<sup>2</sup> °W. H. Chang<sup>1</sup>, N. Okada<sup>1</sup>, M. Horikawa<sup>1</sup>, T. Endo<sup>2</sup>, Y. Miyata<sup>2</sup>, T. Irisawa<sup>1</sup>

## E-mail: wh-chang@aist.go.jp

## 1. Introduction

3. Results and discussion

$MoS_2$ , a well-known TMDC channel material shows great potential in low-power-consumption device field. To fulfill the requirement of very-large-scaleintegration (VLSI) applications, fabricating high performance top gate  $MoS_2$  MOSFETs using chemical vapor deposition (CVD) grown  $MoS_2$  with high quality gate dielectric is indispensable. Recently, we have reported uniform deposition of ZrO<sub>2</sub> on CVD-grown  $MoS_2$  by plasma enhanced ALD (PEALD) [1]. Although high oxidation efficiency of PEALD promotes uniform layer deposition, the degradation of interfacial quality owing to  $MoS_2$  oxidation was addressed.

In this study, uniform deposition of  $ZrO_2$  as gate dielectrics on CVD-grown  $MoS_2$  were obtained through ALD even at low deposition temperature at 150 °C, leading to significantly suppressed interfacial oxidation [2]. The device performance of top gate monolayer (1L)  $MoS_2$  MOSFETs has also been demonstrated.

### 2. Experimental procedure

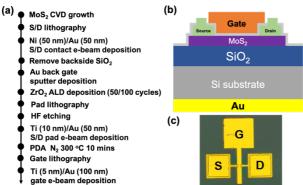

The detailed process flow for fabricating 1L MoS<sub>2</sub> top gate MOSFETs is shown Fig 1(a). The schematic cross-section and top view of optical microscope photograph of MoS<sub>2</sub> devices are shown in Fig. 1(b) and 1(c), respectively. Salt-assisted CVD was used to synthesize MoS<sub>2</sub> directly on SiO<sub>2</sub>/Si substrates using MoO<sub>2</sub> and sulfur powder. KBr was used as a growth promoter, as described previously [3]. ZrO<sub>2</sub> gate dielectrics were deposited at 150 °C thorough ALD using TEMAZ and H<sub>2</sub>O as precursors, which denotes as LT-ALD afterwards. MoS<sub>2</sub> samples deposited with PEALD ZrO<sub>2</sub> gate dielectrics at 300 °C [1] were also prepared for comparison, which denotes as HT-PEALD afterwards.

Fig. 1 (a) Process flow for fabricating  $MoS_2$  top gate MOSFETs, (b) schematic cross-section and (c) top view of optical microscope photograph of the fabricated devices.

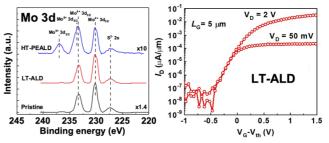

Fig. 2 shows Mo 3d XPS spectra extracted from 2 nm thick ZrO<sub>2</sub> on bulk MoS<sub>2</sub>, which was mechanically exfoliated from MoS<sub>2</sub> flakes. The spectrum extracted from pristine MoS<sub>2</sub> flakes is also shown for comparison. The Mo 3d spectra for pristine and LT-ALD samples show almost identical features with three distinct peaks, which are attributed to the MoS<sub>2</sub> states. This indicates that the ZrO<sub>2</sub> deposition on MoS<sub>2</sub> at 150 °C mainly results from physical absorption instead of chemical reaction between ZrO<sub>2</sub> and MoS<sub>2</sub>. On the other hand, additional states corresponding to MoO3 were observed in HT-PEALD samples, suggesting the formation of Mo oxide interfacial layer owing to high oxidation efficiency of HT PEALD. Fig. 3 shows the  $I_D$ - $V_G$ characteristics of 5µm-gate-length 1L MoS<sub>2</sub> MOSFETs under top gate operation. Normal nMOSFETs operation behavior was clearly observed with a high on-off ratio of  $10^7$ . Low subthreshold swing of ~90 mV/decade also indicates the benefit of suppressed interfacial oxidation, which leads to low damaged MoS<sub>2</sub> channel.

Fig. 2 Mo 3d XPS spectra Fig. 3  $I_D$ - $V_G$  characteristics extracted from HT- of 5 $\mu$ m-gate-length 1L PEALD ZrO<sub>2</sub>/MoS<sub>2</sub>, LT- MoS<sub>2</sub> MOSFETs under top ALD ZrO<sub>2</sub>/MoS<sub>2</sub> and pristine MoS<sub>2</sub>, respectively

## 4. Conclusion

1L MoS<sub>2</sub> top gate MOSFETs using ALD  $ZrO_2$  gate dielectrics has been demonstrated with VLSIcompatible gate stack formation processes. Low ALD deposition temperature promotes physical adsorption, leading to significantly suppressed surface oxidation and less damaged MoS<sub>2</sub> channel. low thermal budget process is beneficial for ultrathin MoS<sub>2</sub> channel.

#### Acknowledgment

This work is supported by JST CREST, Grant Numbers JPMJCR16F3, Japan.

## Reference

[1] W. H. Chang et al., *Silicon nano workshop* 91 (2019). [2] W. H. Chang et al., *JJAP* in press. [3] K. Kojima et al., *Nanoscale* 11, 12798 (2019).