# **On-Wafer Recorders for Assessing Wide Range Plasma Induced Charging Effect in FinFET Processes**

Chi Su, Yi-Jie Chao, Chrong-Jung Lin, and Ya-Chin King Microelectronics Laboratory, Institute of Electronics Engineering, National Tsing Hua University, Hsinchu, Taiwan Phone/Fax: +886-3-5162219, E-mail: <u>ycking@ce.nthu.edu.tw</u>

# Abstract

Newly proposed on-wafer test patterns for assessing widerange plasma induced charging levels in advanced FinFET logic processes have been demonstrated. By sizing up the capacitor linked to the antenna node, the maximum sensing level can be extended successfully.

## Introduction

In recent years, the continuous evolution of semiconductor process technology pushes key circuit elements to scale down aggressively. Advanced CMOS FinFET processes include many more plasma-etching steps, enabling the formation of high aspect ratio structures [1]. Meanwhile, as the intensity of plasma and the number of processing steps with plasma raise, plasma induced damage becomes more serious in FinFET circuits.

Design rules which restrict the size of metal layer structures to avoid plasma charging exceed the tolerance level are commonly used to practice in the industry [2]. Adding protective diodes [3] in parallel to a long wiring patterns can also help shunt the charging current from the transistors. These methods reduce design flexibility on structures pro to plasma induced damages.

Previous studies [4-6] report an on-wafer plasma induced charging effect detector demonstrated in advanced FinFET technologies. In order to widen the sensing range, the effect of adding different types and sizes of capacitors next to the PID detector is investigated in this work. A series of detector patterns targeting a wide range sensing are incorporated in on-wafer testlines for monitoring the plasma processing conditions.

#### **Operation Principle and Test Pattern Design**

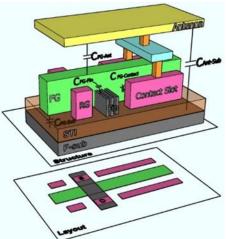

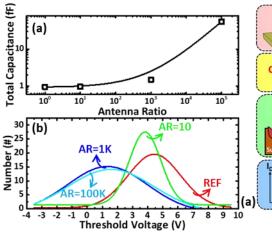

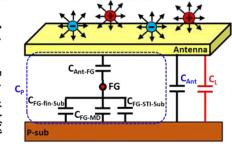

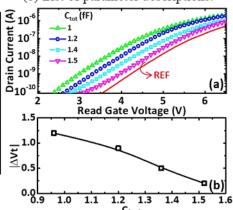

A 3D illustration and layout with the parasitic capacitances which seeing from the antenna node of a plasma induced damage recorder structure are outlined in *Figure 1*. The total capacitance on the antenna is composed of capacitance from antenna to substrate and floating gate, respectively. *Figure 2 (a)* shows the total capacitance of the antenna with raising antenna ratio. From the detectors with increasing antenna area, the distribution of threshold voltage distributions of the PID recorder across a 12-inches wafer are compared in *Figure 2 (b)*. As antenna area raises, the amount of charge collected increases, leading to more significant threshold voltage shifts.

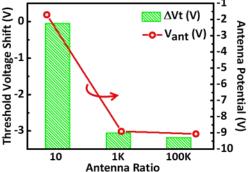

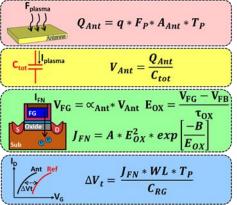

The basic operation principles of the PID detect/record device is explained on the flow chart in *Figure 3(a)*. The detecting mechanisms, starting with the charging of antenna to the final change of threshold voltage of the recorders can be described by simple charging and FN tunneling equations. *Figure 3(b)* lists all parameters used in the model correlating  $\Delta V_t$  with plasma flux seen by the antenna. *Figure 4* shows that large antenna area

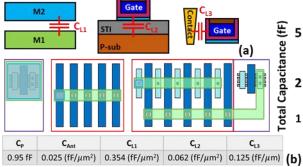

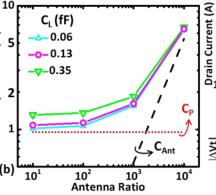

leads a saturated antenna potential,  $V_{ant}$ , causing a maximum detection limit. To avoid saturation when plasma flux level exceeds the detector limit, antenna capacitance is deliberately increased by adding  $C_L$ . To modify the charging rate on the detector's antenna during plasma processes, additional loading capacitor,  $C_L$ , for reading the sensitivities of the plasma detector is proposed. *Figure 5* illustrates all the possible capacitance on the FG-based PID detector with  $C_L$ . Three types of  $C_L$  implemented are MIM capacitor, STI capacitance per unit area/length summarized in *Figure 6(b)* suggest that MIM capacitor seems to be the most area-efficient type for extending  $C_{tot}$ .

## **Experimental Results and Discussion**

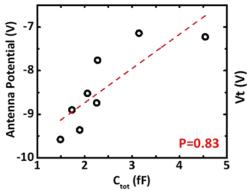

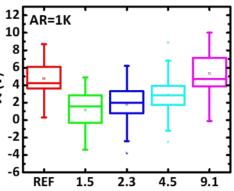

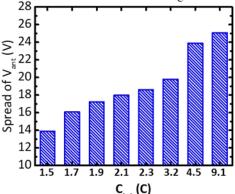

Figure 7 compares the simulated parasitic and total capacitance when different loading capacitors are added. More prominent effect on the total antenna capacitance is found for detector with AR ratio under 1000. Drain current characteristics of the PID recorder with different levels of  $C_L$  are compared in *Figure*  $\delta(a)$ . Figure  $\delta(b)$  further shows that the size of total capacitance of the antenna directly affects the measured threshold voltage shifts. For samples with low antenna ratio, the total capacitance is dominated by  $C_L$ . Antenna potential calculated based on  $\Delta V_t$ through the model in Figure 3 is plotted against  $C_{tot}$ . A strong correlation suggested that under the same plasma flux,  $V_{ant}$  can be effectively reduced, preventing saturation of the detection response. Recorded threshold voltage shifts from samples across wafer with different sizes of MIM loading capacitors with AR=1K are compared in Figure 10. By increasing C<sub>L</sub>, one can effectively attenuate the responsivities and extend the sensing range of the PID detector, as projected in Figure 11.

#### Conclusion

Plasma induced damage detector can be further optimized by connecting additional loading capacitors. The new designs allow for wide-range sensing of plasma charging levels in advanced IC processes.

#### **Acknowledgements**

The authors would like to acknowledge the support from Taiwan Semiconductor Manufacturing Company (TSMC) and Ministry of Science and Technology (MOST), Taiwan.

## References

- [1] K. M. Dowling, et al., in JMEMS, pp. 135-142, Feb. 2017.

- [2] G. Cibrario, et al., in IEEE, pp. 1-4, 2014.

- [3] A. Wallash, et al., in IEEE, pp. 385-390, 1999.

- [4] C. Wu, et al., in IEDM, pp. 7.1.1-7.1.4, 2015.

- [5] Y. Tsai, et al., in IEEE, pp. 2497-2502, June 2016.

- [6] Y. Tsai, et al., in IEDM, pp. 17.5.1-17.5.4, 2018

Figure 1. 3D schematic illustrating the parasitic capacitance seen from the antenna structure in a PID recorder.

Figure 4. Increasing antenna area leads to saturated Vt level on the detectors, while  $V_{ant}$  saturates.

Figure 6. Loading capacitors realized by different structures as illustrated in the (a) cross-sections and corresponding layouts. (b) Capacitance per unit area/length on these three types of  $C_L$  designs.

Figure 9. Projected antenna potential during plasma charging vs. the total antenna capacitance on 80 of samples.

Figure 2. (a) Total capacitance of the antenna with raising AR. (b) Distributions of measured threshold voltage from the PID devices across a 12-inch wafer.

$C_{tot} = C_P + C_{Ant} + C_L$ Figure 5. Compositions of capacitance on an antenna structure with additional load capacitor, designed to tone-down the sensitivities of the plasma detector.

Figure 7. Parasitic and total capacitance as different levels of load capacitances are added.

Figure 10. Box chart of final Vt on the detectors with MIM capacitors of increasing  $C_L$  level.

|   | Q <sub>Ant</sub> | Charges on the antenna    | Coul              |

|---|------------------|---------------------------|-------------------|

|   | Fp               | Plasma flux               | A/cm <sup>2</sup> |

|   | A <sub>Ant</sub> | Antenna collection area   | cm <sup>2</sup>   |

|   | Tp               | Plasma process time       | s                 |

|   | VAnt             | Antenna potential         | v                 |

|   | V <sub>FG</sub>  | Floating gate voltage     | v                 |

|   | ∝ <sub>Ant</sub> | Coupling ratio of antenna | Х                 |

|   | Eox              | Oxide electric field      | V/cm              |

|   | V <sub>FB</sub>  | Flat band voltage         | v                 |

|   | τοχ              | Oxide thinkness           | cm                |

|   | J <sub>FN</sub>  | FN tunneling flux         | A/cm <sup>2</sup> |

|   | ΔVt              | Delta threshold voltage   | v                 |

|   | WL               | Oxide effective area      | cm <sup>2</sup>   |

| ) | C <sub>RG</sub>  | Read gate capacitance     | Х                 |

|   |                  |                           |                   |

Figure 3. (a) Detecting mechanisms, starting with the charging of antenna to the final change of threshold voltage of the recorders. (b) List of parameter descriptions.

(b

Figure 8. (a) I-V  $\stackrel{C_{tot}}{\text{curves}}$  of the PID recorders with different levels of  $C_L$ . (b) Total capacitance of the antenna directly affect the final threshold voltage shifts.

$C_{tot}(C)$ Figure 11. Maximum V<sub>ant</sub> across a wafer are effectively widen when C<sub>tot</sub> increased by C<sub>L</sub>.