# Nonvolatile SRAMs Enabled by Hysteretic Negative-Capacitance FETs

# - A Comparative Study of Novel 9T and 8T nvSRAMs

Yi-Jui Wu, Wei-Xiang You, and Pin Su

Department of Electronics Engineering & Institute of Electronics, National Chiao Tung University, Taiwan Email: yijui850812.ee03@nctu.edu.tw , pinsu@faculty.nctu.edu.tw

#### Abstract

This work conducts a comparative study of two nonvolatile SRAM cells enabled by hysteretic negativecapacitance FETs. With the aid of a short-channel 2D-NCFET SPICE model, the stability, performance and energy consumption of novel 9T and 8T nonvolatile SRAMs have been investigated and compared. Our study indicates that, as compared with the 8T counterpart, the 9T nvSRAM possesses better write stability and read performance at the expense of slightly larger energy consumption during write and restore operation due to the higher transistor count. Both the NCFET-based nvSRAMs exhibit superior energyefficiency than other types of nvSRAMs, which is crucial to power-gating applications.

### **1. Introduction**

Compact embedded nonvolatile memories with fast data access ability is crucial for energy-harvesting near-memory computing. Several nonvolatile SRAM solutions with additional circuitry or nonvolatile memories (e.g., RRAM, MTJ, etc.) for data backup and restore have been proposed in the literatures [1]-[4]. However, the unsatisfactory power off-on energy  $(E_{S\&R})$ due to high static current in existing nvSRAMs prohibits the energy savings. In [5], a 6T2C nvSRAM cell with two ferroelectric capacitors connected to a standard 6T SRAM cell has been demonstrated experimentally. Nonetheless, the area penalty due to ferroelectric capacitors remains the major drawback compared with using transistors. Thanks to the recent discovery of ferroelectricity in doped hafnium-oxide [6], the negative-capacitance FET (NCFET) [7] with steep SS and improved on-state current has garnered substantial interest. Depending on the capacitance matching, the hysteretic-NCFET in I<sub>D</sub>-V<sub>G</sub> characteristics can also be seen. In this work, the stability, performance and energy consumption of novel 9T and 8T hybrid nvSRAMs employing 2D-FETs and hysteretic 2D-NCFETs are comprehensively examined and compared.

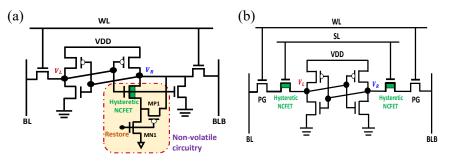

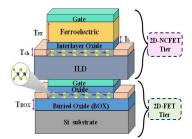

The schematics of the hybrid nonvolatile 9T and 8T SRAM cells are shown in **Fig. 1(a)** and **Fig. 1(b)**, respectively. 2D-FETs with their atomically-thin thickness has the potential for future high-density 3D technology [9]. Monolithic-3D integration offers the possibility to independently optimize two different technologies [10] such that the nonvolatile circuitry of the hybrid nvSRAM cells can be realized in the NCFET-tier as illustrated in **Fig. 2**.

## 2. Methodology

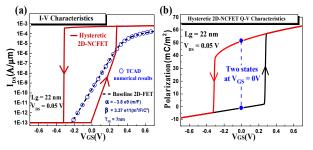

To evaluate the stability and performance of the hybrid nvSRAM cells, an accurate and physical short-channel 2D-NCFET compact model [11] calibrated with TCAD numerical simulation is adopted as shown in **Fig. 3 (a)**. The hysteretic NCFET is simulated by coupling the surface-potential-based model of the underlying 2D-FET with the 1D Landau-Khalatnikov (LK) equation in the SPICE simulator. The ferroelectric parameters of HfZrO used in this work ( $\alpha = -3.8 \times 10^9$  m/F,  $\beta = 3.37 \times 10^{11}$  m<sup>5</sup>/F/C<sup>2</sup>,  $\gamma = 0$  m<sup>9</sup>/F/C<sup>4</sup>) are extracted from the published data [12]. Pertinent parameters of channel materials (monolayer MoS<sub>2</sub> and WSe<sub>2</sub>) are judiciously chosen from the published literature [11]. The hysteretic 2D-NCFET in the hybrid nvSRAM cells can possess two states in the hysteresis loop around  $V_{gs} = 0$ V by design as shown in **Fig. 3(b)**.

One state can switch to the other with a sufficiently positive or negative gate-to-source voltage.

#### **3. Results and Discussion**

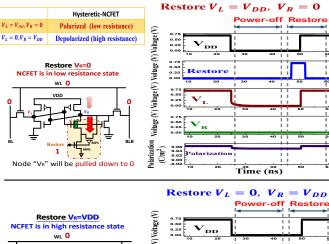

**Fig. 4** shows the transient waveforms and the operation concept of the 9T nvSRAM during restoration. For normal SRAM operation, the restore signal is grounded which isolates the nonvolatile circuitry from the storage node. The grounded restore signal also turns on the additional PMOS (MP1) and passes the value of  $V_R$  to the source terminal of the hysteretic-NCFET. During the recall period, the restore signal needs to be raised to V<sub>DD</sub> in advance. The final state of the V<sub>R</sub> will depend on the polarization state of the hysteretic-NCFET as shown in **Fig. 4**. Note that the additional NMOS (MN1) is stronger than the pull-up PMOS due to the NCeffect so that the storage node can be successfully pulled-down to ground. The three-transistor restore circuitry has also been used to realize nonvolatile flip-flop in [13].

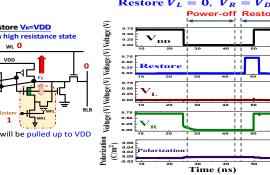

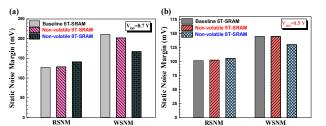

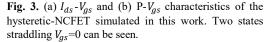

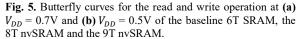

Butterfly curves for the read and write operation at (a)  $V_{DD} = 0.7V$  and (b)  $V_{DD} = 0.5V$  are demonstrated in Fig. 5. Since the restore signal is grounded during normal SRAM-mode, the extra circuitry of the 9T nvSRAM does not affect its read/write operation and stability. Fig. 6 shows the comparison of the RSNM and WSNM at  $V_{DD} = 0.7V$  and 0.5V, respectively. Note that the 9T nvSRAM shows nearly identical results with the baseline 6T SRAM. However, the previously reported 8T nvSRAM exhibits improved RSNM but degraded WSNM. This is because the hysteretic-NCFETs are in series with the pass-gates (PGs) of the baseline 6T SRAM serving as extra resistors weakening the PGs during read and write operation. With a lower supply voltage (Fig. 6(b)), the weakening effect can be alleviated due to the increasing ON-state current ratio of the hysteretic-NCFET and the baseline 2D-FET.

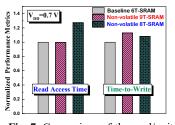

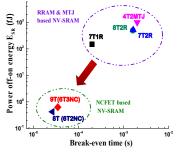

The performance comparison including read access time and time-to-write are shown in Fig. 7. Larger read access time of the 8T nvSRAM results from the degraded read current. Fig. 8 shows the energy consumption during the read and write operation. Slightly larger write energy of the 9T nvSRAM can be attributed to the extra capacitance from the restore circuitry. Fig. 9 illustrates the benchmarking of the power off-on energy  $(E_{S\&R})$  and break-eventime (BET) time for several different nvSRAMs reported [1]-[4]. It is clear that, compared with the RRAM and MTJ based nvSRAMs, the NCFET-based nvSRAMs exhibit superior energy-efficiency which is favorable for power-gating applications. Fig. 10 shows the overall comparison of the NCFET-based 9T and 8T nonvolatile SRAM cells. Although the 9T nvSRAM demonstrates better write stability and read performance, the energy consumption during write and restore operation is slightly larger due to the higher transistor count.

#### Acknowledgements

This work was supported in part by the Ministry of Science and Technology, Taiwan, under MOST-107-2221-E-009-090-MY2, MOST-109-2634-F-009-029 and MOST-109-2639-E-009-001.

#### REFERENCES

[1] A. Lee et al, VLSI Symp. Circuits. Dig., Jun. 2015 [2] P. F. Chiu et al, VLSI Symp. Circuits. Dig., Jun. 2010 [3] T. Ohsawa et al, IEEE J. Solid-State Circuits, vol. 48, no. 6, Jun. 2013 [4] S.-S. Sheu et al, Proc. IEEE Solid-State Circuits Conf., Nov. 2013 [5] M. Kobayashi et al, VLSI Symp. Tech. Dig., Jun. 2017 [6] T. S. Böscke et al. IEDM Tech. Dig., Dec. 2011 [7] S. Salahuddin and S. Datta, Nano Lett. 8, p. 405 2008 [8] W.-X. You, et al, IEEE JEDS, vol. 8, pp. 171-175, 2020 [9] A. B. Sachid et al., Adv. Material., vol.28, pp. 2547-2554, 2016 [10] C.-H. Yu et al., IEEE TED., vol. 64, no. 5, p. 2445, 2017 [11] W. X. You et al., IEEE TED, vol. 65, no. 4, p. 604, 2018 [12] M. Kobayashi and T. Hiramoto, VLSI Symp., 2015 [13] A.A.Saki et al., IEEE TCAS-I, vol. 66, no. 11, Nov. 2019

**Fig. 1. (a)** Schematic of the 9T nonvolatile SRAM cell. Three extra transistors including a hysteretic-NCFET and two hysteresis-free NCFETs are used for data restore operation. **(b)** Schematic of the previously reported 8T nonvolatile SRAM cell [8]. Two hysteretic-NCFETs are inserted in series with the PGs of the traditional 6T SRAM for data restoration.

**Fig. 4.** The transient waveforms of the 9T nvSRAM during backup/restore operation. Note that the polarization state of the hysteretic-NCFET may vary and backup automatically along with the storage nodes.

**Fig. 6.** Comparison of the RSNM and WSNM at (a)  $V_{DD} = 0.7$ V and (b)  $V_{DD} = 0.5$ V. The 9T nvSRAM shows nearly identical results with the baseline 6T SRAM.

Fig. 8. Comparison of the energy consumption during (a) read operation and (b) write operation at  $V_{DD} = 0.7$ V and 0.5V. Slightly larger write energy of the 9T nvSRAM is attributed to the extra capacitance from the restore circuitry.

**Fig. 2.** Schematic illustration of the two-tier monolithic 3D stacking. Depending on the upper-tier interlayer oxide thickness, the NCFET can be hysteresis-free or hysteretic.

Compared with 6T-SRAM

Nonvolatile 8T-SRAM

Nonvolatile 9T-SRAM

RSNM

Image: Compared with 8T-SRAM

Image: Compared with 9T-SRAM

WSNM

Image: Compared with 9T-SRAM

Image: Compared with 9T-SRAM

Read access time

Image: Compared with 9T-SRAM

Image: Compared with 9T-SRAM

Read access time

Image: Compared with 9T-SRAM

Image: Compared with 9T-SRAM

Read access time

Image: Compared with 9T-SRAM

Image: Compared with 9T-SRAM

Write energy

Image: Compared with 9T-SRAM

Image: Compared with 9T-SRAM

Area overhead

Image: Compared with 9T-SRAM

Image: Compared with 9T-SRAM

**Fig. 7.** Comparison of the read/write performance at  $V_{DD} = 0.7$ V. The capacitive load is estimated for the actual layout of 64 cells per bit line.

**Fig. 10.** Comparison of the NCFET-based 9T and 8T nonvolatile SRAMs. The direction and length of the arrows indicate the increase/decrease of the value compared with the baseline 6T-SRAM.

**Fig. 9.** Benchmarking of the power off-on energy and break-even time for several nvSRAMs in the literatures [1]-[4]. The power supply ramp-up time is assumed to be 1us for the 9T and 8T nvSRAMs.

60