# HfN Multi Charge Trapping Layers for Hf-based MONOS Nonvolatile Memory

S. Ohmi, Y. Horiuchi, H. Morita, A. Ihara, and J.Y. Pyo

Tokyo Institute of Technology J2-72, 4259 Nagatsuta, Midori-ku, Yokohama 226-8502, Japan Phone: +81-45-924-5481, E-mail: ohmi@ee.e.titech.ac.jp

#### Abstract

The effect of HfN multi charge trapping layers (CTL) on the Hf-based Metal/Oxide/Nitride/Oxide/Si (MONOS) nonvolatile memory (NVM) characteristics was investigated to improve the threshold voltage ( $V_{TH}$ ) controllability. The Hf-based MONOS NVM with HfN<sub>1.3</sub>/HfN<sub>1.1</sub>/HfN<sub>1.3</sub>/HfN<sub>1.1</sub> 4-layer CTL realized precise control of flatband voltage ( $V_{FB}$ ) and  $V_{TH}$  compared to the Hf-based MONOS with HfN<sub>1.1</sub> single layer CTL. Furthermore, the retention characteristics were found to be remarkably improved for the Hf-based MONOS NVM with HfN multi CTL.

## 1. Introduction

High-k dielectrics is effective to realize high-speed and low-voltage operation for metal-oxide-nitride-oxide-silicon (MONOS) nonvolatile memory (NVM) [1]. We have reported the Hf-based MONOS NVM with high-k HfO<sub>2</sub> and HfN<sub>1.1</sub> dielectrics. The Hf-based MONOS structures were fully in situ formed to improve the interface property by the reactive sputtering utilizing Hf target. The MONOS structures are consisted from HfN<sub>0.5</sub> gate electrode, HfO<sub>2</sub> blocking layer (BL), HfN<sub>1.1</sub> charge trapping layer (CTL), HfO<sub>2</sub> tunneling layer (TL), and we have demonstrated the multi-bit/cell operation [2-4]. However, the V<sub>TH</sub> controllability was necessary to be improved.

Tang et al. reported that the multi-layer CTL formed by the multi Zr silicate layers to improve the MONOS characteristics [5]. The multi-layer CTL was fabricated by changing the Zr and Si contents in each Zr silicate layer. The number of interfaces was increased in the CTL which led to increase the trap sites for the injected electrons.

In this paper, the effect of HfN multi-layer CTL for the Hf-based MONOS NVM was investigated to improve the threshold voltage ( $V_{TH}$ ) controllability. The HfN<sub>1.3</sub>/HfN<sub>1.1</sub>/HfN<sub>1.3</sub>/HfN<sub>1.1</sub> 4-layer CTL was fabricated by changing the N<sub>2</sub> gas flow ratio during the reactive sputtering. It is also expected that the equivalent oxide thickness (EOT) would be decreased because of the interface polarization effect [6]

## 2. Experimental Procedure

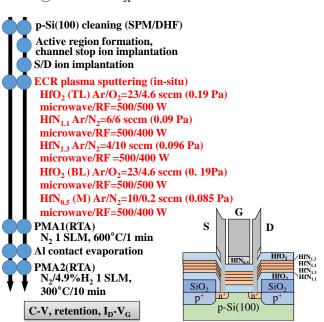

Figure 1 shows the experimental procedure used in this research. The Hf-based MONOS NVM was in situ formed on p-Si(100) substrate using the typical gate-last process [3]. After the active region formation and channel stop ion implantation, ion implantation was carried out for source and drain (S/D) regions (PH<sub>3</sub>,  $5x10^{15}$  cm<sup>-2</sup>, 20 keV) [4]. Then,

**Fig. 1.** Fabrication process and schematic cross-section of Hf-based MONOS NVM with multi CTL.

the HfN<sub>0.5</sub>/HfO<sub>2</sub>/HfN<sub>1.1</sub>/HfO<sub>2</sub> (MONO) structure was in situ deposited on p-Si(100) by electron cyclotron resonance (ECR) plasma sputtering at room temperature (RT) [3]. The designed thickness of HfO<sub>2</sub> TL was 3 nm. The HfN<sub>1.1</sub> layer CTL thickness was 2 nm. The HfN<sub>1.3</sub>/HfN<sub>1.1</sub>/HfN<sub>1.3</sub>/HfN<sub>1.1</sub>4-layer CTL was also fabricated with the thickness of 0.5 nm each. The thickness of HfO<sub>2</sub> BL and HfN<sub>0.5</sub> gate electrode was 8 nm each. Then, the post-metallization annealing (PMA1) was carried out at 600°C/1 min in N<sub>2</sub>. After the contact hole formation and Al evaporation, PMA2 was carried out at 300°C/10 min in N<sub>2</sub>/4.9%H<sub>2</sub>. The gate electrode size of the fabricated MONOS diodes was 100 x 100 µm<sup>2</sup>. The gate length (L) and width (W) of the fabricated n-channel MONOS NVM was L/W = 10/90 µm.

The fabricated Hf-based MONOS diodes and NVMs were evaluated by C-V and I<sub>D</sub>-V<sub>G</sub>. The operation conditions were set as the program voltage/time ( $V_{PGM}/t_{PGM}$ ) of 6 to10 V/1 s, the erase voltage/time ( $V_{ERS}/t_{ERS}$ ) of -6 to -10 V/1 s at  $V_D=V_S=0$  V. All the measurements were carried out at RT.

## 3. Results and Discussion

Figure 2 shows the program voltage dependence on the flat-band voltage ( $V_{FB}$ ) shift in the C-V characteristics for the fabricated Hf-based MONOS diodes. The measurement frequency was 1 MHz. As shown in Fig. 2(a), the charge-

**Fig. 2.**  $V_{PGM}$  dependence on the  $V_{FB}$  shift for the fabricated Hf-based MONOS diodes with (a) 1-layer and (b) 4-layer CTL. The measurement frequency was 1 MHz.

injection type hysteresis width was increased with the program voltage, and  $V_{FB}$  shift was not stable with the program voltage in case of the Hf-based MONOS diode with 1-layer CTL. On the other hand, the hysteresis was markedly decreased even for the  $V_{PGM}/t_{PGM}$  of 10 V/1 s, and the  $V_{FB}$  was well controlled by the program voltage as well as the erase operation in case of 4-layer CTL. Furthermore, the EOT extracted by the dual frequency method was found to be decreased from 6.4 nm for the Hf-based MONOS with 1-lyaer CTL to 6.0 nm for the Hf-based MONOS with 4-layer CTL (not shown). This is probably caused by the interface polarization effect in the 4-layer CTL.

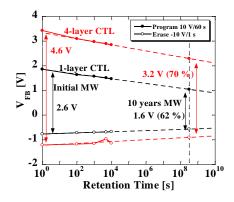

Figure 3 shows the comparison of retention characteristics for the Hf-based MONOS diodes. For the evaluation of retention characteristics, VPGM/tPGM of 10 V/60 s and  $V_{ERS}/t_{ERS}$  of -10 V/1 s were applied. Interestingly, the initial memory window (MW) was increased from 3.6 V with  $V_{PGM}/t_{PGM}$  of 10 V/1 s shown in Fig. 2(b) to 4.6 V for the Hfbased MONOS with 4-layer CTL probably due to the increase of trap states in the CTL. On the other hand, the initial MW was decreased from 5.2 V shown in Fig. 2(a) to 2.6 V for the Hf-based MONOS with 1-layer CTL. This is probably due to the de-trapping of the trapped electrons through the BL during the programing. The extrapolated MW to 10 years was decreased to 62% compared to the initial MW in case the Hfbased MONOS with 1-layer CTL, while it was 70% in case the Hf-based MONOS with 4-layer CTL.

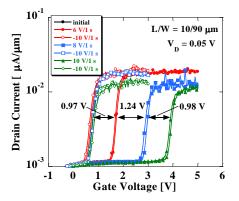

Figure 4 shows the  $I_D$ - $V_G$  characteristics of Hf-based MONOS NVM with 4-layer CTL. As shown in Fig. 4, the precise control of  $V_{TH}$  was realized with the program voltage

Fig. 3. Comparison of the retention characteristics for the Hf-based MONOS diodes.

Fig. 4.  $I_D$ -V<sub>G</sub> of n-channel Hf-based MONOS NVM with 4-layer CTL.

from 6 V to 10 V as well as the erase operation which corresponded to the C-V characteristics shown in Fig. 2(b). Negligible hysteresis was observed and the saturation mobility of  $180 \text{ cm}^2/(\text{Vs})$  was obtained.

#### 4. Conclusions

Hf-based MONOS NVM with HfN 4-layer CTL was investigated. The excellent  $V_{TH}$  controllability was demonstrated for the fabricated Hf-based MONOS NVM. Therefore, the Hf-based MONOS NVM with multi CTL is a promising device for the future analog memory applications.

#### Acknowledgements

The authors would like to thank Dr. M. Shimada and Dr. Y. Jin of JSW-AFTY for their support and useful discussions for this research. This research was partially supported by JSPS KAKENHI Grant Numbers 19H00758 and Toshiba Electronic Devices & Storage Corporation.

#### References

- [1] C. Zhao et al., Materials, 7, p. 5117 (2014).

- [2] S. Kudoh et al., 76th DRC Conf. Dig., p. 157 (2018).

- [3] S. Ohmi et. al., SSDM Ext. Abst., p. 687 (2019).

- [4] S. Ohmi et. al., Jpn. J. Appl. Phys., 59, SGGB10 (2020).

- [5] Z. Tang et al., Appl. Phys. Exp., 12, 074007(2019).

- [6] S. Ohmi et al., 77<sup>th</sup> DRC Conf. Dig., p. 181(2019).