# Over 230 fF/µm<sup>2</sup> capacitance density 9.0V breakdown voltage textured deep trench SiN capacitors toward 3D integration

Koga Saito<sup>1</sup>, Ayano Yoshida<sup>1</sup>, Rihito Kuroda<sup>1</sup>, Hiroshi Shibata<sup>2</sup>,

Taku Shibaguchi<sup>2</sup>, Naoya Kuriyama<sup>2</sup> and Shigetoshi Sugawa<sup>1</sup>

<sup>1</sup> Tohoku University, Aza-Aoba, Aramaki, Aoba-ku, Sendai-shi, Miyagi 980-8579, Japan

Phone: +81-22-795-3977, E-mail: koga.saito.s3@dc.tohoku.ac.jp

<sup>2</sup> LAPIS Semiconductor Miyagi Co., Ltd. 1, Okinodaira, Ohira-mura Kurokawa-gun, Miyagi 981-3693, Japan

Phone: +81-22-345-6203

## Abstract

Si deep trench capacitors with textured surface and SiN dielectric film are presented in this work. The developed capacitors achieved over 230fF/µm<sup>2</sup> capacitance density, 9.0V breakdown voltage and very low leakage current. The developed capacitors can be utilized for various compact electronic systems using 3D integration.

## 1. Introduction

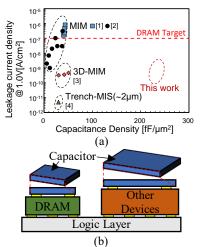

Capacitors have been important parts of integrated circuits; small bypass capacitors for LSI, RF/Microwave capacitors, and capacitive elements for analog IC and so on. For compact system integrations, high capacitance density is required. In addition, high reliability such as low leakage current and high breakdown voltage are also required for various applications. Fig. 1(a) shows the correlation between the leakage current density at 1V and the capacitance density of various types of capacitors. Metal-Insulator-Metal (MIM) capacitors and Metal-Insulator-Silicon (MIS) capacitors have low leakage current but relatively low capacitance density of about  $50 \text{ fF}/\mu\text{m}^2$  [1-4]. DRAM capacitors have a high capacitance density; however, their leakage current density is targeted to be around  $10^{-7}$  A/cm<sup>2</sup> [5], thus they are not suitable for analog applications such as sample/hold circuits and amplifiers. Consequently, there is a demand for a capacitor having a high breakdown voltage, a low leakage current, and a high capacitance density, in order to be utilized in various applications. Si trench capacitors with high quality insulator films have been explored for this purpose [6-8]. In addition, for compact system development, these capacitors should be able to be integrated with LSI using 3D integration technologies such as TSV, micro-bumps and hybrid bonding [9]. In this work, we developed versatile high capacitance density and highly reliable Si deep trench capacitors with textured surface and SiN films toward 3D integration. The size of the capacitor can be easily changed as shown in Fig. 1(b).

## 2. Capacitor design and experimental setup

Eq. (1) shows a simple capacity equation. The capacitance is decided by the surface area, the permittivity of the dielectric, and dielectric thickness. In order to expand the surface area in three dimensions, we introduced textured deep trench with highly reliable SiN as the dielectric.

$$C = \frac{3}{d}\varepsilon$$

(1)

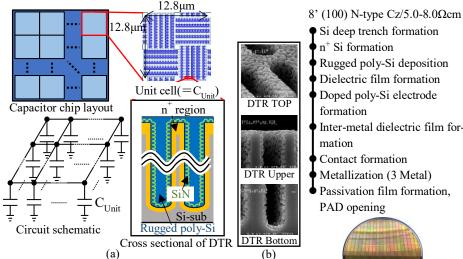

Fig. 2 shows layout diagrams of the unit cell. A chip consists of parallel unit cells with deep trench. By choosing the number of connecting unit cells we can select the capacitor area and enhance versatility. In order to suppress warping of wafers during the fabrication process, trench pattern is formed both vertically and horizontally. Fig. 3 shows the process flow

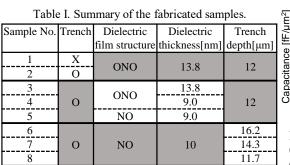

of the fabricated wafer and the wafer photograph. Voltage dependency of capacitance is reduced by introducing high doping layer in the substrate. The texture is formed by rugged poly-Si formation [10]. The buried electrode is n<sup>+</sup> doped poly-Si. High temperature process is available with this structure for high reliability. Table I shows the fabricated samples. We verified the influence of trench, dielectric film structures (ONO and NO [11]) and thickness, trench depth, and developed the optimized sample.

## 3. Results and discussions

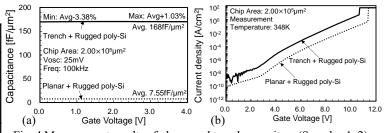

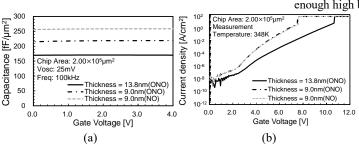

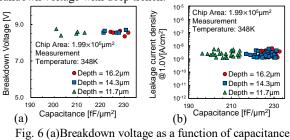

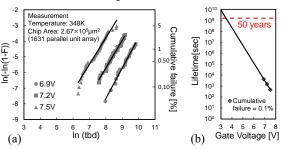

Fig. 4 shows measurement results of planar capacitors and trench capacitors (Samples 1, 2). The results show that deep trench enhances about 22 times capacitance with the high breakdown voltage. Fig. 5 shows measurement results of capacitors with different dielectric film structures and thickness (Samples 3, 4, 5). They show that NO structure and thin thickness film lead to high capacitance density and NO structure does not affect breakdown voltage. We decided to use NO structure for high capacitance density and 10 nm thickness for high reliability. Fig. 6 shows the measurement results of breakdown voltage and leakage current density as functions of capacitance density with different trench depths (Samples 6, 7, 8). The result shows no correlation between trench depth and breakdown voltage or leakage current. From the result, we decided to use 14.3µm depth and designed the optimized sample layout (Sample 7'). Fig. 7 shows the TDDB measurement results of capacitors (Sample 7'). Fig. 7(a) shows the Weibull distribution and Fig. 7(b) shows lifetime prediction with a cumulative failure probability of 0.1%, which indicates more than 50 years at 3.3V. Table II shows the performance summary of the developed capacitor. Fig. 8 shows breakdown voltage as a function of capacitance density of various fabricated structures. From the obtained trend, it is expected that the capacitance density will be further improved if the dielectric thickness is reduced for low voltage applications.

### 4. Conclusions

We developed textured deep trench SiN capacitors over 230fF/µm<sup>2</sup> capacitance density, 9.0V breakdown voltage and low leakage current. The developed capacitor is based on the versatile design with Si substrate, it can be utilized in various applications through 3D integration for compact systems.

#### References

- T. Ando et al., IEDM, p. 236-239, 2016.

- [4 [5

- Y. Koda et al., ECS Trans. 2016, vol.72, pp. 91-100, 2016.

M. Takase et al., VLSI Technol. Dig., pp. 71-72, 2018.

M. Suzuki et al., IISW, pp. 308-311, 2017.

S. K. Kim et al., Adv. Mater. 2008, pp.1429-1435, 2008.

E. Song et al., IEEE TCPMT, vol.3, no.9, pp.1467-1480, 2013. [6]

- M. Brunet et al., IEEE TPE, vol.28, no.9, pp.4440-4448, 2013.

- [8] IPDIA white paper, 2015.

[9] C.-T. Ko et al., Microelectron. Reliab., 52, pp. 302-311, 2012.

- [10] M. Ino et al., J. Vac. Sci. Technol, pp. 751-756, 1996. [11] B. De Salvo et al., Microele. Reliab. 39, pp.235-239, 1999.

Fig. 1 (a) Leakage current density at 1V as a function of capacitance density, comparing various types of capacitors. (b) Schematic illustration of system integration using stacking with other devices.

Fig. 2 Structures of a capacitor chip. (a)Layout diagrams of the unit cell with deep trench (DTR). Circuit schematic representing parallel unit cells. (b)SEM view of the fabricated textured deep trench.

Si deep trench formation n<sup>+</sup> Si formation Rugged poly-Si deposition

Dielectric film formation Doped poly-Si electrode

Inter-metal dielectric film for-

- Contact formation

- Metallization (3 Metal)

Passivation film formation, PAD opening

Fig. 3 Process flow and wafer photograph.

Fig. 4 Measurement results of planar and trench capacitors (Samples 1, 2). (a) CV characteristics showing 22 times higher capacitance density with deep trench compared to planar structure. (b) IV characteristics showing enough high breakdown voltage with deep trench.

Fig. 5 Measurement results of capacitors with different dielectric film structures and thickness (Samples 3, 4, 5). (a) CV characteristics showing NO structure and thin thickness film lead to high capacitance density. (b) IV characteristics, showing NO structure does not affect breakdown voltage.

Fig. 7 TDDB measurement results of the developed capacitors (Sample 7'). (a) Weibull distribution. (b) Lifetime prediction with a cumulative failure probability of 0.1%.

| 11.0                                      | Sample 3                   |   |  |

|-------------------------------------------|----------------------------|---|--|

| 10.0                                      | SiO <sub>2</sub> This work | Г |  |

| 9.0                                       | Sample 7'                  |   |  |

| 8.0                                       | Sample 4                   |   |  |

| 7.0                                       | Rugged-Poly,SiN(ONO)       |   |  |

| 6.0                                       | 1                          | ] |  |

| 5.0                                       |                            | L |  |

| 5                                         | 0 150 250 350              |   |  |

| Capacitance Density [fF/µm <sup>2</sup> ] |                            |   |  |

|                                           |                            |   |  |

Fig. 8 Comparison of breakdown voltage as a function of capacitance density among various fabricated structures.

| developed capacitor.                    |                                                          |  |  |

|-----------------------------------------|----------------------------------------------------------|--|--|

| Technology                              | Deep trench<br>+ Rugged poly-Si<br>+ Unit cell structure |  |  |

| Area of unit cell                       | 12.8µm x 12.8µm                                          |  |  |

| Dielectric film structure<br>/thickness | NO/10nm                                                  |  |  |

| Trench depth                            | 14.3µm                                                   |  |  |

| Capacitance                             | 235fF/µm <sup>2</sup>                                    |  |  |

| Breakdown voltage                       | 9.0V                                                     |  |  |

| Leakage current<br>density(at 1V)       | Below 10 <sup>-8</sup> A/cm <sup>2</sup>                 |  |  |

| TDDB lifetime(at 3.3V)                  | Over 50 years                                            |  |  |

12.0

Breakdown Voltage [V]