# New 1200V Bidirectional FS-IGBT (BFS-IGBT) with Short-Circuit Capability

Masahiro Tanaka<sup>1</sup>, Naoki Abe<sup>1</sup> and Akio Nakagawa<sup>2</sup>

<sup>1</sup> Nihon Synopsys G.K.

2-21-1 Tamagawa, Setagaya-ku, Tokyo 158-0094, Japan Phone: +81-3-6746-3888 E-mail: mtanaka@synopsys.com

<sup>2</sup> Nakagawa Consulting Office, LLC.

3-8-74, Hamatake, Chigasaki-city, Kanagawa 253-0021, Japan E-mail: akio.nakagawa.dr@ieee.org

## Abstract

We propose a new bidirectional FS-IGBT for high voltage applications. Newly developed MOS gate structure with unique N-emitter/P-base and CS/N-buffer layers realize FS-IGBT I-V characteristics for both directions. An optimized N-buffer layer works as CS layer in the cathode and reduces on-state voltage. In result, the device has superior trade-off relationship between on-state voltage and turn-off loss, and even realizes enough shortcircuit withstand capability.

## 1. Introduction

Bidirectional FS-IGBT has conduction and blocking capabilities for both polarities. It realizes AC-AC matrix converters, which achieve much smaller size than DC-linked type converters.

For the matrix converter applications, MBS structures and IGBT structures with reverse blocking capability have been proposed [1-4]. However, in order to adapt the devices to the realistic applications, further loss reduction and ruggedness such as short-circuit withstand capability should be required. In this paper, we propose new bidirectional FS-IGBT structure by using 3D TCAD simulations. It improves the trade-off relationship between on-state voltage drop and turn-off loss by optimizing carrier distribution profiles in the N-base. It also realizes 10us short-circuit withstand capability.

## 2. Structure and basic operation

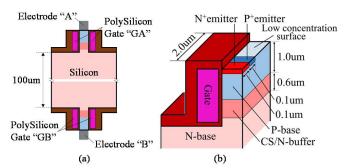

Proposed structure is illustrated in Fig. 1. MOSFET cells are symmetrically formed on the front and rear side of the semiconductor wafer.

Fig. 1 Proposed bidirectional FS-IGBT structure. (a) Cross sectional view of the whole structure. (b) Schematic view of the cell design. Narrow P+ and N+ emitter segments are formed for depth direction. CS/N-buffer layer is located between P-base and N-base.

The structural parameters of the proposed device are summarized in Table I. Narrow segmented N+/P+ layers and a large low concentration P-base surface are designed. The low concentration P-base surface realizes low hole injection efficiency when it is in the Anode side. A CS/N-buffer layer works as FS(Field Stop) layer and realizes 1500V blocking capability with 100um N-base. It also works as CS layer and achieves high electron injection efficiency from the MOS gate[5] when it is in the Cathode side. Thus, CS/N-buffer layer improves trade-off relationship between on-state voltage drop and turn-off loss. The N+ emitter width is set at 0.1um in order to reduce the saturation current, which affects short-circuit withstand capability. The device is 1.2kV class and the operating gate voltage is 5V.

Table I Device structural parameters.

| N-base thickness | 100um | Unit half cell pitch for horizontal direction | 4.0um |

|------------------|-------|-----------------------------------------------|-------|

| P-base depth     | 1.0um | Mesa width                                    | 2.0um |

| Trench depth     | 2.0um | Gate oxide thickness                          | 33nm  |

The device operation is similar to conventional FS-IGBT. When positive voltages are applied to the electrodes B and GA against A, electrons flow from A to B via MOS channel. Conversely, holes flow from B to A. They cause conductivity modulation in the N-base. It is a unique characteristic feature of this device that the hole injection efficiency can be controlled by the gate bias of the Anode side. When a negative gate bias is applied to the gate GB against B, a P-channel is formed and increases hole injection. When an enough positive gate bias is applied to the gate GB against B and makes short-circuit between N-base and Anode N+ layer by the Nchannel, the hole injection is reduced.

## 3. Results and discussion

## Blocking, forward and switching characteristics

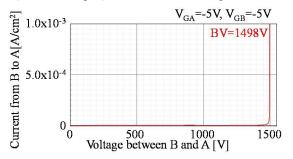

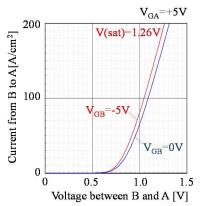

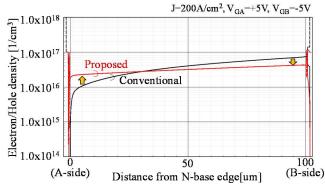

Proposed bidirectional FS-IGBT has been analyzed by 3D TCAD simulations. It is shown in Fig. 2 that the breakdown voltage of the proposed device is 1498V. It is shown in Fig. 3 that the proposed device has low on-state voltage drop of 1.26V at 200A/cm<sup>2</sup>. The I-V characteristics can be controlled by negative gate bias for the Anode side. It is shown in Fig. 3 that the proposed device achieves flat on-state carrier distribution profiles, compared with conventional device, such as MBS, which does not have the low concentration P-base surface nor CS/N-buffer layer. It is because the hole injection

efficiency in the Anode side is reduced by the low concentration P-base surface (B-side in Fig. 4). The electron injection efficiency in the Cathode side increases by the CS/N-buffer layer (A-side in Fig. 4). It acts as a barrier against holes.

Fig. 2 Breakdown characteristic of the proposed device.

Fig. 3 Forward I-V characteristics of the proposed device. The onstate voltage drop can be reduced by applying a negative gate bias to the Anode side.

Fig. 4 On-state carrier distribution in the N-base. Proposed device achieves lower hole injection efficiency from the Anode side (Bside) and higher electron injection efficiency from the Cathode side (A-side), than conventional device such as MBS.

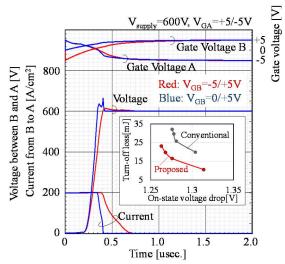

The turn-off waveforms are shown in Fig. 5. In the turnoff, it is found that, in the case where the gate bias of the Anode side changes from zero to +5V, the switching speed becomes faster, compared with the case where the gate bias changes from -5V to +5V. Thus, it is important to set the gate voltage at zero before turn-off because the excess carriers are reduced by removing the P-channel prior to the turn-off. It is also shown in the inlet of Fig. 5 that the proposed bidirectional FS-IGBT improves the trade-off relationship between on-state voltage drop and turn-off loss.

Fig. 5 Turn-off switching waveforms of inductive load circuit. The initial gate voltage of the Anode side affects the turn-off speed. Trade-off relationship between on-state voltage drop and turn-off loss is also shown. Proposed device improves on-state voltage drop as well as turn-off loss by introducing low concentration P-base surface and CS/N-buffer layers.

#### Short-circuit withstand capability

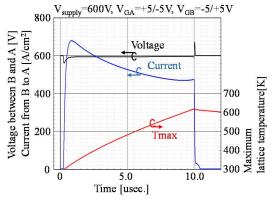

It is shown in Fig. 6 that the proposed bidirectional FS-IGBT has 10us short-circuit withstand capability. The saturation current during the operation is restricted less than  $700 \text{A/cm}^2$  by the narrow segmented N+ emitter. The temperature increase is successfully suppressed below 630K.

Fig. 6 Short-circuit waveforms. The device is successfully turned off after 10us.

#### 3. Conclusions

A new bidirectional FS-IGBT was proposed. Carrier injection efficiencies and saturation current are optimized by narrow P+/N+ emitters, low concentration P-base surface and CS/N-buffer layers. We also confirmed that the proposed device has enough short-circuit withstand capability.

#### References

- [1] K. D. Hobart et al., Proc.of ISPSD'99 (1999), 45.

- [2] R. Sittig and F. Heinke, Solid-State Electronics 44 (2000) 1387.

- [3] R. Sittig and F. Heinke, Solid-State Electronics 44 (2000) 1393.

- [4] M. Takei et al., Proc. of ISPSD'01 (2001), 413.

- [5] H. Takahashi et al., Proc. of ISPSD'01 (2001), 445.