# Altitude Dependent Failure Rate Calculation for High Power Semiconductor Devices in Aviation Electronics

Srikanth Gollapudi<sup>1</sup>, Ichiro Omura<sup>2</sup>

<sup>1</sup> Kyushu Institute of Technology

2-4, Hibikino, Wakamatsu-ku, Kitakyushu 808-0196, Japan

Phone: +81-80-8877-7200 E-mail: gollapudisrikanth.elec@gmail.com

<sup>2</sup> Kyushu Institute of Technology

2-4, Hibikino, Wakamatsu-ku, Kitakyushu 808-0196, Japan

Phone: +81-70-5464-1602

## Abstract

In this paper, we calculated the failure rate of high power semiconductor devices due to cosmic ray neutrons induced breakdown. This failure is found to occur during reverse bias condition at a voltage, which in practice well below the actual breakdown voltage of the device. Power semiconductor devices operating at airplane altitudes are more susceptible to this failure compare to the terrestrial operation.

## 1. Introduction

Traditionally, the static blocking capability of a power device is determined based on avalanche breakdown phenomena. During the early nineties, a new failure mode is found in power devices. A localized breakdown in the bulk of a device is observed due to this failure. The reason for this failure was attributed to the cosmic radiation present in the atmosphere and occurs at a voltage, which in practice well below the typical avalanche breakdown voltage of the power device.

The cosmic ray neutron flux density rises almost exponentially with altitude [1]. It was observed that, it is 80-150 times higher at airplane altitude than at sea level [2]. So the knowledge about altitude dependent failure rate of high voltage power device is essential during the design stage of power electronic system for avionics.

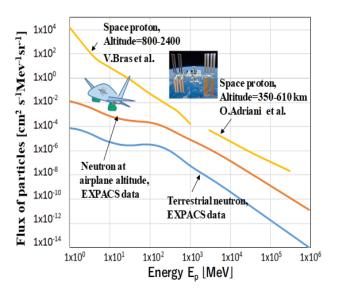

In this paper, we proposed the methodology to calculate the power semiconductor device failure rate as a function of altitude and operating voltage by decoupling the cross-section and the neutron flux spectrum (ex. EXPACS data base, shown in Fig. 1).

## 2. Cosmic ray induced failure rate calculation

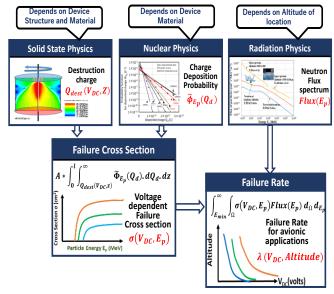

Device failure rate calculation process involves dealing with solid state physics, nuclear physics and radiation physics (Fig. 2). Failure cross section is obtained by integrating critical charge for device destruction and the probability of charge deposition in silicon by the cosmic ray particle as shown in equation (1). The parameters are given in Table I.

$$\sigma(V_{DC}, E_p) = A \int_0^l \int_{Q_{dest}(V_{DC}, Z)}^\infty \tilde{\phi}_{E_p}(Q_d) dQ_d dz \quad (1)$$

Integrating this failure cross section with the particle flux gives the failure rate ( $\lambda$ ) as shown in equation (2).

$$\lambda = \int_{E_{min}}^{\infty} \int_{\Omega} \sigma \big( V_{DC}, E_p \big) Flux(E_p) \ d_{\Omega} \ d_{E_p}$$

(2)

Fig. 1. Neutron and proton spectrum at various altitudes

Fig. 2. Failure rate calculation process

*Neutron Flux spectrum at airplane altitude*

The neutron flux spectrum up to flight altitude is obtained from EXPACS data [4]. EXPACS is a particle and heavy ion

transport code system (PHITS) based analytical radiation modelling the atmosphere.

Energy deposition probability

Probability of charge deposition in silicon by the energetic particle for different particle energies for a thickness of 300µm is considered from literature [5].

| Table I – Parameter symbols and units used in equation (1-2) |                                 |                                                                     |

|--------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------|

| Symbol                                                       | Parameter name                  | unit                                                                |

| σ                                                            | Failure cross section           | $cm^2$                                                              |

| Flux                                                         | high energy particle flux       | MeV <sup>-1</sup> s <sup>-1</sup> cm <sup>-2</sup> sr <sup>-1</sup> |

| $E_p \ \Omega$                                               | Particle energy                 | MeV                                                                 |

|                                                              | Solid angle                     | sr                                                                  |

| A                                                            | Device area                     | $cm^2$                                                              |

| $Q_{dest}$                                                   | Critical amount of deposited    | С                                                                   |

|                                                              | charge                          | C                                                                   |

| $	ilde{\phi}_{E_p}(Q_d$ )                                    | Deposited charge probability in | $C^{-1}cm^{-1}$                                                     |

|                                                              | silicon                         |                                                                     |

| $O_d$                                                        | Deposited charge                | С                                                                   |

| $egin{array}{c} Q_d \ V_{DC} \end{array}$                    | Applied voltage                 | V                                                                   |

| Z                                                            | Position along depth direction  | μm                                                                  |

| l                                                            | i-layer thickness               | μm                                                                  |

| λ                                                            | Failure rate                    | FIT*                                                                |

|                                                              | * FIT                           | Failure/10 <sup>9</sup> hours                                       |

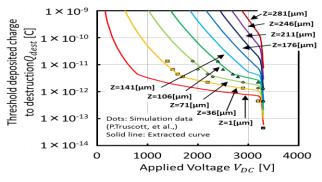

#### Critical charge for device destruction

Critical charge for device destruction  $Q_{dest}$  ( $V_{DG}$  z) is nothing but the threshold of charge that cause the device failure. The critical charge for device destruction for a 300µm PiN diode with charge deposition at different locations is shown in Fig. 3.

Fig. 3. Critical amount of charge for destruction [3]

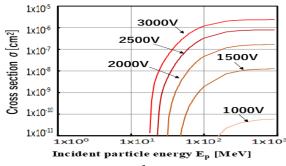

Fig. 4. Cross section  $\sigma$  [cm<sup>2</sup>] of a 300µm PiN diode [3]

Cross section calculated by the use of  $Q_{dest}$  (Fig. 3) for a PiN diode with 300µm thickness is shown in Fig. 4.

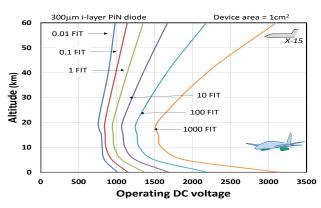

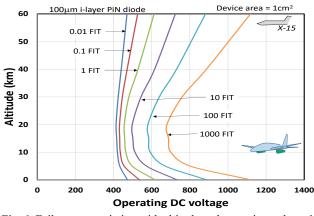

The altitude dependent failure rate for  $300\mu m$  and  $100\mu m$  PiN diode as a function of operating voltage is shown in Fig. 5 and Fig. 6.

#### 4. Conclusions

We proposed the methodology to calculate the power - semiconductor device failure rate as a function of altitude and - operating voltage. We introduced new formulation by decoupling the cross-section and the neutron flux spectrum to obtain altitude dependent failure rate of high voltage power device for avionics applications. We successfully demonstrated failure rate variation with altitude using neutron flux spectrum from EXPACS data base.

Fig. 5. Failure rate variation with altitude and operating voltage in 300µm PiN diode

Fig. 6. Failure rate variation with altitude and operating voltage in 100 µm PiN diode

#### References

- [1] H.R Zeller., Microelectron. Reliab. Vol.37, pp.1711-1718, 1997.

- [2] Goldhagen, MRS Bull., 28(2)(2003), pp.131-135

- [3] M Sudo et al., Microelectron. Reliab. Vol. 100-101, 2019.

- [4] T.Sato, PLOS ONE,11(8):e0160390(2016).

- [5] P Truscott et al., Proc of RADECS`05,pp. LN11-1-LN11-4,2005.