# Estimation of Seebeck Coefficient of Si Wire Laterally Lying on Oxide-Covered Substrate

K. Katayama<sup>1</sup>, M. M. H. Mahfuz<sup>1</sup>, M. Tomita<sup>1</sup>, S. Hirao<sup>1</sup>, S. Tanabe<sup>1</sup>, T. Matsukawa<sup>2</sup>,

T. Matsuki<sup>1,2</sup>, H. Inokawa<sup>3</sup>, H. Ikeda<sup>3</sup>, T. Watanabe<sup>1</sup>

<sup>1</sup> Faculty of Science and Engineering, Waseda University, 3-4-1 Okubo, Shinjuku-ku, Tokyo 169-8555, Japan

Email: katayama.kazu@akane.waseda.jp

<sup>2</sup> National Institute of Advanced Industrial Science and Technology (AIST),

1-1-1 Umezono, Tsukuba-shi, Ibaraki 305-8568, Japan

<sup>3</sup> Research Institute of Electronics, Shizuoka University, 3-5-1 Johoku, Naka-ku, Hamamatsu 432-8011, Japan

#### Abstract

We characterized the Seebeck coefficient of Si wires formed on an oxide-covered substrate, which is an essential component of a proposed planar-type micro thermoelectric (TE) generator. The Si wires are laterally lying on the oxide-covered substrate, so that the injected heat current leaks out from the Si wires to the substrate. Nevertheless, the Seebeck coefficient of the Si wires was not so deteriorated from a nearly adiabatic case where Si wires are suspended in air.

## 1. Introduction

Towards the IoT society, TE generator is attracting many attentions as a permanent power source for distributed sensor nodes. Si-based TE generator is one of the expected power sources because they are manufacturable using Si CMOS process<sup>[1]</sup>.

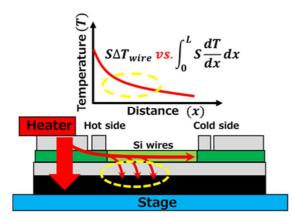

Recently, we proposed a cavity-free planar TE generator with using Si wires which are fabricated on an SiO<sub>2</sub>/Si substrate. In this device architecture, as shown in Fig. 1, most of the heat current injected into the Si wires leak out toward the substrate, thereby the temperature profile in the Si wires no longer render a linear gradient <sup>[2]</sup>. Although the heat leakage seems unfavorable to exploit the TE ability, it is not certain that the Seebeck coefficient is effectively deteriorated in the Si wires laterally lying on the substrate. Here, the effective Seebeck coefficient is defined as the open-circuit output voltage divided by the temperature difference between both ends.

In this study, we estimated the effective Seebeck coefficient of Si wires formed directly on an SiO<sub>2</sub>/Si substrate. The precise temperature difference across the Si wire was estimated by metal wire resistance thermometers formed at both ends of the Si wires.

#### 2. Experimental

The effective Seebeck coefficient of Si wires was evaluated by varying the number of wires, the width, and the spaces between each wire.

The Si wire samples were prepared by the following processes. First, a p-type Si (100) SOI substrate (SOI: 88 nm, BOX: 145 nm, Si-substrate: 745  $\mu$ m) was patterned by electron beam lithography and reactive ion etching, and a thermal oxide film about 20 nm was formed on the surface. Subsequently, P<sup>+</sup> ions were implanted at dose of  $1.0 \times 10^{15}$  cm<sup>-2</sup> and acceleration energy of 25 keV, and activation annealing (950 °C, 10 min) was performed. The thickness and active impurity concentration of the Si wires were about 70 nm and  $7 \times 10^{19}$  cm<sup>-3</sup>, respectively. Finally, metal films (Ti: 10 nm, TiN: 30 nm, Al: 400 nm) were deposited by sputtering to form electrodes and resistance thermometers

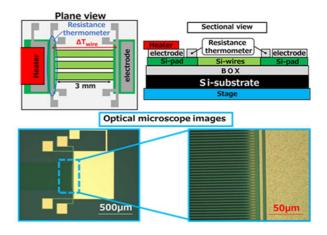

which measures the temperature difference between both ends of the Si wires ( $\Delta T_{wire}$ ). Then, a forming gas annealing (FGA) was conducted to the samples whose spaces between each wire were varied. We prepared three different numbers of Si wires (5, 20, and 100), two different widths (0.5 and 2.0 µm), and four different spaces between each wire (0.5, 1.0, 2.0 and 10 µm). The Si wire length is set to 3.0 mm.

Fig. 2 shows the schematic of TE generators. For the calibration of the resistance thermometers, the stage temperature was changed from 20 °C to 40 °C to measure the temperature coefficients of the resistance thermometers. The temperature coefficients of metal wire samples with and without FGA were about 0.330%/K and 0.341%/K, respectively. Upon the TE power measurement, a micro heater was pressed on the hot side electrode of the TE generator. The temperature difference between the micro heater and the stage was kept at 15 K. The  $\Delta T_{wire}$  was determined by measuring the resistance of thermometers. Finally, the open-circuit output voltage ( $V_{oc}$ ) of the TE generator was measured by a nano-volt meter to estimate the Seebeck coefficient.

#### 3. Results and Discussion

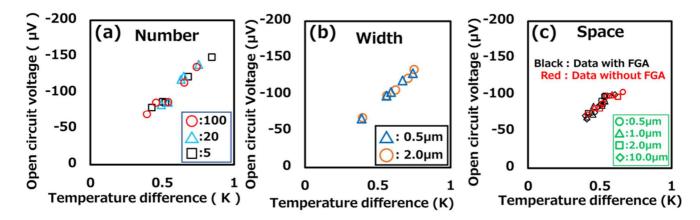

The measurement results of the  $\Delta T_{wire}$  and the  $V_{oc}$  are summarized in Fig. 3. The horizontal axis is the  $\Delta T_{wire}$ . Although the externally applied temperature difference between the micro heater and the stage is kept constant at 15 K, the contact thermal resistance between the sample and hot/cold sources varied from measurement to measurement. Therefore, the  $\Delta T_{wire}$  was changed for each measurement.

Clear proportional relationships appear between the  $\Delta T_{wire}$ and the V<sub>oc</sub> in Fig 3(a), (b) and (c). The Seebeck coefficient was estimated to be approximately –170 µV/K. In literature, the Seebeck coefficient of the SOI layer is reported to be –500 µV/K at an impurity concentration of 5×10<sup>19</sup> cm<sup>-3</sup> <sup>[3]</sup>. A simulation ignoring phonon drag effect estimated the Seebeck coefficient to be –130 µV/K at an impurity concentration of 7 × 10<sup>19</sup> cm<sup>-3</sup> <sup>[3]</sup>. Present result is very closer to the simulation result, but the coincidence does not necessarily substantiate the vanishing of the phonon drag, because the Si wires used in this work is wide enough to compare the SOI film thickness. Anyway, the effective Seebeck coefficient estimated in this work is similar in the order of the previous report.

As shown in Fig. 3(a), there is no meaningful difference in the distribution of the  $\Delta T_{wire}$  for different number of Si wires, in spite that the thermal resistance of the Si wires differs by 20 times. The result shows that the thermal resistance of the Si wires is negligible in our device. This is because that most of the heat current flow into the substrate and only small portion of heat current spreads into Si wires to establish the temperature gradient<sup>[2]</sup>.

For the same reason, the width and the space do not affect the temperature difference across the Si wires as shown in Fig. 3(b) and (c). The effect of the space between each wire on the TE performance was not observed in our previous work <sup>[4]</sup>.

It was reported that the FGA is effective to suppress an anomalous change in the Seebeck coefficient of thin Si wires with 45 nm <sup>[5]</sup>. However, as shown in Fig. 3(c), there is no significant change in Seebeck coefficient before and after FGA. This is considered due to the difference in the Si wires; present work employs 0.5 and 2.0  $\mu$ m-wide Si wires, which are much wider than the previous report <sup>[5]</sup>.

In our device architecture, width of Si wire is found to be unessential to enhance the TE performance, so that the Si wires can be replaced with wide Si membrane.

#### 4. Conclusions

We estimate the Seebeck coefficient of Si wire laterally lying on  $SiO_2/Si$  substrate. The clear proportional relationships between the temperature differences and the

TE voltages is obtained by using metal wire resistance thermometers. The effective Seebeck coefficients was not deteriorated much compared to the reported value <sup>[3]</sup>. Therefore, it is found that our proposed cavity-free planar TE generator has the potential for enough TE performance. It is future work to evaluate effective Seebeck coefficient of short Si wires on SiO<sub>2</sub>/Si substrate.

## Acknowledgements

This work was supported by CREST, JST (JPMJCR19Q5). A part of this study was supported by NIMS Nanofabrication Platform in Nanotechnology Platform Project sponsored by the Ministry of Education, Culture, Sports, Science and Technology (MEXT), Japan.

#### References

G. Hu, H. Edwards and M. Lee, Nature Electronics 2, pp.300-306 (2019). [2] M. Tomita et al., VLSI Symp. Tech. Dig. (2018) 93.

F. Salleh et al., Appl. Phys. Express 2, 071203 (2009). [4] S Tanabe et al., IWDTF. "Effect of Embedding in Dielectric Film on the Performance of Si-Nanowire Thermoelectric Generator" (2019).

Hashimoto et al., Appl. Phys. Lett. 111, 023105 (2017).

Fig. 1 Heat current illustration in cavity-free structure.

Fig. 2 Schematic views of TE generators.

Fig. 3  $\Delta T_{\text{wire}}$  vs. V<sub>oc</sub> obtained by metal wire resistance thermometers. (a) the devices with 5, 20, and 100 parallel Si wires when width and space are 2  $\mu$ m. (b) the devices with 0.5  $\mu$ m-wide 40-parallel Si wires and 2.0  $\mu$ m-wide 10-parallel Si wires when space is 2.0  $\mu$ m. (c) the devices with Si wire spaces of 0.5, 1.0, 2.0, and 10  $\mu$ m when width and number are 2.0  $\mu$ m and 50, respectively. The Si wire length is set to 3.0 mm.