L-10-05 (Late News)

# Differential-Drive CMOS Rectifier with Photovoltaic-Assist and Self-Vth-Cancellation Schemes

Toki Watanabe<sup>1</sup>, Ren Usami<sup>1</sup>, Takao Komiyama<sup>1</sup>, Yasunori Chonan<sup>1</sup>, Hiroyuki Yamaguchi<sup>1</sup> and Koji Kotani<sup>1</sup>

> <sup>1</sup> Akita Prefectural University 84-4 Aza Ebinokuchi Tsuchiya, Yurihonjo Akita 015-0055, Japan Phone: +81-184-27-2105 E-mail: kotani@akita-pu.ac.jp

### Abstract

In this study, a differential-drive CMOS RF rectifier equipped with photovoltaic assist and self-Vth-cancellation mechanisms is developed for efficient energy harvesting from ambient radio waves. By dynamically biasing the MOSFET gates with differential input signal, both onresistance and reverse leakage current of the MOSFET are reduced and high power conversion efficiency (PCE) can be achieved. In addition to the differential-drive dynamic biasing, the combination of self-Vth-cancellation (SVC) technology, which biases the gate by DC output voltage of the rectifier itself, and photovoltaic (PV) assist technology using photo-generated voltage of the on-chip PV cell allows further improvement of the PCE under low input power conditions. As a result, this rectifier operates with higher efficiency than the previously reported simple differentialdrive rectifier and single-ended PV-assisted SVC rectifier under low input power conditions. The PCE of 38% was achieved at an input power level of -22.5 dBm, a frequency of 1 GHz, an output load resistance of 10 k $\Omega$ , and a light irradiance of 1 W/m<sup>2</sup>.

## 1. Introduction

Energy harvesting from ambient energy sources is gaining attention as a technology for powering IoT devices such as remote sensors. There are various energy sources around us like light, heat, electromagnetic wave, and vibration. Energy harvesting from ambient radio waves is performed by converting the received radio frequency (RF) signals into direct current (DC) power by a rectifier. Since the receivable power level in RF energy harvesting is tiny and the input signal voltage applied to the rectifier is small, the main loss of the rectifier is caused by the turn-on voltage of the rectifier diode. In general, in CMOS integrated circuit technology, a diodeconnected MOSFET is used as a rectifying diode, where the turn-on voltage is equal to the threshold voltage (Vth) of the MOSFET. Therefore, lowering the effective Vth of the MOSFET can reduce the loss and improve the PCE. Based on this understanding, various high efficiency rectifiers that compensate Vth to improve PCE have been proposed.

One such high-performance rectifier is the differential-drive CMOS rectifier [1]. In the rectifier, high PCE can be obtained by dynamically biasing the MOSFET gates with differential input signal. The on-resistance and reverse leakage current can be reduced at the same time. To the best of authors' knowledge, it is the most efficient rectifier circuit topology in the RF energy harvesting applications. The photovoltaic (PV)-assisted self-Vth-cancellation (SVC) CMOS rectifier [2] has been proposed as an example of the "synergistic ambient energy harvesting" concept. This rectifier circuit compensates for Vth of the MOSFET not only with the DC output voltage generated by the rectifier itself but also with the voltage generated by the on-chip PV cell. Compared with a simple voltage doubling rectifier, Vth is effectively compensated for and high PCE can be obtained under the wide input power range.

In this study, a differential-drive PV-assisted SVC CMOS rectifier circuit that combines PV-assisted and SVC techniques with a differential-drive CMOS rectifier circuit is newly proposed for further improvement of the PCE under low input power conditions. Measurement results of the fabricated prototype chip are also reported.

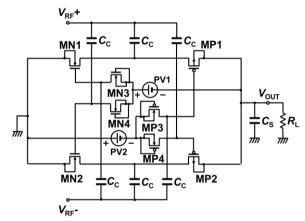

Fig. 1 Differential-Drive PV-assisted SVC CMOS rectifier.

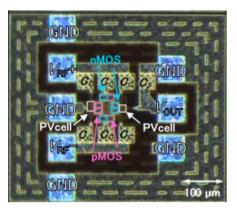

Fig. 2 Photomicrograph of a differential-drive PV-assisted SVC CMOS rectifier test circuit.

# 2. Differential-Drive PV-Assisted SVC CMOS Rectifier

The proposed differential-drive PV-assisted SVC CMOS rectifier circuit is shown in Fig. 1. Based on the differentialdrive CMOS rectifier [1], on-chip PV cell (PV1) and diodeconnected MOSFETs (MN3, MN4) are inserted in the gate bias paths of nMOS's (MN1, MN2) fed from the output of the rectifier V<sub>OUT</sub>. In the same way, on-chip PV cell (PV2) and diode-connected MOSFETs (MP3, MP4) are inserted in the gate bias paths of pMOS's (MP1, MP2) fed from the GND. This configuration improves the PCE especially under low input power conditions by dynamically and statically biasing the gate by superimposing DC output voltage generated by the rectifier itself and photo-generated voltage from the PV cell onto a differential input signal. Diode-connected MOSFETs (MN3, MN4, MP3, MP4) are used as high resistance elements. They isolate the PV cells from high-frequency nodes, thus minimizing parasitic losses due to the high-frequency current flow.

A test circuit for the proposed differential-drive PV-assisted SVC CMOS rectifier was designed and fabricated with a 0.18  $\mu$ m 5-ML CMOS process. The channel width/length of nMOS's (MN1, MN2) and pMOS's (MP1, MP2) used for rectification was 3.6  $\mu$ m/0.18  $\mu$ m and 10.8  $\mu$ m/0.18  $\mu$ m, respectively. The channel width/length of nMOS's (MN3, MN4) and pMOS's (MP3, MP4) for low-pass filtering was 0.22  $\mu$ m/3.5  $\mu$ m. The transistor area was covered by the top two metal layers for shading. The PV cell area (surface diffusion layer) was 7 × 7  $\mu$ m<sup>2</sup>. Both coupling capacitor *C*<sub>C</sub> and output smoothing capacitor *C*<sub>S</sub> were designed to be 1.13 pF. Fig. 2 shows a photomicrograph of a fabricated test chip.

The test chip was evaluated by on-wafer measurement. PCE measurements were performed at an RF input frequency of 1 GHz and an output load resistance of 10 k $\Omega$ . A vector network analyzer (Keysight N5242A) was used to apply true-differential RF signal to the rectifier by iTMSA and measure the mixed-mode reflection coefficient. An LED lamp that emulates a normal indoor lighting environment was used as a light source. For fair comparisons, simple differential-drive rectifier [1] and single-ended PV-SVC rectifier [2] were also designed and measured again at the same time by ourselves under the same measurement conditions.

### 3. Measurement results And Discussion

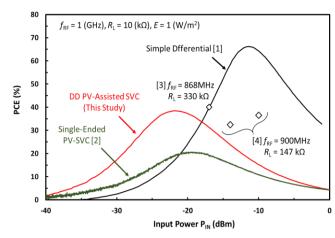

Measured results are shown in Fig. 3. The light irradiance was 1 W/m<sup>2</sup>. As compared with the simple differential-drive CMOS rectifier, a higher PCE was obtained for the input power range from -40 dBm to -18 dBm. Specifically, at an input power of -22.5 dBm, the PCE was 38%. Since the typical room light intensity is  $\sim 3$  W/m<sup>2</sup>, high PCE is obtained even at indoor-level light intensity. Compared with a single-ended PV-assisted SVC CMOS rectifier, the PCE has improved by about two times over entire input power range.

On the other hand, in the proposed circuit, Vth is excessively compensated for by the output voltage of the rectifier under the high input power region, which results in a significant increase in the reverse leakage current and the degradation of the PCE.

Fig. 3. Measured PCE as a function of  $P_{IN}$ .

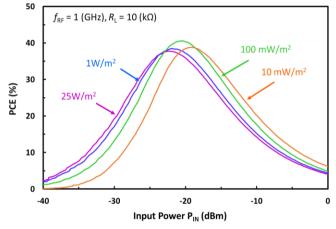

Fig. 4. Measured PCE dependence on light irradiance E.

In the figure, previously reported measured PCEs of 900 MHz range rectifiers developed by other groups [3], [4] are also plotted. Note that measurement conditions of them are different from ours, especially output load resistance was much higher than us, which is advantageous for obtaining high PCE. While the peak PCE of our newly developed rectifier is almost on the same level as others, it is obtained at much lower input power level.

PCE variation when the light intensity is varied from 10  $\text{mW/m}^2$  to 25 W/m<sup>2</sup> is shown in Fig. 4. Since the output voltage of the PV cell increases by increasing the light intensity, the curve of the PCE shifts to the low input power direction.

### Acknowledgement

This research was conducted through the VLSI Design and Education Center (d.lab-VDEC), University of Tokyo, in cooperation with Cadence Japan Corporation, Keysight Technologies Corporation, ROHM Corporation, and Toppan Printing Corporation.

### References

- [1] K. Kotani, et al., IEEE J Solid-State Circuits 44 (2009) 3011.

- [2] R. Usami, et al., IEEE A-SSCC (2018) 115.

- [3] M. Stoopman, et al., IEEE J Solid-State Circuits 49 (2014) 622.

- [4] Yan Lu, et al., IEEE Trans. Circuits Syst. II: Express Briefs 64 (2017) 116.